| CATEGORII DOCUMENTE |

Introducere

Scopul indrumarului este de a prezenta studentilor o structura minimala a unui microsistem realizat cu microprocesorul Z80. Microsistemul permite rularea programelor ciclu cu ciclu sau instructiune cu instructiune. In acest fel se poate urmari modul de executie a setului de instructiuni si efectul executiei instructiunilor asupra resurselor hard. Studentul este antrenat in perceptia instructiunilor scrise in cod masina prin urmarirea efectelor acestora.

In prima parte se prezinta structura microsistemului cu resursele hard aferente. Se pune in evidenta rolul dispozitivelor si circuitelor electronice utilizate.

In cea de-a doua parte se prezinta setul instructiunilor microprocesorului Z80 si modul de executie al acestor instructiuni.

Se are in vedere de asemenea si modul de tratare a intreruperilor mascabile si nemascabile.

Pentru a face trecerea de la rularea programelor in regim - pas cu pas catre regimul automat se prezinta un program cu ajutorul caruia se genereaza semnale dreptunghiulare de frecventa variabila.

Prin modul de prezentare a microsistemului se urmareste transferul unor cunostinte solide, care au la baza realitatea prin care se percep notiunile referitoare la modul de lucru a microprocesoarelor.

microprocesorul Z80

In cadrul laboratorului se prezinta structura unui microsistem realizat cu microprocesorul Z80 de 8 biti. Microsistemul contine urmatoarele dispozitive electronice:

Microprocesorul Z80 - circuitul nr. 1;

Amplificatoarele magistralei de adrese 2 74LS373 - circuitele nr. 2 si 3;

Amplificatoarele magistralei de date 2 8216 - circuitele nr. 4 si 5;

Memoria EPROM 2716 - circuitul nr. 7;

Memoria RAM static 2 2114 - circuitele nr. 8 si 9;

Amplificatorul magistralei de comenzi 74LS125 - circuitul nr. 6;

Decodorul de adrese 74LS138 - circuitul nr. 18;

Buffer-ele de intrare/iesire 2 74LS373 - circuitele nr. 10 si 11;

Circuitele pentru generarea CLK;

Circuitele pentru generarea starilor de WAIT.

Microsistemul permite rularea programelor in regim pas cu pas si afiseaza adresele, datele si comenzile; astfel se pune in evidenta modul de executie al instructiunilor si efectul acestora. In timpul executiei se poate urmari modul de activare a semnalelor de selectie a memoriilor si circuitelor de intrare/iesire.

In cadrul orelor de laborator se urmareste evidentierea functiilor dispozitivelor electronice si modul de transfer a informatiei intre resursele microsistemului.

Mnemonica |

Descrierea simbolica |

LD r,r |

r r |

|

LD r,n |

r n |

|

LD r,(HL) |

r (HL) |

|

LD r,(Ix+d) |

r (Ix+d) |

|

LD r,(Iy+d) |

r (Iy+d) |

|

LD (HL),r |

(HL) r |

|

LD (Ix+d), r |

(Ix+d) r |

|

LD (Iy+d),r |

(Iy+d) r |

|

LD (HL),n |

(HL) n |

|

LD (Ix+d),n |

(Ix+d) n |

|

LD (Iy+d),n |

(Iy+d) n |

|

LD A,(BC) |

A (BC) |

|

LD A,(DE) |

A (DE) |

|

LD A,(nn) |

A (nn) |

|

LD (BC),A |

(BC) A |

|

LD (DE),A |

(DE) A |

|

LD (nn),A |

(nn) A |

|

LD A,I |

A I |

|

LD A,R |

A R |

|

LD I,A |

I A |

|

LD R,A |

R A |

unde:

r,r' reprezinta oricare dintre registrele B, C, D, E, H, L, A;

n este un octet;

(DE), (HL), (BC) o locatie de memorie a carei adresa este furnizata de data din registrele (DE), (HL), (BC);

(Ix+d), (Iy+d) indica o adresa de memorie, iar d reprezinta deplasamentul.

Mnemonica |

Descrierea simbolica |

|

LD dd,nn |

dd nn |

|

LD IX,nn |

IX nn |

|

LD IY,nn |

IY nn |

|

LD HL,(nn) |

H (nn+1) L (nn) |

|

LD (nn),HL |

(nn+1) H (nn) L |

|

LD dd,(nn) |

ddH (nn+1) ddL (nn) |

|

LD (nn),dd |

(nn+1) ddH (nn) ddL |

|

LD SP,HL |

SP HL |

|

LD SP,IX |

SP IX |

|

LD SP,IY |

SP IY |

|

PUSH qq |

(SP-2) qqL (SP-1) qqH SP SP-2 |

|

POP qq |

qqH (SP+1) qqL (SP) SP SP+2 |

|

PUSH IX |

(SP-2) IXL (SP-1) IXH SP SP-2 |

|

PUSH IY |

(SP-2) IYL (SP-1) IYH SP SP-2 |

|

POP IX |

IXH (SP+1) IXL (SP) SP SP+2 |

|

POP IY |

IYH (SP+1) IYL (SP) SP SP+2 |

|

EX DE,HL |

DE HL |

|

EX AF,AF' |

AF AF |

|

EXX |

BC BC DE DE HL HL' |

|

EX (SP),HL |

H (SP+1) L (SP) |

|

LDI |

(DE) (HL) DE DE+1 HL HL+1 BC BC-1 |

|

LDIR |

(DE) (HL) DE DE+1 HL HL+1 BC BC-1 Se repeta pana cand BC=0 |

|

LDD |

(DE) (HL) DE DE-1 HL HL-1 BC BC-1 |

|

LDDR |

(DE) (HL) DE DE-1 HL HL-1 BC BC-1 Se repeta pana cand BC=0 |

|

CPI |

A-(HL) HL HL+1 BC BC-1 |

|

CPIR |

A-(HL) HL HL+1 BC BC-1 Se repeta pana BC=0 sau A=(HL) |

|

CPD |

A-(HL) HL HL-1 BC BC-1 |

|

CPDR |

A-(HL) HL HL-1 BC BC-1 Se repeta pana BC=0 sau A=(HL) |

unde: nn - reprezinta un numar format din doi octeti;

(nn) - reprezinta octetul de memorie de la adresa nn.

dd: 00, 01, 10, 11.

registre: BC, DE, HL, SP.

00 BC 01 DE 10 HL 11 SP

Mnemonica |

Descrierea simbolica |

|

IN A,(n) |

A (n) |

|

IN r,(c) |

r (c) |

|

INI |

(HL) (c) B B-1 HL HL+1 |

|

INIR |

(HL) (c) B B-1 HL HL+1 Se repeta pana cand B=0 |

|

IND |

(HL) (c) B B-1 HL HL-1 |

INDR |

(HL) (c) B B-1 HL HL-1 Se repeta pana cand B=0 |

|

OUT (n),A |

(n) A |

|

OUT (c),r |

(c) r |

|

OUTI |

(c) (HL) B B-1 HL HL+1 |

|

OTIR |

(a) (HL) B B-1HL HL+1 Se repeta pana cand B=0 |

|

OUTD |

(c) (HL) B B-1 HL HL-1 |

|

OTDR |

(c) (HL) B B-1 HL HL-1 Se repeta pana cand B=0 |

Observatie: In cazul instructiunilor IN A,(n) si OUT (n),A, pe magistrala de adrese, in timpul executiei instructiunii se afla:

A0-A7 n si A8-A15 A

In toate celelalte cazuri, in timpul executiei instructiunilor de intrare/iesire, pe magistrala de adrese se afla informatia:

A0-A7 C A8-A15 B

Instructiuni de salt si apel de subrutina, reveniri

|

Mnemonica |

Descrierea simbolica |

|

JP nn |

PC nn |

|

JP cc, nn |

Daca cc adevarata PC nn, altfel continua |

|

JR e |

PC PC+e |

|

JR c, e |

c=0-continua, c=1-PC PC+e |

|

JR Nc, e |

c=1-continua, c=0-PC PC+e |

|

JR z, e |

z=0-continua, z=1-PC PC+e |

|

JR Nz, e |

z=1-continua, z=0-PC PC+e |

|

JP (HL) |

PC (HL) |

|

CALL nn |

(SP-1) PCH (SP-2) PCL SP SP-2 PC nn |

|

CALL cc, nn |

cc=0-continua, cc=1-CALL nn |

|

RET |

PCL (SP) PCH (SP+1) SP SP+2 |

|

RET cc |

cc=0-continua, cc=1-RET |

|

RETN |

Revenire din intrerupere nemascabila |

|

RETI |

Revenire din intrerupere |

|

RST p |

(SP-1) PCH (SP-2) PCL PCH PCL p Este echivalent cu CALL p |

unde: ![]()

![]() cc conditia:

cc conditia:

000 NZ non-zero

Z zero

010 NC non-carry

c carry

100 PO impar

101 PE par

P pozitiv

M negativ

Variabila p poate lua una din valorile 00h, 08h, 10h, 18h, 20h, 28h, 30h, 38h, iar e reprezinta un numar scris in complement fata de 2 cuprins intre -126 si 128.

Instructiuni aritmetice si logice

|

Mnemonica |

Descrierea simbolica |

|

ADD A, r |

A A+r |

|

ADD A, n |

A A+n |

|

ADD A, (HL) |

A A+(HL) |

|

ADD A, (Ix+d) |

A A+(Ix+d) |

|

ADD A, (Iy+d) |

A A+(Iy+d) |

|

ADD A, S |

A A+S+CY |

|

SUB S |

A A-S |

|

SBC A, S |

A A-S-CY |

|

AND S |

A A S |

|

OR S |

A A S |

|

XOR S |

A A S |

|

CP S |

A-S |

|

INC r |

r r+1 |

|

INC (HL) |

(HL) (HL)+1 |

|

INC (Ix+d) |

(Ix+d) (Ix+d)+1 |

|

INC (Iy+d) |

(Iy+d) (Iy+d)+1 |

|

DEC m |

m m-1 |

|

ADD HL, ss |

HL HL+ss |

|

ADC HL, ss |

HL HL+ss+CY |

|

SBC HL, ss |

HL HL-ss-CY |

|

ADD Ix, pp |

Ix Ix+pp |

|

ADD Iy, rr |

Iy Iy+rr |

|

INC ss |

ss ss+1 |

|

INC Ix |

Ix Ix+1 |

|

INC Iy |

Iy Iy+1 |

|

DEC ss |

ss ss-1 |

|

DEC Ix |

Ix Ix-1 |

|

DEC Iy |

Iy Iy-1 |

Variabilele r, s, m, ss, pp, rr au urmatoarea semnificatie: s - poate fi r, n, (HL), (Ix+d), (Iy+d),

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() r Registre

ss Registre pp Registre rr Registre

r Registre

ss Registre pp Registre rr Registre

000 B 00 BC 00 BC 00 BC

001 C 01 DE 01 DE 01 BE

010 D 10 HL 10 Ix 10 Iy

011 E 11 SP 11 SP 11 SP

100 H

101 L

A

Instructiuni de comanda si control, rotatii si deplasari,

prelucrari pe bit

|

Mnemonica |

Descrierea simbolica |

|

CPL |

|

|

NEG |

A 0-A |

|

CCF |

CY CY |

|

SCF |

CY |

|

NOP |

nici o operatie |

|

HALT |

oprirea UC - Z80 |

|

DI |

dezactivare sistem intrerupere/IFF 1, 2 |

|

EI |

activare sistem intrerupere/IFF 1, 2 |

|

IM 0 |

stabilire mod intrerupere 0 |

|

IM 1 |

stabilire mod intrerupere 1 |

|

|

stabilire mod intrerupere 2 |

|

| |

|

| |

|

RRCA | |

|

| |

|

BIT b, |

Z |

|

BIT b, |

|

|

BIT b, |

Z |

|

BIT b, |

Z |

- b reprezinta bitul testat al registrului r sau al locatiei de memorie adresata de (HL), (IX+d), (IY+d).

![]()

![]()

0

1

2

3

4

5

6

7

In cadrul acestui laborator se prezinta modul de executie a unei intreruperi mascabile, a unei intreruperi nemascabile respectiv modul de tratare a unei cereri de magistrala.

Se descrie intreruperea mascabila si se urmareste cum se trateaza o intrerupere in modul 1. Se pune in evidenta faptul ca intreruperea mascabila este preluata si tratata la sfarsitul instructiunii curente.

Se descrie intreruperea nemascabila si se urmareste modul de tratare si felul cum se revine din intrerupere. Se pune in evidenta faptul ca intreruperea NMI este preluata in orice moment si se trateaza la sfarsitul instructiunii curente.

Se desfasoara experimentul prin care se pune in evidenta modul de preluare si cedare a magistralei sistemului. Se observa faptul ca magistralele sistemului sunt trecute in S.I.R. si se pot accesa resursele microsistemului.

Lucrari de laborator:

Lucrarea 1:

Folosinduse simulatorul de Z80 aflat pe fiecare calculator din laborator sa se ruleze pas cu pas urmatorul program realizat in limbaj de asmblare urmarindu-se cu atentie modul de executie:

|

Fisierul Prog . asm |

Fisierul Prog . lst |

Fisierul Prog . obj |

|

; Ex. de pr. in asamblare Z80 ; Se seteaza ; indicatorul de stiva LD SP,0020H JP ST ; Se stabileste adresa unde ; se plaseaza codul programului ORG 0020H ST: JP LP1 ; Se definesc datele de intrare LD1: .DB 04H .DB 03H .DB 02H ; Se defineste spatiul destinatie SD1: .DB 00H .DB 00H .DB 00H ; Se seteaza constanta CT1 CT1 .EQU 14H LP1: LD BC,LD1 LD HL,SD1 LD D,03H; LP2: CALL R1 DEC D JP NZ,LP2 HALT ; Rutina care aduna la data ; din memorie de la adresa (BC) ; contanta CT1si o depune ; la adresa de memorie (HL) R1: LD A,(BC) ADD A,CT1 LD (HL),A INC BC INC HL RET .END |

0000 ; Ex. de pr. in asamblare Z80 0000 ; Se seteaza indicatorul de stiva LD SP, 0020H C3 20 00 JP ST 0006 ; Se stabileste adresa unde 0006 ; se plaseaza codul programului 0007 0020 .ORG 0020H C3 29 00 ST: JP LP 0023 ; Se definesc datele de intrare LD1: .DB 04H .DB 03H .DB 02H 0026 ; Se defineste spatiul destinatie SD1: .DB 00H .DB 00H .DB 00H 0029 ; Se seteaza constanta CT1 0018 0029 CT1 .EQU 14H LP1: LD BC,LD1 0020 002C LD HL,SD1 0021 002F LD D,03H; CD 39 00 LP2: CALL R1 DEC D C2 31 00 JP NZ,LP2 HALT 0039 ; Rutina care aduna la data 0039 ; din memorie de la adresa (BC) 0039 ; contanta CT1si o depune 0039 ; la adresa de memorie (HL) 0A R1: LD A,(BC) 0031 003A C6 14 ADD A,CT1 0032 003C LD (HL),A 0033 003D INC BC 0034 003E INC HL 0035 003F C9 RET 0036 0040 .END |

0003 C3 20 00 000A 00 000B 00 000C 00 000D 00 000E 00 000F 00 001A 00 001B 00 001C 00 001D 00 001E 00 001F 00 0020 C3 29 00002C 21 26 00 002F 16 03 0031 CD 39 00 0035 C2 31 000039 0A 003A C6 14 003C 77 003D 03 003E 23 003F C9 |

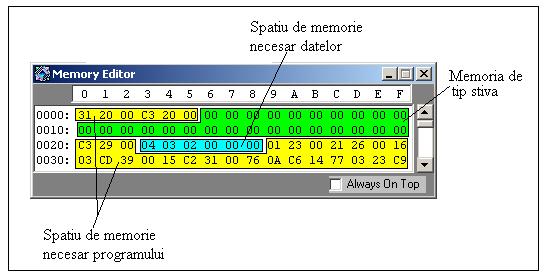

Spatiul de memorie necesar executiei programului, inaintea rularii acestuia

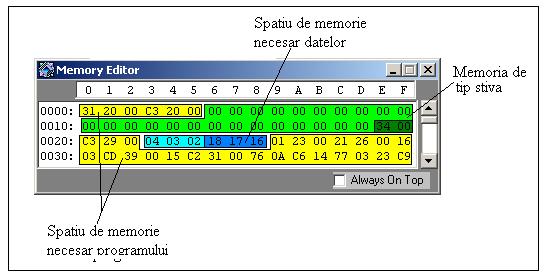

Spatiul de memorie necesar executiei programului, dupa rularea acestuia

Lucrara 2:

Sa se rezolve urmatoarele cerinte si apoi sa se ruleze fiecare program in parte cu ajutorul simulatorului Z80:

1. Sa se transfere in registrul B valoarea 80H si in C valoarea 10 prin intermediul unei instructiuni pe 16 biti.

2. Sa se incarce la locatia de memorie 8010H valoarea 05H.

3. Sa se incarce la adresa 8010H plus un deplasament de 10H valoarea FFH folosindu-se registrul index IX.

4. Sa se schimbe continutul locatiilor de memorie 8020H si 8010H.

5. Sa se schimbe continutul registrului D cu E dupa ce in prealabil au fost incarcate cu valorile 03H si EFH.

Lucrarea 3:

Sa se rezolve urmatoarele cerinte si apoi sa se ruleze fiecare program in parte cu ajutorul simulatorului Z80:

1. Sa se puna la adresele de memorie 7030H, 702FH,702EH,702DH,703CH valorile 55H, 54H, 53H, 52H, 51H folosind instructiunea LDDR.

2. Folosind instructiunea CPIR sa se repete ciclul doar de 4 ori stiind ca ca A=0E3H,

BC=0007H si HL=773DH.

Lucrarea 4:

Sa se rezolve urmatoarele cerinte si apoi sa se ruleze fiecare program in parte cu ajutorul simulatorului Z80:

1. Folosind instructiunea INDR sa se puna succesiv la locatiile de memorie 800DH,

800EH, 800FH, 8010H valorile D, E, F, 1. Adresa portului de intrare va fi 01H si se seteaza cu ajutorul registrului C.

2. Folosind instructiunea OTIR sa se trimita la portul de iesire de adresa 02H valorile

A, B, C stiind ca HL este 800AH.

Lucrarea 5:

Sa se rezolve urmatoarele cerinte si apoi sa se ruleze fiecare program in parte cu ajutorul simulatorului Z80:

1. Sa se adune intr-un registru acumulator valoarea citita de la portul de intrare cu adresa 00H atit timp cit este diferita de 0. Sa se afiseze continutul acumulatorului in final.

2. Sa se scada dintr-un registru ce are valoarea initiala 0 pe rind valorile citite de la portul de intrare 01H de 4 ori folosind instructiunea DNJZ. Rezultatele se vor afisa de fiecare dat la portul cu adresa 04H.

Lucrarea 6:

Sa se rezolve urmatoarele cerinte si apoi sa se ruleze fiecare program in parte cu ajutorul simulatorului Z80:

1. Sa se obtina valoarea B7H folosind instructiunea RLA.

2. Sa se obtina valoarea AEH folosind instructiunea RLCA.

3. Sa se obtina valoarea 92H folosind instructiunea RRCA.

4. Sa se obtina valoarea C5H folosind instructiunea RRA.

Lucrarea 7:

Folosind simulatorul Z80, sa se studieze cu atentie fiecare instructiune a programului de mai jos:

;Program pentru selectarea subprogramelor

LD SP,8400H

IN A,(00H)

CP 00H

JP Z,0100H

CP 01H

JP Z,0180H

CP 02H

JP Z,0200H

CP 03H

JP Z,0280H

CP 04H

JP Z,0300H

CP 05H

JP Z,0380H

CP 06H

JP Z,0400H

CP 07H

JP Z,0480H

CP 08H

JP Z,0500H

CP 09H

JP Z,0580H

HALT

;Subrutina pentru tratarea intreruperilor mascabile

.ORG 0038H

DI

PUSH BC

PUSH AF

IN A,(00H)

OUT (04H),A

POP AF

POP BC

EI

RETN

HALT

;Subrutina pentru tratarea intreruperilor nemascabile

.ORG 0066H

PUSH BC

PUSH AF

IN A,(00H)

OUT (04H),A

POP AF

POP BC

RETN

;Subprogram care ilustreaza modul de executie

;a instructiunilor de transfer pe 8 biti

.ORG 0100H

LD A,0FFH

LD HL,8010H

LD (HL),A

LD B,A

LD (HL),B

LD B,05H

LD HL,8020H

LD (HL),B

LD IX,8100H

LD IY,8200H

LD (IX+10H),C

LD (IY+20H),C

LD IX,8000H

LD D,(IX+10H)

LD IY,8000H

LD E,(IY+20H)

LD HL,8110H

LD A,(HL)

LD HL,8220H

LD A,(HL)

LD BC,8010H

LD (BC),A

PUSH BC

PUSH IX

LD BC,0000H

LD IX,0000H

POP IX

POP BC

LD (IX+01H),B

LD (IX+02H),C

LD A,01H

OUT (04H),A

HALT

;Subprogram care ilustreaza modul de

;executie a instructiunilor de transfer

;pe 16 biti, transfer de blocuri, cautari

.ORG 0180H

LD HL,8020H

LD DE,8080H

LD B,0F0H

LD C,0FH

LD (HL),B

LD A,C

LD (DE),A

EX DE,HL

LD A,(HL)

LD A,(DE)

LD A,55H

LD (HL),A

INC HL

LD (HL),A

INC HL

LD A,0FH

LD (HL),A

INC HL

LD (HL),A

LD BC,0004H

LDDR

LD DE,8030H

LD BC,0004H

LDIR

LD HL,8033H

LD DE,8010H

LD BC,0003H

LDDR

LD A,02H

OUT (04H),A

HALT

;Subprogram care ilustreaza modul de

;executie a instructiunilor de intrare/iesire

.ORG 200H

LD HL,8100H

IN A,(00H)

LD (HL),A

LD C,00H

IN D,(C)

INC HL

LD (HL),D

LD A,(HL)

OUT (04H),A

DEC HL

LD E,(HL)

LD C,04H

OUT (C),E

LD C,00H

LD B,04H

INIR

LD C,04H

LD B,03H

OTDR

LD A,03H

OUT (04H),A

HALT

;Subprogram care ilustreaza modul

;de executie a instructiunilor

;de salt si apel de subrutina, reveniri

.ORG 0300H

LD C,00H

JP 030EH

IN A,(C)

OUT (04H),A

CP 0FFH

JP Z,0305H

CALL 0324H

IN A,(C)

CP 0FFH

JP NZ,0305H

IN A,(C)

CP 0FFH

CALL Z,0324H

LD A,05H

OUT (04H),A

HALT

IN A,(C)

CP 0FFH

RET Z

LD A,55H

OUT (04H),A

RET

;Subprogram care ilustreaza modul

;de executie a instructiunilor

;aritmetice si logice

.ORG 280H

LD C,00H

IN B,(C)

IN A,(C)

ADD A,B

OUT (04H),A

IN D,(C)

IN A,(C)

SUB D

OUT (04H),A

IN E,(C)

IN A,(C)

OR E

OUT (04H),A

IN B,(C)

IN A,(C)

AND B

OUT (04H),A

IN A,(C)

CP 0FFH

PUSH AF

POP BC

LD A,C

OUT (04H),A

LD A,B

OUT (04H),A

LD A,04H

OUT (04H),A

HALT

;Subprogram prin care se pune

;in evidenta modul de executie

;a instructiunilor de comanda si control

;rotatii si deplasari, prelucrari pe bit

.ORG 380H

EI

IM 1

LD C,04H

LD A,0FH

RLCA

OUT (C),A

RRCA

OUT (C),A

SCF

RLA

OUT (C),A

CCF

RRA

OUT (C),A

DI

LD A,0FH

OUT (C),A

CPL

OUT (C),A

NOP

LD A,0F0H

BIT 7,A

JP NZ,03ACH

LD A,0FH

BIT 5,A

JP Z,03ADH

NOP

NOP

LD A,06H

OUT (04H),A

HALT

;Program pentru generarea semnalelor

;dreptunghiulare de frecventa variabila

.ORG 400H

EI

IM 1

LD C,00H

LD A,55H

OUT (04H),A

IN B,(C)

CALL 041AH

LD A,0AAH

OUT (04H),A

IN B,(C)

CALL 041AH

JP 0405H

;Rutina de temporizare

LD D,04H

DEC D

JP NZ,041CH

DEC B

JP NZ,041AH

RET

Lucrarea 8:

Programul prezentat in continuare efectueaza inmultirea a dou numere intregi cu semn. Sa se studieze cu atentie modul de realizare a lui.

; Program care realizeaza inmultirea

; a doua numere intregi reprezentate pe un octet

; Numerele apartin intervalului [-128 127]

; Se seteaza indicatorul de stiva

LD SP,0020H

JP ST

; Se stabileste adresa unde

; se plaseaza codul programului

.ORG 0100H

ST: JP LP1

; Se definesc datele de intrare

; Cele doua numere sunt date mai jos

LD1: .DB 0F8H

;LD2: .DB 0F1H

LD2: .DB 0H

S1: .DB 0H

S2: .DB 0H

SR: .DB 0H

; Se defineste spatiul destinatie unde

; se plaseaza rezultatul

SD1: .DB 00H

.DB 00H

; Programul care realizeaza inmultirea celor doua numere

LP1: LD HL,00H

; Se citeste primul factor

LD DE,LD1

LD A,(DE)

BIT 7,A

JP Z,AP1

; Se complementeaza in raport cu doi

CPL

ADD A,01

; Se seteaza semnul la adresa S1:

PUSH HL

LD HL,S1

LD (HL),01H

POP HL

; Se compara primul factor cu zero

AP1: CP 00H

JP Z,LP3

LD C,A

LD B,00H

; Se citeste cel de-al doilea factor

LD DE,LD2

LD A,(DE)

BIT 7,A

JP Z,AP2

; Se complementeaza in raport cu doi

CPL

ADD A,01

; Se seteaza semnul la adresa S2:

PUSH HL

LD HL,S2

LD (HL),01H

POP HL

; Se compara al doilea factor cu zero

AP2: CP 00H

JP Z,LP3

; Se compara factorii cu 80H

LD E,A

CP 80H

JP Z,AP3

LD A,C

CP 80H

JP Z,LP2

LD A,E

CP C

; Se compara E cu C (E-C)

; si se schimba continutul acestor registre

; daca E este mai mare decat C

JP M,LP2

AP3: LD D,C

LD C,E

LD E,D

; Se realizeaza inmultirea prin adunari repetate

LP2: ADD HL,BC

DEC E

JP NZ,LP2

JP LP7

; Se trateaza cazul cand cel putin un factor este nul

LP3: LD DE,SR

LD A,03H

LD (DE),A

LP7: LD DE,SD1

LD A,H

LD (DE),A

INC DE

LD A,L

LD (DE),A

; Se trateaza semnul rezultatului

; Cazul cand cel putin un factor este nul

LD DE,SR

LD A,(DE)

CP 03

JP NZ,LP8

LD A,00

LD (DE),A

JP LP6

; Cazul cand factorii sunt nenuli

LP8: LD B,0H

LD DE,S1

LD A,(DE)

CP 00H

JP Z,LP4

INC B

LP4: LD DE,S2

LD A,(DE)

CP 00H

JP Z,LP5

INC B

LP5: LD A,B

CP 01H

JP NZ,LP6

LD A,01H

LD DE,SR

LD (DE),A

LP6: HALT

Lucrarea 9:

Intreruperile nemascabile si intreruperile mascabile de mod 0:

LD A,0AAh

LD I,A

LD SP,0010H

LD IX,0AA30h

LD (IX+00h),00h

LD (IX+01h),0EEh

JP ST1

.ORG 0066h

PUSH AF

LD A,0CCH

OUT (0AAH),A

POP AF

RETN

.ORG 0300H

ST1: EI

IM 0

ST2: LD A,0AAH

OUT (045H),A

LD A,0FH

T1: DEC A

JP NZ,T1

LD A,55H

OUT (045H),A

LD A,0FH

T2: DEC A

JP NZ,T2

JP ST2

.ORG 0038H

DI

PUSH AF

JP masc

.ORG 0500h

masc: IN A,(02H)

LD B,A

AND 80H

CP 80H

JP Z,adr1

ALFA1: LD A,B

AND 40H

CP 40H

JP Z,adr2

ALFA2: LD A,B

AND 20H

CP 20H

JP Z,adr3

ALFA3: LD A,B

AND 10H

CP 10H

JP Z,adr4

ALFA4: LD A,B

AND 08H

CP 08H

JP Z,adr5

ALFA5: LD A,B

AND 04H

CP 04H

JP Z,adr6

ALFA6: LD A,B

AND 02H

CP 02H

JP Z,adr7

ALFA7: LD A,B

AND 01H

CP 01H

JP Z,adr8

ALFA8: POP AF

EI

RET

.ORG 0700h

ADR1: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,31H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA1

ADR2: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,32H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA2

ADR3: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,33H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA3

ADR4: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,34H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA4

ADR5: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,35H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA5

ADR6: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,36H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA6

ADR7: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,37H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA7

ADR8: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,38H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA8

.ORG 0EE00h

PUSH AF

LD A,0CCH

OUT (0AAH),A

POP AF

RETI

.END

Lucrarea 10:

Intreruperile nemascabile si intreruperile mascabile de mod 1:

LD SP,0010H

JP ST1

.ORG 0010h

PUSH AF

LD A,0CCH

OUT (0AAH),A

POP AF

RETI

.ORG 0066h

PUSH AF

LD A,0CCH

OUT (0AAH),A

POP AF

RETN

.ORG 0300H

ST1: EI

IM 0

ST2: LD A,0AAH

OUT (045H),A

LD A,0FH

T1: DEC A

JP NZ,T1

LD A,55H

OUT (045H),A

LD A,0FH

T2: DEC A

JP NZ,T2

JP ST2

.END

Lucrarea 11:

Intreruperile nemascabile si intreruperile mascabile de mod 2:

LD A,0AAh

LD I,A

LD SP,0010H

LD IX,0AA30h

LD (IX+00h),00h

LD (IX+01h),0EEh

JP ST1

.ORG 0066h

PUSH AF

LD A,0CCH

OUT (0AAH),A

POP AF

RETN

.ORG 0300H

ST1: EI

IM 2

ST2: LD A,0AAH

OUT (045H),A

LD A,0FH

T1: DEC A

JP NZ,T1

LD A,55H

OUT (045H),A

LD A,0FH

T2: DEC A

JP NZ,T2

JP ST2

.ORG 0038H

DI

PUSH AF

JP masc

.ORG 0500h

masc: IN A,(02H)

LD B,A

AND 80H

CP 80H

JP Z,adr1

ALFA1: LD A,B

AND 40H

CP 40H

JP Z,adr2

ALFA2: LD A,B

AND 20H

CP 20H

JP Z,adr3

ALFA3: LD A,B

AND 10H

CP 10H

JP Z,adr4

ALFA4: LD A,B

AND 08H

CP 08H

JP Z,adr5

ALFA5: LD A,B

AND 04H

CP 04H

JP Z,adr6

ALFA6: LD A,B

AND 02H

CP 02H

JP Z,adr7

ALFA7: LD A,B

AND 01H

CP 01H

JP Z,adr8

ALFA8: POP AF

EI

RET

.ORG 0700h

ADR1: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,31H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA1

ADR2: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,32H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA2

ADR3: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,33H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA3

ADR4: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,34H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA4

ADR5: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,35H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA5

ADR6: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,36H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA6

ADR7: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,37H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA7

ADR8: PUSH BC

LD A,49H

OUT (44H),A

LD A,4EH

OUT (44H),A

LD A,54H

OUT (44H),A

LD A,20H

OUT (44H),A

LD A,38H

OUT (44H),A

LD A,20H

OUT (44H),A

POP BC

JP ALFA8

.ORG 0EE00h

PUSH AF

LD A,0CCH

OUT (0AAH),A

POP AF

RETI

.END

Lucrarea 12:

Probleme propuse:

1. Sa se realizeze un program care sumeaza fara semn continutul locatiilor de memorie cu adresele 40A0H si 40A1 si salveaza rezultatul la adresele 40B0H si 40B1.

Atentie: Sa se tina cont de faptul ca poate exista transport la bitul cel mai semnificativ care trebuie salvat in memoria RAM.

2. Sa se realizeze un program care initializeaza cu FFH adresele din memorie cuprinse intre 4080H si 408FH.

3. Sa se realizeze un program care initializeaza blocul de memorie cuprins in tre adresele 4100H si 411FH cu valorile 0, 1, 2, , 1FH.

4. Sa se modifice in mod corespunzator programul de la exerciciul 3 astfel incat initializarea sa se realices in ordine inversa () de la 4100H la 411FH cu valorile 1FH, 1EH, , 0.

5. Sa se faca programul care copiaza blocul de memorie cuprins intre adresele 0000H si 001FH. Copierea se va face in zona de memorie incepand de la adresa 41000H.

6. Sa se faca programul care gaseste maximul si minimul a 16 date de un byte aflate in memoria RAM incepand de la adresa 4050H. Maximul si minimul se vor salva la adresele 40A0H si respectiv 40B0H.

7. Sa se faca programul care sumeaza doua date de 8 biti aflate la adresele de memorie 5050H si respectiv 4060H si salveaza rezultatul incepand cu adresa 40A0H. Datorita faptului ca Z80 salveaza datele in memorie cu biti mai semnificativi la adrese mai mari, in cazul in care se produce transport final, acesta trebuie sa se salveze la adresa 40A8H, daca nu este transport, valoarea de la adresa respectiva trebuie pusa la zero.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1235

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2024 . All rights reserved