| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

CBB R-S simplu realizat in consructoe integrata

CBB-urile reprezinta circuite electronice care din punct de vedere o parametrilor electrici se caracterizeaza prin doua stari limite distincte. Trecerea dintr-o srate in alta sau (bascularea circuitului) are loc intr-un timp foarte scurt ce depinde de constantele de timp ale circuitului si apare ca o variatie brusca a marimilor de la cele doua iesiri ale circuitului. Acest proces de basculare se declanseaza fie sub actiunea unor semnale electice externela CBB si CBM fie ca urmare a proprietatilor circuitului de basculare spontan dintr-o stare in cealalta cum este cazu CBA.

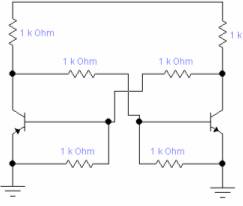

In tehnologia circuitelor integrate de tip secventia, circuitele basculante cele mai folosite sunt cele de tip bistabil si in unele cazuri monostabile realizate cu tranzistori integrati de tip npn cu siliciu. Se observa in schema ca daca T conduce, la aplicarea unui impuls pozitiv pe baza prin terminalul S (set- de punere, de inregistrare) va avea loc deschiderea tranzistorului T la saturatie. Ca urmare saltul negativ de tensiune de la colectorul sau se va transmite prin R la baza tranzistorului T ducand la blocarea tensiunii negative pe baza. Tranzistorul T mentinand-o pozitiva pana cand semnalul pe intrarea S devine 0, in absenta altor semnale de intrare anterioare, circuitul va ramane in aceasta stare un timp nedefinit. De aici rezulta ca CBB poate indeplinii functia de memorie avand iesirea Q in starea 1 logic, iar Q in 0 logic, tensiunea practic nula in colectorul lui T , care este in conductie la saturatie.

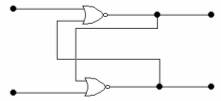

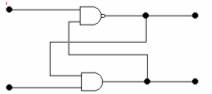

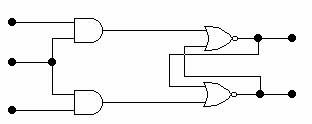

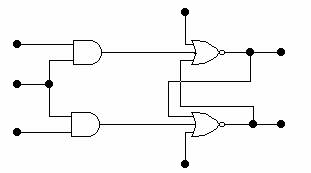

CBB de tip R-S poate fi considerat ca fiind format din doua porti NOR sau doua porti NAND (SI-NU) cuplate intersectat dupa urmatoarea achema.

Operatiile logice pe care poate executa un astfel de bistabil pot fi exprimate prin urmatoarele relatii :

Q = S + QR

Q = R + QS

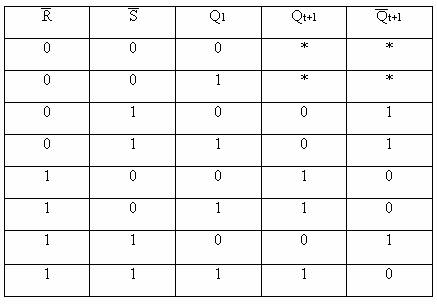

Tabelul cu stari de functionare.

|

R |

S |

Q |

Q |

|

X |

X |

La analiza functionarii bistabilului R-S trebuie sa se tina seama de faptul ca in momentul aplicarii semnalului, CBB poate sa se afle intr-unul din cele doua stari deci trebuie sa se ia in considerare toate combinatiile posibile pentru iesirea activa Qt-1 in functie de starile Qt existente in momentul aplicarii comenzilor.

Qt-1 = S + RQ

Qt-1 = R + SQ

R ∙ S = 0 Se poate determina cu ajutorul diagramelor VK aceste ecuatii.

Dupa cele doua ecuatii vor rezulta urmatoarele pentru bistabilii cu porti NOR.

A aplicarea semnalului 0 la ambele intrari nu modifica starea bistabililor

B aplicarea semnalului S=1 simultan cu R= 0 determina Q01 independend de starea bistabilului inainte de aplicarea comenzii. Aceasta trecere a bistabilului in starea Q01 se numeste pozitionare (SET).

C la aplicarea semnalului R=1 simultan cu S=0 determina Q=0 operatia care numeste stergere (RESET) sau punere pe 0 pentru iesirea Q.

D la aplicarea simultana a semnalului 1 la intrarile S si R genereaza o stare nedeterminata de aceea comanda R=S=1 cea ce este interzisa. Acest lucru este descris de conditia logica RS=0 , adica R si S nu pot fi simultan 1.

Infunctie de starile le monentul T(Q ) existente aplicarii comenzilor la care tabelul de adevar este:

A

|

R |

S |

Qt |

Qt+1 |

De regula in cazul circuitului de tip NAND comutara se face prin 0 logic, adica pe front negativ, alicandu-se semnale R si respectiv S la intrarile bistabilului. Ca urmare pentru a memora un bit adica Q = 1, se va aplica la intrari semnalele S = 0 si R = 1, si invers pantru a obtine 0, ce va rezulta din tabelul b de adevar de unde se vede ca de data asta este interzisa pentru comenzile R = 0 si respectiv S = 0 aplicate simultan, deci se va impune conditia R∙ S = 1

Pentru obtinerea ecuatiilor logice

ale iesirilor se apleleaza la minimizarea functiilor logice si respectiv ![]() folosite tot cu

tabelul V - K.

folosite tot cu

tabelul V - K.

![]()

Circuitele bistebile R-S sunt circuite asincrone, acestea inseamna ca intrarile S si R sunt considerate intrari de comenzi asincrone deoarece iesirea se modifica dupa ce se modifica oricare din intrari ( prin aplicarea semnalelor ). In practica cel mai mult sunt folosite circuitele basculante bistabile sincrone la care exista o intrare suplimentara de tact ( CLK ) care face ca circuitul sa poata functiona simultan ( sincron ) cu toate celelalte dispozitive din sistem.

Circuitul basculant bistabil ( CBB ) de tip R-S cu porti NORpoate fi transformat intr-un CBB sincron prin adaugarea unor porti si suplimentar actionate de cate o intrare cu impulsul de sincronizare ( de tact ) CLK, dat de un generator special ( clock- ceas ).

In figura a) atat timp cat intrarea CLK nu

este activata ( se afla in starea 0 logic ) iesirile portilor Si suntin 0 logic

independent de valorile semnalelor aplicate la intrarile S ti R si ca urmare,

starea CBB nu poate fi modificata. Daca intrarea CLK se afla la nivel 1 logic,

atunci la aplicarea semnalelor

Se vede ca pe langa functia de sincronizare ( comanda sincrona), impulsul de tact joaca in acest caz si rolul de conditie suplimentara sau de fereastra pentru intrarile de date cat timp fereastra este inchisa (CLK= 0), datele de la intrari nu sunt transmise in bistabil, cand CLK = 1 (fereastra deschisa) datele sunt transmise in bistabil si apar la iesirile acestuia. In aceasta situatie se spune ca CBB simplu ( latch R-S simplu) comuta pe palier, adica pe durata palierului tactului.

Astfel durata semnalului de tact CLK delimiteaza intervalul in care R-S pot modifica starea bistabilului intru-cat acesta comuta pe palier. In unele situatii este necesar ca bistabilul sa comute in afara palierului al tactului, fie pe frontul pozitiv, fie pe frontul negativ cum este cayul bistabilelor D cu latch simplu.

In majoritatea aplicatiilor practice circuitele basculante bistabile (nu numai cele de tip R-S) mai sunt inzestrate cu inca doua intrari intrari de comanda PRESET si respectiv CLEAR (RESET) pentru punerea directa a CBB in pozitia SET si respectiv CLEAR (stergere) a acestuia inainte sau in afara aplicarii semnalelor CLK si respectiv R si S.

Acestea sunt reprezentate in figura a) de mai jos.

PRESET

CLEAR (RESET)

Prin urmare aceste semnale se utilizeaza cand nu se aplica tactul (CLK = 0) deci sunt intrari asincrone, de tip prioritar , le fiind folosite le inceputul functionarii schemei, cand trebuie resetat ansamblul de bistabili (CLEAR) sau pusi intr-o anumita stare de initializare a fiecarui bistabil conform cerintelorproblemei dare (PRESET).

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1322

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2024 . All rights reserved