| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

CIRCUITE LOGICE SECVENTIALE ( CLS )

GENERALITATI

CLS este un echipament (iar in cazul cel mai simplu un circuit integrat) cu mai multe intrari si iesiri; in cazul cel mai frecvent, una dintre intrari se numeste intrare de tact. Vectorul iesirilor depinde nu numai de valoare momentana a vectorului intrarilor ci si de starea in care se afla circuitul, respectiv de succesiunea starilor prin care a trecut acest circuit. Pentru cunoasterea starii in care se afla CLS, acestea se memoreaza folosind unul sau mai multe circuite basculante bistabile (CBB). Starea CLS este caracterizata prin variabilele de stare.

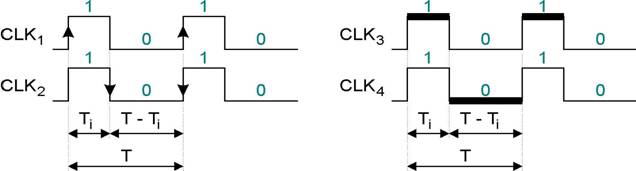

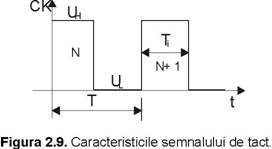

Modificarea starii CLS are loc in momente sau intervale de timp determinate de un semnal de tact (ceas, clock, CLK, CK). Un semnal de tact este format din impulsuri dreptunghiulare cu perioada de repetitie constanta.

CLS isi pot modifica starea pe front sau palier. Semnalul de tact se considera: -activ pe "1" daca modificarea starii CLS se face pe frontul crescator al impulsului de tact sau pe intreaga durata a acestuia. -activ pe "0" atunci cand modificarea starii circuitului se face pe frontul scazator al impulsului sau pe durata pauzei dintre doua impulsuri de tact. Semnalul de tact din figura 2.1 este activ pe front, Ti este durata impulsului de tact iar T este perioada semnalului.

Cel mai simplu CLS este circuitul basculant bistabil CBB. Starea acestuia este caracterizata printr-o variabila de stare notata Q.

CIRCUITE BASCULANTE BISTABILE (CBB)

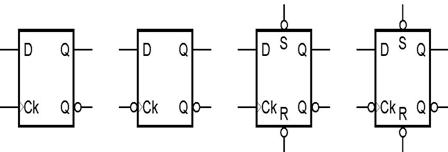

Daca un bistabil are prevazuta o intrare de tact il vom numi in continuare bistabil secvential sau sincron, sau pe scurt bistabil, iar daca nu are o asemenea intrare va fi denumit bistabil asincron, nesecvential sau latch. Exista si se folosesc urmatoarele tipuri de bistabile si latch-uri: SR, D, JK si T. In tehnologie TTL se fabrica urmatoarele tipuri de latch-uri: 74LS256, 74LS259, 74LS373, 74LS375, 74LS75, iar CMOS: 4042, 4043, 4044, 4508. In tehnologie TTL se fabrica urmatoarele tipuri de bistabile: 74107, 74109, 74112, 74173, 74174, 74175, 74273, 74374, 74377, 74378, 7473, 7476, , iar CMOS: 4013, 4027, 4076.

1. Circuite basculante bistabile de tip S-R

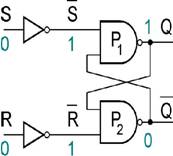

1.1. Latch-ul S-R ( Set-Reset ) cu porti SI-NU

Este cel mai simplu CLS si CBB, utilizat pentru memorarea unui bit de informatie (figura 2). Este alcatuit din doua porti SI-NU care formeaza un latch /R-/S si eventual doua inversoare care formeaza circuitul de intrare pentru intrari active SUS.

Pentru latch, S si R sunt variabile de intrare, iar Q este variabila de stare.

Circuitul din dreapta

cuprinde doua porti incluse intr-o bucla de reactie pozitiva. Presupunand ca P1si

P2functioneaza ca inversoare, bucla de reactie este activa doar atunci cand cele doua porti

functioneaza simultan in zona de tranzitie a caracteristicii de transfer. In

aceasta zona

Circuitul din dreapta

cuprinde doua porti incluse intr-o bucla de reactie pozitiva. Presupunand ca P1si

P2functioneaza ca inversoare, bucla de reactie este activa doar atunci cand cele doua porti

functioneaza simultan in zona de tranzitie a caracteristicii de transfer. In

aceasta zona

amplificarea in valoare absoluta este:

dui

du

du i >>1 Portile P si P efectueaza o amplificare numai in zona de tranzitie. In

UL

celelalte zone amplificarea este nula, bucla de reactie nu este activa si ansamblul

format din P si P este intr-o stare stabila.

Modificarea starii Q a unui latch SR se realizeaza prin modificarea variabilelor de intrare S si R. Daca

presupunem ca initial Q si S = R = 0 Q = 0 , iar aceasta stare se mentine un timp nedefinit. Similar,

daca presupunem ca pentru S=R=0 si initial Q

= 0 Q = 1. Combinatia S = 1 si R = 0 determina

Q = 1 (setarea latch-ului),iarcombinatiaS =0siR=1determinaQ=0(stergerea

latch-ului).

Functionarea este reflectata de un tabel de functionare, care prezinta care va

fi valoarea noua valoare a lui Q, notata Q* in functie

de vechea valoare Q si valorile logice ale variabilelor de intrare S si

R.

Combinatia S = R =1 este interzisa deoarece determina

aparitia egalitatii tensiunilor la iesire Q = nQ = 1, iar dupa inlaturarea

acestei combinatii si trecerea de exemplu la intrare la valorile S = R

= 0, iesirile se vor gasi intr-o stare nedeterminata, influentata de

procesul tehnologic, diferentele dintre P si P , etc.

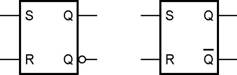

Figura Latch-ul SR, reprezentare simbolica.

|

S |

R |

Q |

Explicatie |

|

Q |

nici o modificare |

||

|

Q sters |

|||

|

Q setat |

|||

|

combinatie interzisa |

Q = nQ = 1 si apoi Q aleator |

Tabelul 1.

Functionarea latch-ului RS

![]()

La reprezentarea tuturor CBB este important de respectat urmatoarea regula: notand iesirea Q cu un

cerculet, in interiorul bistabilului se trece doar Q, in nici un caz tot Q

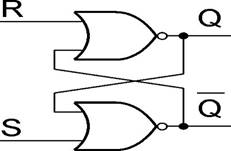

1.2. Latch-ul S-R cu porti SAU-NU

Latch-ul S-R poate fi realizate si cu porti

SAU-NU. Trebuie remarcat ca in acest caz semnalele S si R sunt

active SUS, iar pentru poarta cu iesirea Q intrarea corespunzatoare este R si

nu S sau nS, asa cum se intampla la latch-ul SR.

Latch-ul S-R poate fi realizate si cu porti

SAU-NU. Trebuie remarcat ca in acest caz semnalele S si R sunt

active SUS, iar pentru poarta cu iesirea Q intrarea corespunzatoare este R si

nu S sau nS, asa cum se intampla la latch-ul SR.

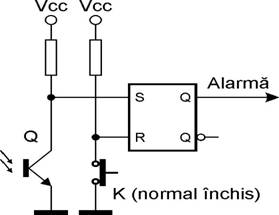

1.3. Aplicatie: circuit simplu de alarma cu latch S-R

Descrierea functionarii

Initial se sterge latch-ul, apasand K. In functionare normala, fototranzistorul Q este permanent luminat, astfel incat S = 0, K este inchis deci R = 0 iar Alarma = 0. La intreruperea razelor de lumina, rezistenta fototranzistorului este foarte mare, S devine 1 iar Alarma este 1. Indiferent de restabilirea caii razelor luminoase, alarma va fi actionata pana la o apasare a lui K.

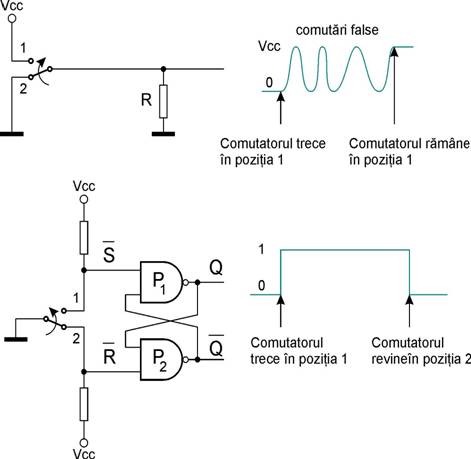

1. Aplicatie: eliminarea comutarilor false cu latch-ul S-R

Descrierea functionarii

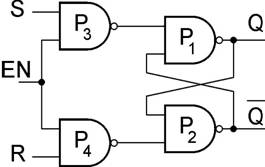

1.5. Latch-ul S-R cu intrare de comanda

Are o intrare suplimentara de comanda (sau validare), care poate fi privita atat ca intrare de tact (CK), cat si ca intrare de validare (EN). Latch-ul S-R cu intrare de comanda EN poate fi utilizat si in aplicatii nesecventiale, in acest caz la intrarea de comanda EN se aplica niveluri logice neperiodice.

In cazul functionarii secventiale, modificarea starii latch-ului se poate face pe toata durata Tia impulsului de comanda. Daca datele de intrare sunt modificate pe intervalul Ti, aceste modificari se reflecta imediat in valorile lui Q si Q ca in cazul unui latch SR obisnuit. Modificarea lui S si R se poate face si in intervalul dintre cele doua impulsuri succesive, cand aceste modificari nu se transmit la iesirile Q si Q , deoarece EN = 0 face ca iesirile portilor P si P sa fie pe "1" indiferent de faptul ca R sau S se modifica. Starea variabilelor de intrare si iesire inainte de aplicarea impulsului n + 1 de tact se noteaza cu Sn , Rn si Qn, iar dupa aplicarea impulsului n + 1 de tact se noteaza cu Sn+1, Rn+1 si Qn+1 . Nici acest latch nu poate fi folosit in aplicatii in care poate apare combinatia S = R = 1

Tabelul 2.

Tabel de functionare pentru latch-ul SR, cazul EN = 1

|

nS |

nR |

n Q |

Comentarii |

|

nQ |

nici o modificare |

||

|

Q sters |

|||

|

Q setat |

|||

|

combinatie interzisa |

conduce la 1== QQ |

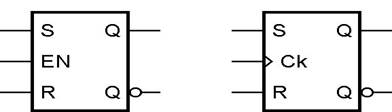

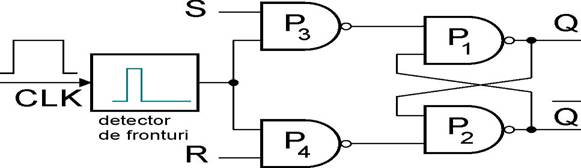

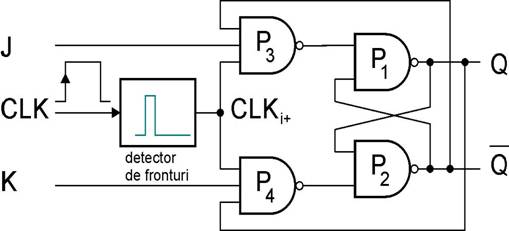

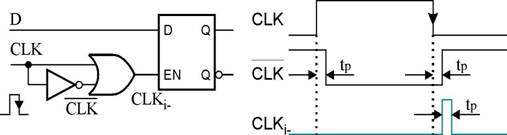

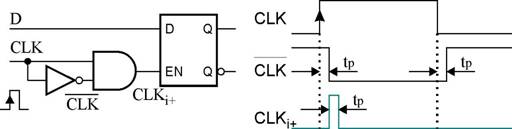

1.6. Metode de generare a semnalului de tact activ pe front

Datorita performantelor dinamice superioare si a comoditatii utilizarii, in sistemele sincrone moderne se folosesc cu precadere bistabile actionate pe front. Acest tip de comutare foloseste doua scheme simple de detectoare de fronturi, una pentru fontul crescator si alta pentru frontul descrescator. Desi impulsul generat are o latime mica, tipic de durata egala cu timpul de propagare, impulsurile generate intern CLKi+ si CLKisunt suficiente pentru a declansa circuitele comandate.

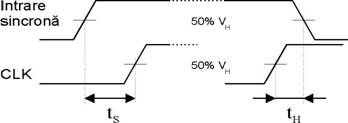

1.7. Particularitati dinamice cu privire la utilizarea bistabilelor comutate pe front

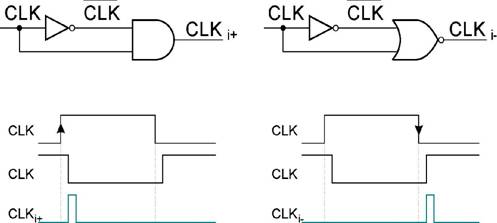

Pentru functionarea corecta a bistabilelor D si JK comutate pe front este necesara respectarea a doua intervale de timp care se numesc:

-timpul de (pre)stabilire (setup time)-tsu

-timpul de mentinere (hold time)-th

tsu -este intervalul (durata minima) dintre momentul atingerii unei valori stabile a nivelului logic la intrarea de date si momentul aplicarii frontului activ al impulsului de tact.

th -reprezinta durata minima in care valoarea stabila a nivelului aplicat la intrarea de date trebuie mentinuta dupa aparitia frontului activ a impulsului de tact.

![]()

Pentru circuitele TTL uzuale, timpul de stabilire este cuprins intre 5 si 50 ns, iar timpul de mentinere intre 0 si 10 ns. Daca nu se respecta acesti timpi, functionarea bistabilului este imprevizibila dupa aplicarea frontului activ al impulsului de tact (pot apare oscilatii, comportari metastabile sau in caz fericit o stare stabila nedeterminata).

1.8. Bistabilul SR comandat pe front

Descrierea functionarii Deoarece semnalul intern de tact CLKi+ este activ cateva nanosecunde, modificarea nivelului logic la S sau R poate afecta iesirea Q doar scurt timp inainte si dupa de frontul crescator al semnalului de tact CLK - aceasta comportare determina comanda pe front a bistabilului. Simbolul acestui bistabil este dat in figura 10 - dreapta.

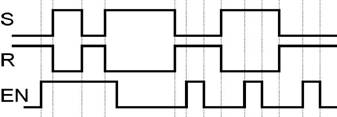

1.9. Tema

Pentru secventa de impulsuri prezentata mai jos, se cere sa se deseneze variatia iesirii Q pentru un latch SR.

Pentru aceeasi secventa de impulsuri, se inlocuieste EN cu CLK -se cere sa se deseneze variatia iesirii Q pentru un bistabil SR.

Explicati diferenta dintre comportari.

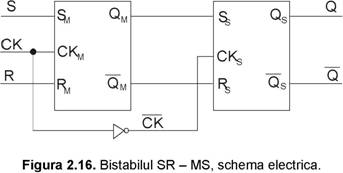

1.10. Bistabilul SR Master Slave

Acest tip de bistabil nu elimina nedeterminarea pentru Sn = Rn = 1 asa cum se intampla in cazul bistabilului JK-MS. Structura sa este inspirata din cea a bistabilului JK MS, cu deosebirea ca nu exista doua bucle de reactie globala de la cele doua iesiri Q si /Q la intrare. Pentru realizarea acestui bistabil se pot folosi doua latch-uri SR cu intrare de comanda (figura 7). Acest bistabil isi comuta iesirile pe frontul scazator al impulsului de tact.

La aplicarea tactului, primul

bistabil functioneaza dupa tabelul 2, iesirile Q ,Q![]() M se pozitioneaza

M se pozitioneaza

M

dupa valorile din tabel. Informatia inmagazinata la inceputul semnalului de tact si pe durata lui nu e

transmisa bistabilului S deoarece CK este pe intervalul Tisi bistabilul al II-lea Slave este zavorat.

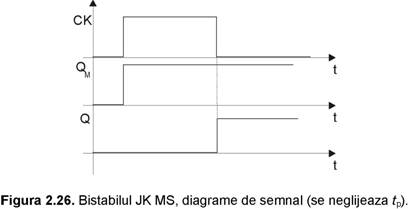

Figura 17, 18. Diagrame de semnal si reprezentare simbolica.

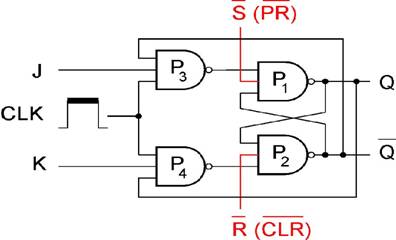

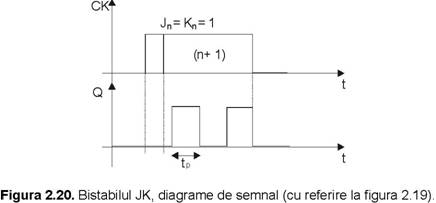

2. Circuite basculante bistabile de tip JK

2.1. Bistabilul JK cu intrare de tact si restrictie temporala

In continuare vom analiza o topologie pentru bistabilul JK derivata din cea a latch-ului RS si obtinuta prin adaugarea unei bucle de reactie de la iesiri la intrari, dar restrictionata sever temporal pentru o functionare corecta (durata impulsului de tact trebuie sa fie mai mica decat timpul de propagare prin bistabil:

Ti < tp = 2t pSI −NU

Principalele deosebiri fata de latch-ul RS:

-intrarile de date se noteaza cu J si K, litere fara o anumita

semnificatie, dar adiacente in alfabet.

-starea iesirilor portilor P3si P4depinde

nu numai de intrarile de date ci si de starea latch-ului

S − R ,

circuitul fiind prevazut cu o reactie globala de la iesiri la cele doua porti

din circuitul de intrare. -Sunt prevazute si doua intrari asincrone prioritare

pentru stabilirea starii initiale /PR (Preset), /CLR (Clear).

Functionarea: Reprezentarea tabelului de functionare se face analizand functionarea circuitului pentru

fiecare combinatie a lui Jn, Kn si Qn

Q = f J , K ,Q

n+1 n nn

In tabel se trece si /Qn pentru a facilita analiza functionarii. PR = CLR = 1

Tabelul 3.

Functionaarea bistabilului JK din figura 15 pentru Ti <tp

|

nJ |

nK |

nQ |

nQ |

n Q |

|

|

nQ |

|||||

|

nQ |

|||||

Analiza se bazeaza pe faptul ca iesirea unei porti SI-NU din circuitul de intrare este pe 1 daca cel putin

o intrare a sa este pe 0. Starea bistabilului /S-/R se poate modifica numai daca cel putin una dintre iesirile portilor P3si P este 0. Pentru Jn= Kn = 0, aplicarea impulsului CLKn+1 nu modifica starea bistabilului JK.

Se constata ca pentru Jn si Kn egale simultan cu 1 starea bistabilului este complementata la fiecare semnal de tact. Aceasta afirmatie, care presupune eliminarea nedeterminarii, nu e valabila decat in conditia in care durata impulsului de tact e mai mica decat un timp de propagare, tp reprezentand timpul de

propagare de la oricare intrare la orice iesire: Ti < tp tp = 2tpSi −NU

Neglijam durata fronturilor, dar nu si timpii de propagare. Daca iesirea Q a fost pe 0, dupa trecerea timpului tp, Q trece pe 1. Daca Ti < tp atunci aceasta este starea finala a bistabilului. Daca Ti are insa o durata mai mare, atunci dupa scurgerea a inca unui tp, Q trece din nou in 0, si asa mai departe, pana cand CLK devine 0. In acest caz apar oscilatii la iesire si nu se poate preciza starea finala a bistabilului.

Ecuatia caracteristica a bistabilului J-K, in ipoteza eliminarii nedeterminarii, in conformitate cu tabelul este:

Q = f J , K ,Q

n+1 n nn

![]()

Qn = J nK nQn + JnK nQn + JnK nQn + JnKnQn

Q = JQ ![]() (

(![]() Kn + K +

Kn + K + ![]() K

nQ (

K

nQ (![]() Jn + J

Jn + J

n+1 nn nnn

In final, se obtine urmatoarea expresie pentru ecuatia caracteristica:

![]()

Qn = JnQn + K nQn

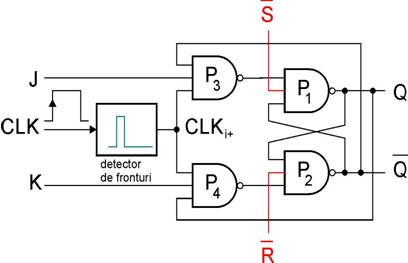

2.2. Bistabilul JK comandat pe front

Bistabilul JK a fost creat din dorinta de a elimina nedeterminarea produsa la latch-ul si bistabilul SR de combinatia S = R = 1. In cazul bistabilului JK, combinatia J = K = 1 conduce la complementarea iesirii dupa prima tranzitie activa a semnalului de tact (toggle). Literele J si K folosite pentru notarea intrarilor nu au o semnificatie specifica, ele sunt doar alaturate in alfabet.

Tabelul 4

Tabel de functionare pentru bistabilul JK comandat pe front

|

J |

K |

n Q |

Explicatie |

|

Q sters |

|||

|

Q setat |

|||

|

nQ |

(nici o modificare) |

||

|

nQ |

(complementare) |

Figura 22. - Bistabil JK comandat pe front crescator - schema simplificata.

Tabelul 5.

Efectul intrarilor asincrone prioritare

|

S |

R |

Q |

Comentarii |

|

setare bistabil |

|||

|

stergere bistabil |

|||

|

Q |

functionare normala, sincrona (nici un efect) |

||

|

combinatie interzisa |

conduce la Q=/Q=1, apoi la nedeterminare |

![]()

Intrarile asincrone prioritare notate cu S si R care servesc la initializarea starii bistabilului inaintea sau in timpul functionarii secventiale. Asincrone - nu exista nici o sincronizare intre aceste semnale si impulsurile de tact, ele sunt prioritare -determina starea bistabilului, daca sunt active si nu intrarile J, K.

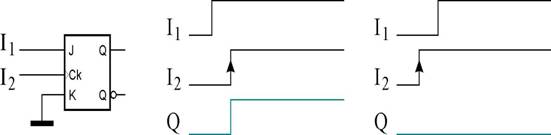

2.3. Aplicatie

Bistabilul JK comandat pe front poate fi folosit pentru determinarea ordinii a doua semnale I si I (figura 23).

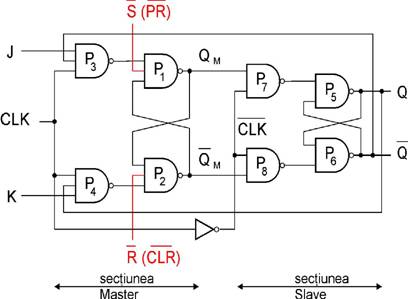

2. Bistabilul JK Master-Slave (JK MS)

Si acest tip de bistabil asigura eliminarea nedeterminarii starii Qn+1 pentru combinatia Jn= Kn = 1. In acest scop reactia globala de la iesiri la intrari este intrerupta pe durata impulsului de tact. Din acest motiv, oscilatiile care apar la iesirea bistabilului JK prezentat anterior si care duc la o stare nedeterminata a lui Qn+1 nu vor mai avea loc.

Comunicarea intre sectiunea Master si cea Slave este dirijata de portile P si P prin intermediul

semnalului de tact negat, CLK

Atat timp cat CLK , rezulta CLK , ceea ce impiedica transmiterea lui QMsi QM la sectiunea Slave. Prin aceasta se intrerupe bucla de reactie globala iesire-intrare pe toata durata impulsului de tact, evitand aparitia oscilatiilor observate la bistabilul JK din figura 15 si asigurandu-se o functionare corecta dupa tabel a ecuatiei bistabilului pentru orice durata a impulsului de tact.

In momentul aparitiei impulsului de tact n + 1 se modifica starea Qnin conformitate cu tabelul

de functionare, aceasta informatie nefiind transmisa spre iesire prin sectiunea Slave datorita inhibarii P si

P de catre CLK pe durata impulsului de tact. Dupa terminarea palierului impulsului de tact, incepand cu frontul sau scazator (crescator pe /CLK ) informatia Q se va transmite la iesirile Q QS

Reprezentarea diagramelor de timp nu tine seama de tp. Functionarea decurge dupa tabelul 3. Ecuatia caracteristica este si in acest caz:

Qn = JnQn + K nQn

3. Circuite basculante bistabile de tip D

O larga utilizare o au bistabilele D (Delay) si T (Toggle).

Aceste bistabile utilizeaza tot unul dintre tipurile de bistabile de baza vazute mai inainte. Numai ca

bistabilele D si T sunt fortate sa functioneze doar intr-o zona limitata a tabelelor de functionare ce

corespunde bistabilelor SR respectiv JK.

D - Delay (sau Data) - se pot realiza folosind bistabile SR sau bistabile JK de orice tip, ele

functioneaza doar in zona tabelului de functionare S = /R, respectiv J = /K

T - Toggle - isi comuta iesirile la fiecare impuls aplicat, el functioneaza in zona J = K=1. Se pot

realiza folosind bistabile JK-MS sau bistabile D transformate in bistabile T.

Bistabile D, clasificare:

-D-latch

-bistabile D comutate pe frontul scazator al impulsului de tact.

-bistabile D comutate pe frontul crescator al impulsului de tact.

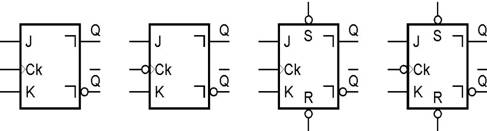

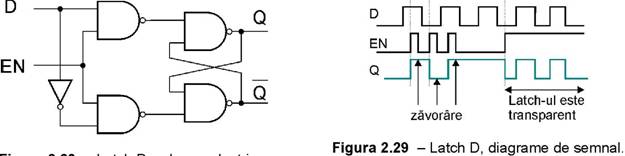

3.1. Latch-ul D

Latch-ul D este asemanator cu latch-ul SR care este utilizat pentru memorarea unui bit de informatie. Ca si in toate bistabilele D acest bistabil realizat din SR functioneaza cu restrictia ca S trebuie sa fie intotdeauna complementul lui R sau invers.

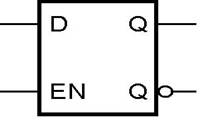

Figura 28 - Latch D, schema electrica.

Descrierea functionarii

Pentru EN = 1, Q = D (latch-ul este transparent). La tranzitia 1

![]() 0 a intrarii EN, latch-ul zavoraste ultima

0 a intrarii EN, latch-ul zavoraste ultima

valoare a lui D, memorand-o pana cand EN se modifica din nou. Tabelul 6.

Functionarea latch-ului D

|

EN |

D |

Q |

|

antQ |

||

|

antQ |

||

In prezent se fabrica in tehnologie TTL: 74LS75 - Latch cvadruplu, 74LS373 - latch octal des folosit, 74LS573 idem 373 dar cu o dispunere mai avantajoasa a intrarilor si iesirilor.

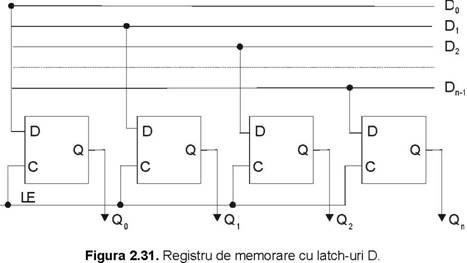

3.2. Aplicatie: Registru de memorare cu latch-uri D

Un latch D poate memora un bit de informatie, iar n latch-uri pot fi utilizate pentru memorarea unui cuvant cu n biti intr-un moment determinat prin aplicarea unui impuls scurt de tip STROBE la intrarile EN ale latch-urilor.

Magistrala de date pe n biti:

Fiecare latch

din figura de mai sus va memora un bit din magistrala de date in momentul in

care LE la tranzitia 1 ![]() 0 a semnalului LE.

0 a semnalului LE.

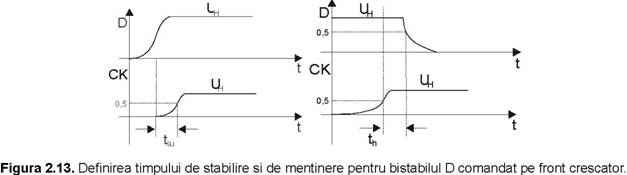

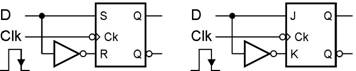

3.3. Bistabilul D comutat pe frontul scazator al impulsului de tact

Acest tip de bistabil se poate realiza:

a. folosind fie un bistabil SR-MS, fie un bistabil JK-MS (figura 26)

Figura 32. Bistabil D comandat pe front scazator din SR MS si JK MS.

b. folosind un latch D

Reprezentarea simbolica este data in figura 35. Descrierea functionarii

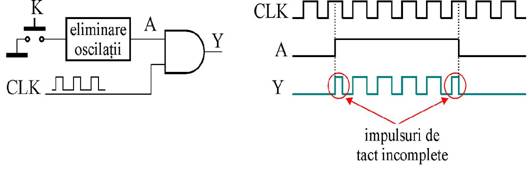

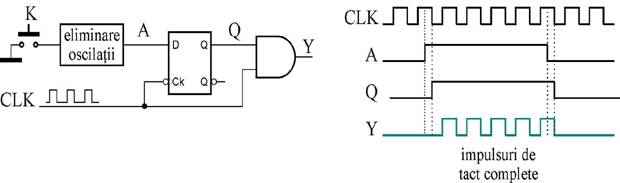

3. Aplicatie: Conditionarea si sincronizarea semnalului de tact

Echipamentele numerice sunt in general sincrone, in sensul ca diferitele semnalele interne variaza sincron in raport cu un semnal global de tact. Exista insa situatii in care trebuie prelucrate semnale externe asincrone, generate de exemplu de un operator uman. Defazajul temporal intre aceste semnale si tactul sistemului este aleator, iar daca nu se iau masuri de sincronizare, conditionarea unui semnal sincron cu un semnal asincron poate produce rezultate imprevizibile. Cazul cel mai frecvent de conditionare este cel prezentat in figura 33. Operatorul uman actioneaza aleator asupra unui comutator ale carui oscilatii mecanice sunt eliminate asa cum s-a aratat de exemplu la 1. Desi semnalul din punctul A este "curat" din punct de vedere al oscilatiilor, el este asincron fata de semnalul de tact, iar la iesirea portii SI se obtin si impulsuri incomplete.

Rezolvarea problemei descrise anterior este data in figura 3 Utilizand un bistabil D comandat pe front scazator, semnalul Q la iesirea acestuia este simultan sincronizat cu semnalul de tact si conditionat de intrarea A, astfel incat la iesirea Y se obtin doar impulsuri de tact complete.

3.5. Bistabile D comutate pe front crescator Varianta 1 Este realizat dintr-un latch D la care se adauga un detector de fronturi.

Bistabilul D-latch este validat pe o durata scurta plasata imediat dupa frontul crescator al semnalului de tact. Reprezentarea simbolica este data in figura 35.

Tema. Reprezentati cronogramele pentru acest caz.

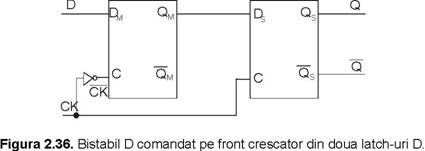

Varianta 2 Foloseste 2 latch-uri D si 1 inversor:

![]()

Functionarea este ilustrata de diagramele

de timp (se reprezinta D,CLK,CLK,QM,QS:

Functionarea este ilustrata de diagramele

de timp (se reprezinta D,CLK,CLK,QM,QS:

QS este determinat de CLK si QM

![]() tCK t

tCK t

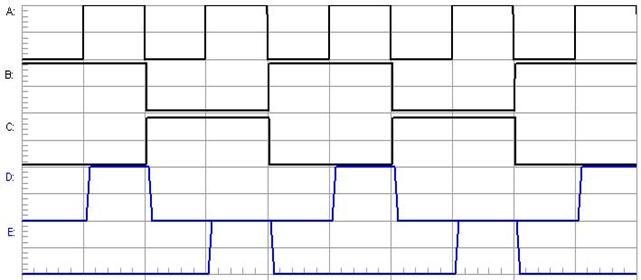

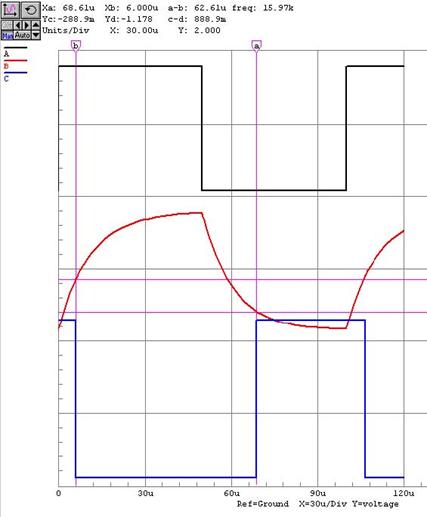

Figura 37. Cronograme pentru functionarea circuitului din figura 33.

Reprezentarile simbolice posibile pentru bistabilul D cu comutare pe front sunt prezentate in figura de mai jos:

Figura 38. Bistabil D comandat pe front crescator sau scazator (stanga) si cu intrari asincrone prioritare /S, /R (dreapta).

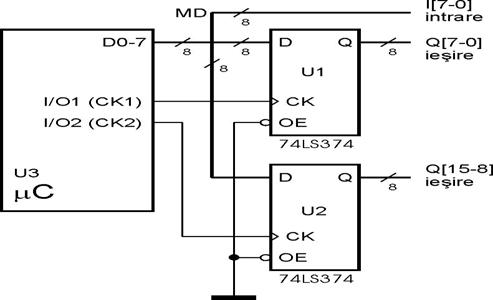

3.6. Aplicatie: Extensie I/O pentru un microsistem cu bistabile D octale

Descrierea schemei si a functionarii

3.7. Aplicatie: Determinarea ordinii a doua semnale

Sa se reproiecteze schema din figura 23 utilizand un bistabil D de tip 74LS7

Bistabilul de tip T

Bistabilul T (toggle) se caracterizeaza prin faptul ca el este fortat sa functioneze doar in doua situatii ce corespund la doua linii ale tabelului 4;

J = K = 1

nn

J = K = 0

nn

Intrarea T a unui astfel de bistabil se obtine prin interconectarea intrarilor J si K. Pentru realizarea bistabilului de tip T se folosesc numai bistabile JK-MS.

Figura 40. Bistabil T din JK. Figura 41. Bistabil T -simbol.

La functionarea secventiala:

![]()

-daca T este permanent egal cu Qn = Qn ; -daca T este permanent egal cu Qn = Qn

Ecuatia caracteristica se deduce din:

![]()

Qn = JnQn + K nQn

![]()

Qn = TnQn + T nQn

Tabelul 7

Functionarea bistabilului T

|

nT |

n Q |

|

nQ |

|

|

nQ |

![]()

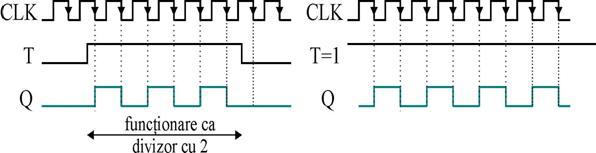

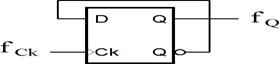

Daca T este permanent 1, Qn = Qn , bistabilul basculeaza la fiecare impuls de tact si se poate folosi ca divizor de frecventa a impulsurilor de tact raportat la iesirea Qn

fQ = fCK ![]() 2

2

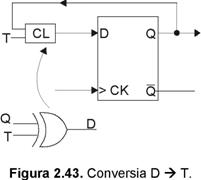

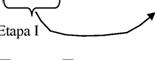

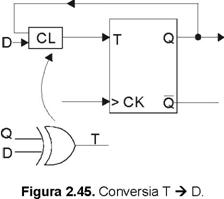

1. Aplicatie: Conversia bistabilelor D in T

Modalitatile

pe care le avem pentru a transforma un bistabil D in T sau invers. Cea mai

frecvent utilizata este conversia D ![]() T impusa de necesitatea divizarii frecventei

de tact cu 2.

T impusa de necesitatea divizarii frecventei

de tact cu 2.

Secventa de realizare:

Etapa II

Din tabel se obtine: Dn = T nQn + TnQn = Tn Qn . CL este o in acest caz poarta SAU-EXCLUSIV. Exista situatii in care un astfel de bistabil trebuie sa functioneze permanent ca divizor de frecventa (T=1) si in consecinta nu avem nevoie de o intrare T. Schema rezultata din relatia anterioara.

![]()

T Dn = Qn urmatoarea schema:

T Dn = Qn urmatoarea schema:

fQ = f CK![]()

Figura 4 Divizor de frecventa cu 2, un bistabil T particular, cu T =1.

2. Conversia T

Conversia unui T care comuta pe frontul descrescator intr-un D (care comuta pe frontul descrescator) se realizeaza similar (schema). Se foloseste acelasi tabel dar se deduce:

Tn = f (Dn ,Qn )

![]()

Tn = DnQn + DnQn = Dn Qn

Solutia este aceeasi: in loc de CL conectandu-se un SAU-EXCLUSIV.

Tabelul 8

Sinteza principalelor tipuri de bistabile

|

Tip |

Ecuatia caracteristica |

Latch Bistabil |

Comuta |

TTL |

CMOS |

Observatii |

|||||

|

pe |

Tip |

n |

Tip |

n | |||||||

|

Latch |

Palier, 1 Palier, 1 |

3 stari, porti SAU-NU 3 stari, porti SI-NU |

|||||||||

|

SR |

R QSQRSQ |

bistabil |

Palier |

cu intrare de comanda |

|||||||

|

bistabil |

Front | ||||||||||

|

Bistabil |

MS | ||||||||||

|

JK |

nnn K QJ QQ |

Bistabil |

front |

74276 4 bistabile JK 74376 4 bistabile JK |

|||||||

|

Bistabil |

MS | ||||||||||

|

D |

DQ |

Latch |

Palier | ||||||||

|

nn DQ |

Bistabil |

Front | |||||||||

|

T |

nnn T QT QQ |

Bistabil | |||||||||

5. Aplicatii

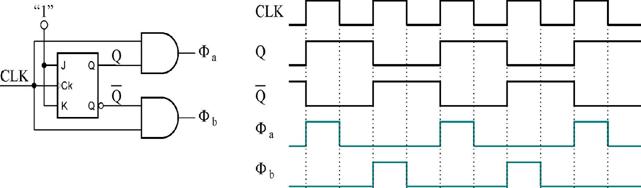

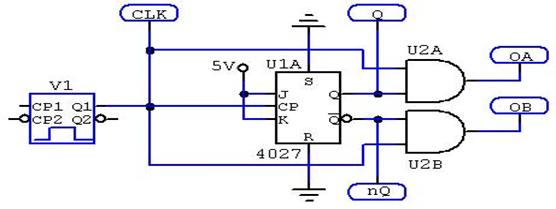

5.1. Generarea unui semnal de tact cu doua faze

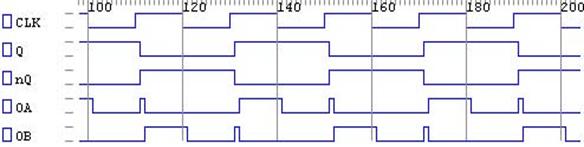

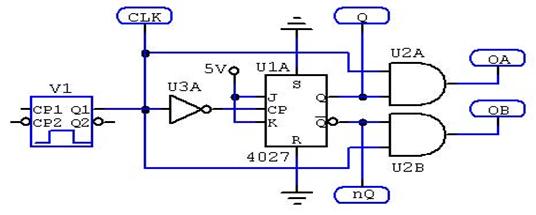

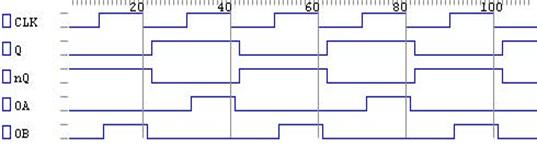

Este uneori necesara generarea unui semnal de tact cu mai multe faze. In figura 46 este ilustrat un asemenea caz, in care bistabilul JK comutat pe front crescator functioneaza ca divizor cu 2, iar iesirile sale sunt preluate de doua porti SI pentru a genera fazele Φa si Φb. Diagramele de semnal sunt reprezentate pentru cazul ideal, in care tp = 0. Realizand practic montajul sau simulandu-l se constata insa o comportare complet diferita - atat Φa cat si Φb prezinta o serie de impulsuri scurte (glitch).

Explicatia acestei comportari se obtine studiind atent formele de unda din figura 48: tinand cont de timpul de propagare tp prin bistabilul JK, intre CLK si Q pe de o parte, respectiv CLK si nQ pe de alta parte vor aparea conditii de suprapunere pe 1 (race conditions) - ceea ce conduce la comutarea falsa in 1 a iesirilor portilor U2A si U2B.

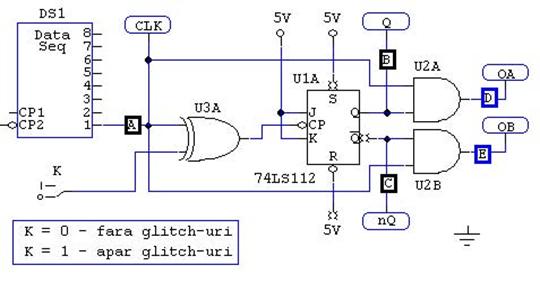

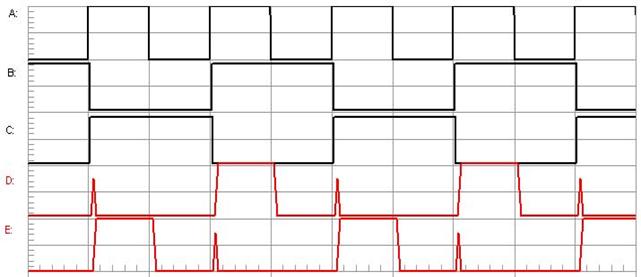

Rezolvarea acestei situatii se poate face simplu, adaugand un inversor la intrarea de tact a bistabilului U1A, care va comuta pe frontul scazator al semnalului de tact CLK si in acest fel se elimina suprapunerea nedorita in 1 intre tact si iesirile bistabilului (figura 50).

Schemele din figurile 47 si 49 au fost simulate in Circuit Maker in modul digital, in care toate circuitele se presupune ca au acelasi timp de propagare. O simulare mai precisa se obtine redesenand schema pentru modul analogic (figura 51). In acest caz se foloseste un bistabil JK comandat pe front scazator (74LS112) fata de bistabilul JK MS CMOS 4027 din figurile 47 si 49. Prezenta si absenta inversorului U3A este realizata cu circuitul SAU-EXCLUSIV si a comutatorului K. Legatura de masa nu este uitata pe schema - pentru simularea analogica SPICE este obligatorie prezenta a cel putin unei legaturi la masa, chiar daca in acest caz ea este aparent nefolosita.

5.2. Circuit de intarziere

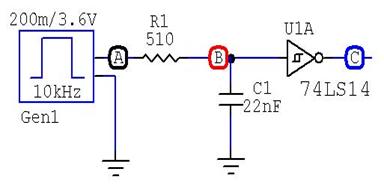

Realizarea unui circuit de intarziere cu un trigger Schmitt este extrem de simpla (figura 54). Generatorul Gen1 simuleaza iesirea unei porti TTL (V0L = 200 mV, V0H = 3,6 V).

Pentru a evalua intarzierea, se scrie expresia tensiunii pe condensator in functie de timp:

t

uC (t) = uC (∞) − [uC (0) − uC (∞)] e RC

Pentru incarcarea condensatorului, se particularizeaza uC (0) = VOL + IIL R si uC (∞) = VOH . Rezulta:

Pentru exemplul din figura, VOL = 0.2 V, VOH = 3.6 V, IILR = 0,125 V, VPSUS = 1,9 V, adica t = RC ln 1.926 = 0.66 RC = 7,35 s. t este delimitat in simulare de cursorul b, pentru t rezultand o valoare de 6 s (figura 55).

Pentru descarcarea condensatorului, se particularizeaza uC (0) = VOH si uC (∞) = VOL + IIL R . Rezulta:

Pentru exemplul din figura, VOL = 0.2 V, VOH = 3.6 V, IILR = 0,125 V, VPJOS =1,1V,adicat = RC ln 38 =

1.48 RC = 16,59 s. t este delimitat in simulare de cursorul a, pentru t rezultand o valoare de 18,61 s (figura 55).

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 3285

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2024 . All rights reserved