| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

Este utilizat pentru detectarea erorilor de transmisie a informatiei binare. Functia este un circuit logic combinational care determina paritatea sau imparitatea numarului de variabile de intrare egal cu 1, generand un bit de paritate sau imparitate. Un astfel de detector se bazeaza pe detectoare elementare de imparitate cu doua intrari (circuit SAU-EXCLUSIV).

Tabelul 3.x

Functionarea portii SAU-EXCLUSIV ca generator de imparitate

|

I1 |

I2 |

IMP |

![]()

Figura 3.52. Generator de imparitate din poarta SAU-EXCLUSIV.

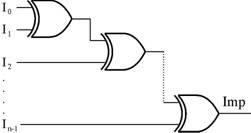

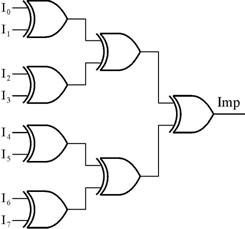

Structura detectorului poate fi in lant sau arborescenta.

a. Structura in lant. La aceasta structura trebuie sa tinem seama de:

pentru n intrari sunt necesare n-1 circuite XOR

timpul de propagare pe traseul critic: tp = (n - 1) tpXOR

numarul de intrari n poate fi un numar par, cat si impar

b. Structura arborescenta. La aceasta structura trebuie sa tinem seama de:

pentru n intrari sunt necesare n - 1 circuite XOR;

timpul de propagare tp = (log2 n) tpXOR este mai mic decat la structura in lant;

numarul de intrari n trebuie sa fie un numar par.

Figura 3.53. Generator de imparitate cu structura in lant.

Figura 3.54. Generator de imparitate cu structura arborescenta.

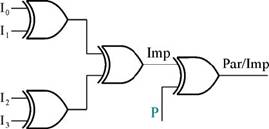

Orice detector de imparitate se poate transforma intr-unul de paritate prin folosirea unui inversor suplimentar. Astfel de circuite permit utilizatorului, in functie de aplicatie, sa aleaga functia indeplinita, stabilind printr-un bit daca circuitul functioneaza ca un detector de paritate sau imparitate.

Figura 3.55. Generator de paritate / imparitate selectabil.

(P = 1 inversor P = 0 neinversor)

In prezent se folosesc:

74HC180

are 8 intrari; 2 iesiri PAR si IMPAR; 2 intrari de interconectare;

structura arborescenta;

se foloseste pentru detectarea erorilor de transmisie.

74LS280

are 9 intrari; 2 iesiri PAR si IMPAR

structura in lant

este folosit pentru detectarea erorilor de memorare ale unui cuvant binar cu 8 biti. Verifica daca informatia citita din memorie are aceeasi paritate ca si cea inscrisa. In afara de cei 8 biti memoria trebuie sa asigure si memoria de paritate.

|

P |

In cazul unei linii de transmisie exista campuri electromagnetice care pot sa modifice informatia trimisa de la sursa.

Figura 3.53. Sistem de transmisie cu semnalizarea paritatii.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2793

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2024 . All rights reserved