| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

NUMARATOARE

0. Introducere

Numaratoarele sunt circuite care evolueaza periodic (ciclic) intre anumite stari. Numarul starilor distincte dintr-un ciclu se numeste modulul numaratorului si se noteaza cu m. Numaratoarele in inel sau Johnson, realizate cu registre de deplasare formate din bistabile D, studiate anterior aveau modulul m = n respectiv m =2n; (n era numarul de bistabile a registrului). In acest caz m ≤ 2n .

Se pune problema obtinerii cu acelasi numar de bistabile n a unui numar cat mai mare de stari distincte in cadrul unui ciclu, adica a maririi modulului m. Numarul n de bistabile necesare pentru realizarea unui numarator modulo m este n ≥ log2 m.

1. Clasificarea numaratoarelor

Dupa modul de aplicare a impulsurilor de tact

-asincrone -tactul se aplica numai bistabilului celui mai putin semnificativ, urmatoarele bistabile au

semnalul de tact provenit de la iesirea Q sau /Q a bistabilului precedent;

-sincrone

- impulsul de tact se aplica simultan tuturor bistabilelor.

Dupa modul

-Binare m =2n;

-Zecimale sau decadice m = 10;

-Modulo

p ≠ 2n .

Dupa sensul

de numarare

-directe - acestea numara intr-un singur sens in sens direct adica crescator;

-inverse -acestea numara in sens descrescator

-reversibile -numara in ambele sensuri adica atat in sens direct cat si in sens

invers.

Un numarator care evolueaza ciclic prin exact 10 stari se numeste zecimal sau decadic. Daca cele 10 stari sunt 0, 1, 2, , 9 atunci el se mai numeste numarator BCD (Binary Coded Decimal).

Bistabilele utilizate in constructia numaratoarelor sunt de tip T realizate de obicei din bistabile JK sau D-MS, cu T = 1 permanent sau uneori cu validarea accesibila in exterior.

Initializarea numaratorului se face de obicei prin intermediul semnalului de stergere (Reset sau Master Reset), activ SUS sau JOS (nMR). Stergerea se poate face asincron, daca survine independent de starea semnalului de tact si de indata ce semnalul MR este activ sau sincron, in care stergerea se face numai dupa frontul activ al semnalului de tact (crescator sau descrescator).

Anumite numaratoare poate fi initializate in orice stare daca sunt prevazut cu posibilitatea incarcarii paralel, folosind o linie aditionala notata LD (LOAD), activa SUS sau JOS (nLD). Incarcarea se poate face asincron, daca survine indata ce semnalul LD este activ sau sincron, in care incarcarea se face numai dupa frontul activ al semnalului de tact (crescator sau descrescator).

2. Numaratoare asincrone

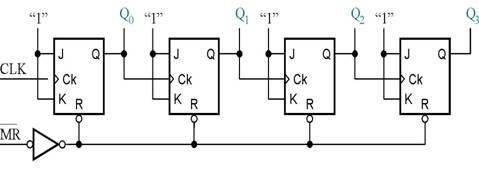

2.1. Numaratorul asincron binar direct

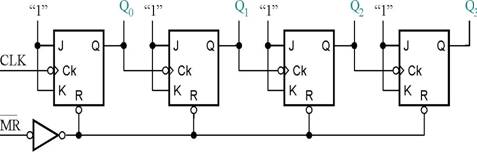

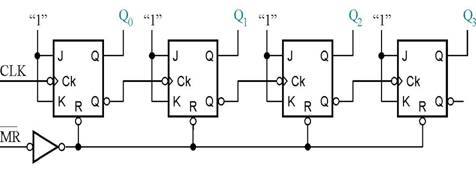

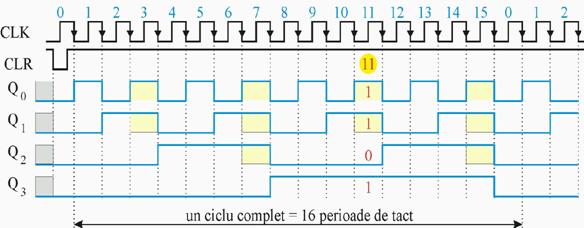

Pentru n = 4 bistabile numarul starilor distincte (modulul numaratorului) binar este m = 24 = 1 Impulsurile de tact se aplica primului bistabil, urmatoarele bistabile avand fiecare ca semnal de tact iesirea Q a bistabilului anterior. Bistabilele functioneaza in regim de divizor de frecventa. Divizarea frecventei de tact depinde de pozitia in numarator a bistabilului la iesirea caruia se culege semnalul.

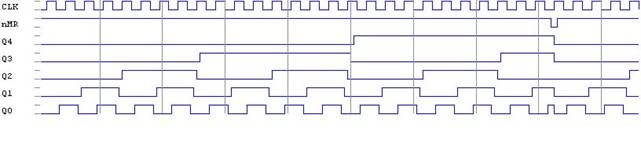

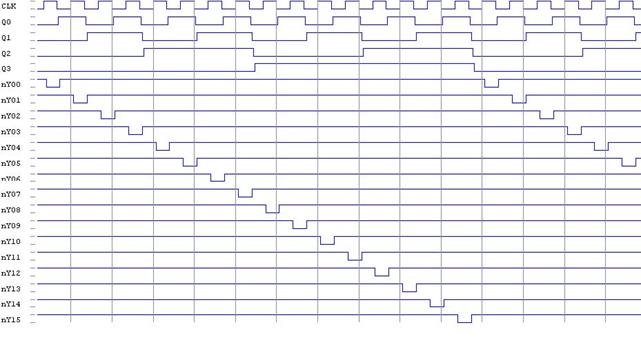

In figura 2 s-a reprezentat un ciclu complet de functionare si partial inceputul celui de-al doilea ciclu. Iesirile numaratorului evolueaza in sens crescator (direct), cu fiecare impuls de tact aplicat valoarea la iesire creste cu o unitate. Numaratorul prezentat este modulo 16 (are 4 bistabile). Cel de-al 16-lea impuls de tact incheie ciclul, el aducand numaratorul pe zero. Cel de-al 17-lea este primul impuls de tact din cel de-al doilea ciclu.

La un moment dat codul binar de iesire corespunde numarului de impulsuri de tact aplicate in ciclul respectiv, in aceasta constand practic functia de numarare. Citind iesirile dupa cel de-al 11-lea impuls de tact, rezulta Q Q Q Q = 1011, care este tocmai corespondentul in binar al numarului zecimal 11.

Pentru extinderea capacitatii de numarare se pot conecta mai multe numaratoare in cascada prin conectarea iesirii Q la intrarea de tact a urmatorului numarator.

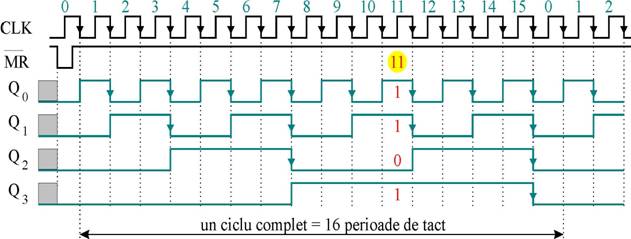

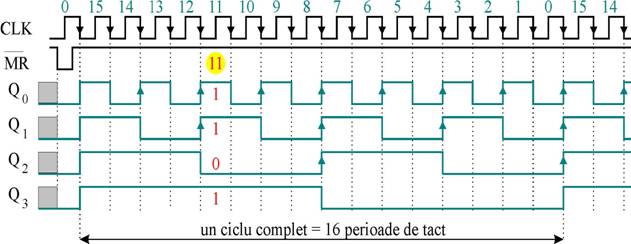

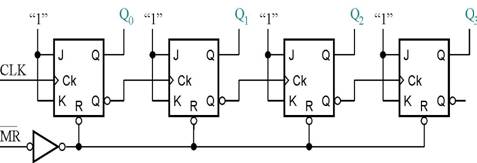

2.2. Numaratorul asincron binar invers

In anumite aplicatii este necesara utilizarea unor numaratoare care sa poata numara si in sens invers, adica numaratorul sa isi micsoreze continutul cu cate o unitate la fiecare impuls de tact. In acest scop semnalul de tact a bistabilului urmator nu se mai culege de la iesirea Q a bistabilului anterior, ci de la iesirea nQ.

Cand Q trece din 1 in 0, nQ trece din 0 in 1, (bistabilul urmator nu comuta), dar cand Q trece din 0 in 1, nQ trece din 1 in 0 si determina comutarea bistabilului urmator. Acest lucru poate fi verificat in tabelul

Tabelul 1

Functionarea (partiala) a numaratorului binar asincron invers

|

Tactul |

Q |

Q |

Q |

Q |

Corespondent zecimal |

|

Valoare initiala | |||||

Tema. Sa se analizeze functionarea numaratoarelor din figurile 5 si

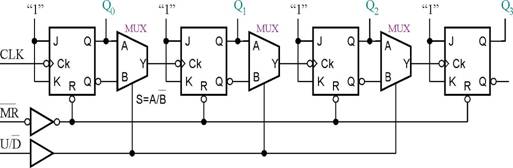

2.3. Numaratorul asincron binar reversibil

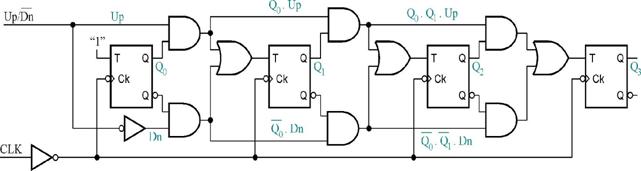

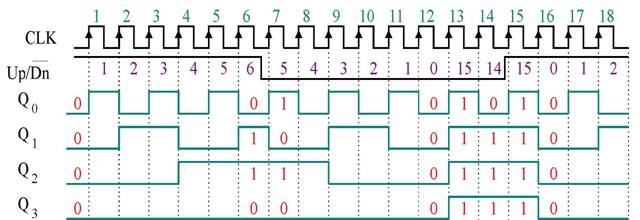

Numaratorul reversibil (figura 7) poate efectua atat operatia de numarare in sens direct (in sus) cat si in sens invers (in jos). Determinarea sensului de numarare se stabileste printr-o linie suplimentara de sens notata de obicei U/nD (UP/nDOWN). Bistabilele folosite sunt de tip T realizate din JK sau D-MS.

-daca U/nD = 1

se conecteaza Qk ? CLKk+1, numarare in sens direct;

-daca U/nD = 0 se conecteaza /Qk ?

CLKk+1, numarare in sens invers.

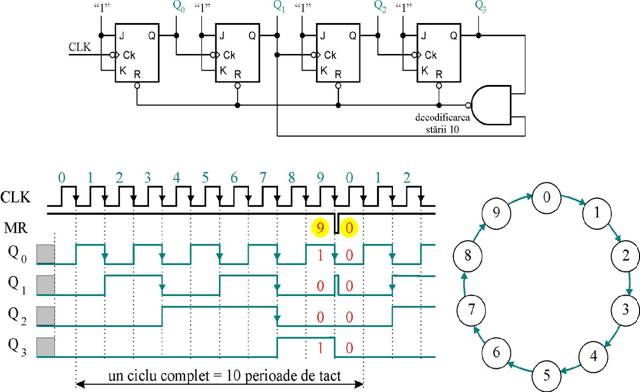

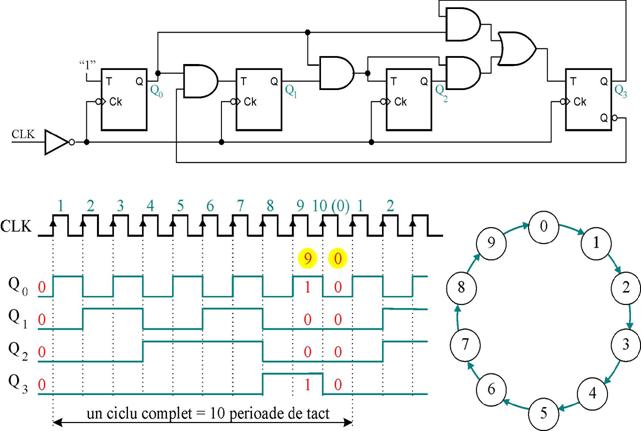

2.4. Numaratoare asincrone zecimale

Numaratorul zecimal din figura 8 este des intalnit in aplicatiile practice. El se bazeaza pe structura numaratorului asincron binar din figura 1 la care se adauga un circuit de decodificare a starii 10, format dintr-o poarta SI-NU. Cand numaratorul ajunge in starea 10, iesirea portii SI-NU trece in 0 logic, determinand trecerea numaratorului in starea 0, dupa care ciclul de functionare se repeta.

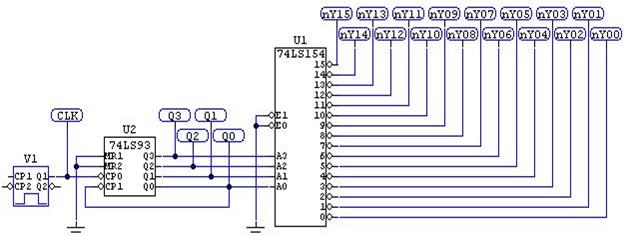

2.5. Numaratoare asincrone disponibile pe piata

Cele mai utilizate numaratoare asincrone in tehnologie TTL sunt 74LS93 (binare direct) si 74LS90 (zecimal direct). Ele sunt dublate de variantele ulterioare 74LS293 si 74LS290 la care alimentarea se face la pinii 8 (GND) si 16 (VCC), deoarece la 74LS93 respectiv 74LS290 pinii de alimentare erau plasati neobisnuit (pinul 10 - GND, pinul 5 VCC). Varianta 74LS390 contine echivalentul a 2 numaratoare 74LS290 intr-o singura capsula, iar 74LS393 contine echivalentul a doua 74LS293 intr-o singura capsula. In tehnologie CMOS sunt disponibile mai multe numaratoare asincrone, de exemplu 4020, 4040, 4060 (tabelul 4.x).

![]() 2n

2n

2. Sinteza numaratoarelor asincrone modulo p

Exista aplicatii in care modulul numaratorului nu mai este o putere intreaga a lui 2 (m ?2n unde n natural). Modulul unui astfel de numarator se va nota cu p. Pentru un ceas electronic, p poate fi egal cu 7, 12, 24, 38, 29, 30, 31, 365, 366 etc. Se pot realiza astfel de numaratoare modulo p, cu p = m plecand de la numaratoare binare asincrone cu m =2n , transformarea efectuandu-se prin scurtarea ciclului de functionare a numaratorului la p stari, cu p = m.

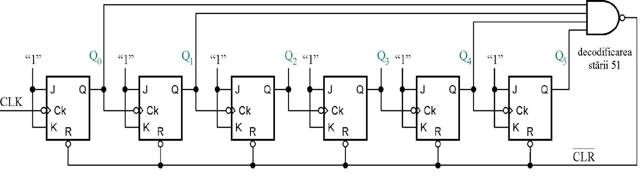

Modul in care se determina structura unui astfel de numarator este ilustrat in exemplul urmator. Fie un numarator asincron direct (in sens crescator) cu p = 51. Numarul minim de bistabile necesar n se determina din conditia: 2n-1 < p <2n, adica 2n-1 < 51 <2n, indeplinita in conditiile exemplului considerat

pentru n =6 (32 < 51 < 64).

Functionarea numaratorului cu p = 51 implica practic resetarea acestuia in cadrul unui ciclu dupa aplicarea celui de al 51-lea impuls de tact. Acest lucru este posibil prin identificarea starii 51 cu ajutorul unui circuit decodificator, care in cel mai simplu caz poate fi o poarta SI-NU si stergerea numaratorului prin activarea liniei nCLR. In figura 10 este prezentata schema numaratorului modulo 51 care functioneaza pe acest principiu.

Resetarea numaratorului trebuie sa se produca in momentul in care numaratorul ajunge in starea p =

51. Modulul p = 51 se poate scrie in binar sub forma:

p =51= 1*32+1*16+0*8+0*4+1*2+1*1 adica:

|

Q |

Q |

Q |

Q |

Q |

Q |

|

|

Determinarea acestei stari se face utilizand o poarta SI-NU cu 4 intrari la care sunt conectate o parte din iesirile numaratorului, respectiv Q Q Q si Q care sunt pe 1 logic pentru prima data intr-un ciclu de numarare pentru starea 51. In urma activarii liniei /CLR in care iesirea portii SI-NU este 0 logic, aceasta stare se va transforma in starea 000000 (starea initiala). Astfel numarul starilor distinct ale numaratorului este redus de la 64 (corespunzatoare modulului m= 26) la p = 51.

In structura prezentata schema nu prezinta o functionare sigura datorita dispersiei timpilor de propagare tPCLR→Q. Bistabilul cu timpul de propagare cel mai redus se reseteaza primul, iesirea Q corespunzatoare care este legata la una din intrarile portii SI-NU trece pe zero. Iesirea portii SI-NU trece in 1 logic intrerupand astfel procesul de stergere integrala a numaratorului (a bistabilelor care au mai ramas pe 1 logic).

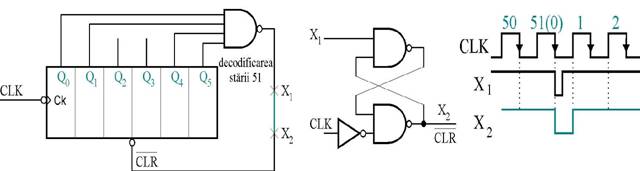

Pentru inlaturarea acestui neajuns este necesar un circuit de memorare a semnalului de stergere (nCLR) pe o durata care sa fie mai mica decat perioada de repetitie a impulsului de tact, dar suficient de mare pentru initializarea sigura pe "0" a tuturor bistabilelor. Acest circuit se intercaleaza intre X1 si X2 si are schema din figura 11.

Dupa cum se observa din schema, circuitul de memorare folosit este in acest caz un latch S-R. Iesirea portii SI-NU, X1 se afla pe 1 logic pana cand apare frontul scazator al celui de al 51-lea impuls de tact. In acest moment X1 trece in 0 logic, determina setarea bistabilului si punerea liniei X2 pe 0 logic. In acest moment incepe procesul de stergere a numaratorului. Iesirea portii SI-NU, X1 va sta scurt timp pe 0 logic, mai exact pana cand una din iesirile Q , Q , Q sau Q trece pe 0 logic. Desi X1 este deja 1 logic, latch-ul memoreaza impulsul de stergere, mentinand in continuare linia X2 pe 0 logic pana cand apare frontul crescator al impulsului de tact, in care se produce resetarea bistabilului SR si trecerea iesirii X2 pe 1 logic. Se poate observa ca latimea noului impuls de stergere X2 = /CLR este proportionala cu durata cat semnalul de tact, CLK, este pe 0 logic. Se presupune ca acest interval de timp este suficient de mare pentru stergerea (initializarea) tuturor bistabilelor din care este compus numaratorul. In caz contrar, factorul de umplere al semnalului de tact se alege astfel incat sa fie satisfacuta aceasta conditie.

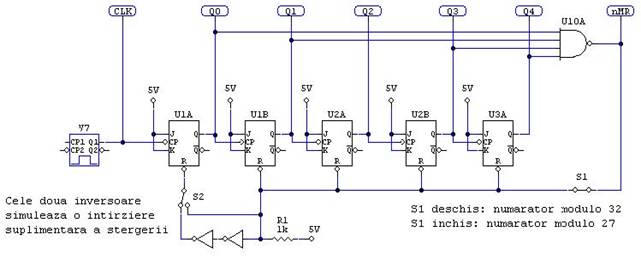

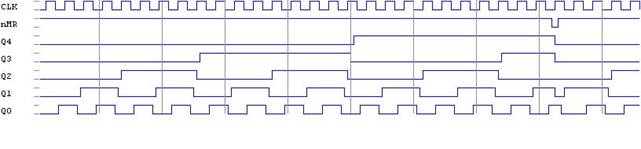

In figura 12 este prezentata schema electrica pentru un numarator asincron direct cu n = 5 bistabile, cu un ciclu de 32 de stari (S1 deschis), respectiv de 27 de stari (S1 inchis). Cele doua inversoare din schema asociate bistabilului U1A simuleaza o stergere intarziata a respectivului bistabil -un tpCLR→Q mai mare decat la celelalte bistabile. Cu S2 se poate valida sau inhiba aceasta intarziere suplimentara.

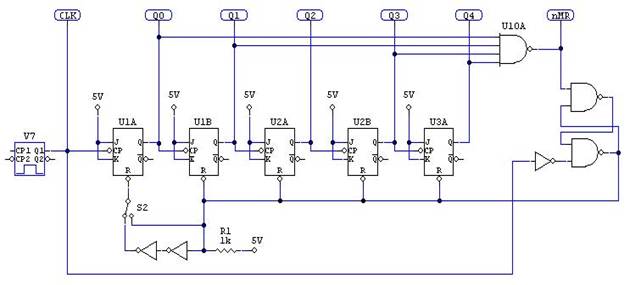

Figura 13.a. Numarator asincron direct modulo p = 27, functionare corecta(S1 inchis, S2 spre dreapta).

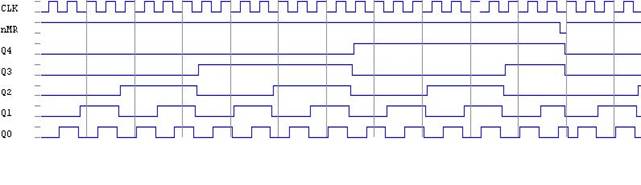

Figura 13.b. Numarator asincron direct modulo p = 27, functionare incorecta in secventa 26, 27+ stergere, 2, 3, obtinuta pentru S1 inchis si S2 spre stanga.

2.7. Determinarea frecventei maxime de operare pentru numaratoarele asincrone

Principalul avantaj al numaratoarelor sincrone il constituie simplitatea arhitecturii, aspect contrabalansat de dezavantajul major al unei frecvente maxime de operare reduse, datorata propagarii succesive a semnalului de tact. Intarzierea produsa de un bistabil este egala cu tpCLR→Q. Pentru stabilirea frecventei, maxime de operare trebuie tinut cont de cazul cel mai defavorabil in care comuta toate cele n bistabile, impulsul de tact urmator se putandu-se aplica numai dupa stabilizarea efectului impulsului de tact anterior. Uzual starea stabila a numaratorului inaintea aplicarii unui nou impuls de tact trebuie sa dureze un interval de timp Δt necesar citirii starii numaratorului (decodificarea cuvantului de stare). Din aceste motive perioada minima de repetitie a tactului in cazul cel mai defavorabil este:

TCLK min = n tP(CLK →Q) +Δt

unde n este numarul de bistabile din componenta numaratorului. In cazul in care intre iesirea Q a bistabilului anterior si intrarea CLK a bistabilului urmator exista circuite care produc intarzieri (de exemplu multiplexoare la numaratoarele reversibile), durata minima a impulsului de tact este:

TCLKMax = n tp(CLK →Q) + (n −1)t pMUX +Δt , iar frecventa maxima de functionare este:

Acest fenomen limiteaza frecventa maxima de tact la care poate functiona numaratoarele asincrone (de exemplu pentru circuitele 74LS90, 74LS93 fMax = 16 MHz, tipica pentru numaratoare asincrone ).

3. NUMARATOARE SINCRONE

Aceasta categorie de circuite asigura functionarea la frecvente mult mai mari decat in cazul numaratoarelor asincrone datorita aplicarii simultane a impulsului de tact la intrarile de tact ale tuturor bistabilelor.

3.1. Metode de generare a semnalului T

In cadrul unui ciclu de functionare al numaratorului la trecerea dintr-o stare in alta in urma aplicarii impulsului de tact CK , unele bistabile trebuie sa basculeze, altele nu. Inseamna ca trebuie utilizate bistabile de tip T cu intrarea T accesibila (bistabilul JK − MS la care J se leaga impreuna cu K si formeaza T ) pentru a permite ca inaintea aplicarii urmatorului impuls de tact sa se aplice la intrarea T a bistabilului ce trebuie sa basculeze (conform tabelului de functionare), nivelul 1 logic, iar la intrarea T a celorlalte nivelul 0 logic. Apare astfel necesitatea utilitarii unor circuite logice pentru generarea valorilor T ce corespund

celor n bistabile folosite pentru ca functionarea numaratorului sa decurga in conformitate cu tabelul de

functionare dorit.

Procedura de determinare a structurii circuitului logic destinat generarii

valorilor logice pentru intrarile T se

va exemplifica pentru tabelul de functionare ce corespunde unui numarator binar

sincron pe 4 biti.

Procedura poate fi aplicata similar si unor numaratoare care functioneaza dupa

alte tabele de functionare.

Tabelul de functionare (este valabil atat pentru numaratoarele asincrone cat si pentru cele sincrone):

|

Nr. tacte |

Q |

Q |

Q |

Q |

|

initializare | ||||

|

|

T

T = Q0

T = Q0 Q1 = Q1 T1 T = Q Q Q = Q T

...........

Tn = Q Q Qn = Tn Qn

Din tabel se deduc urmatoarele:

-bistabilul de rang 0 trebuie sa basculeze la fiecare impuls de tact, deci T0 = 1 in permanenta.

-bistabilul de rang 1 basculeaza numai atunci cand in starea de dinaintea aplicarii impulsului de tact

Q = 1, deci T = Q

-bistabilul de rang 2 basculeaza numai atunci cand in starea anterioara atat Q0 cat si Q1 sunt pe "1"

adica: ![]()

-bistabilul Q3 basculeaza numai atunci cand anterior aplicarii impulsului de tact Q0, Q1 si Q2 sunt pe "1" deci T = Q Q Q = Q T

In general se poate scrie: Tn = Q Q Qn = Tn Qn

Revenind la numaratorul pe 4 biti, in functie de modul de scriere al valorilor T se disting doua metode de generare a acestora:

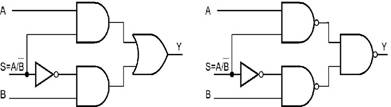

-seriala - in acest caz valorile lui T se obtin din valorile anterioare: ![]()

-paralela - la care valorile lui T se obtin direct din valorile

lui Q: ![]()

Generarea valorilor lui T pentru un numar de 4 biti prin metoda seriala:

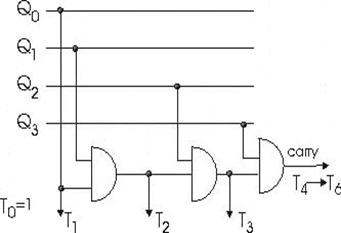

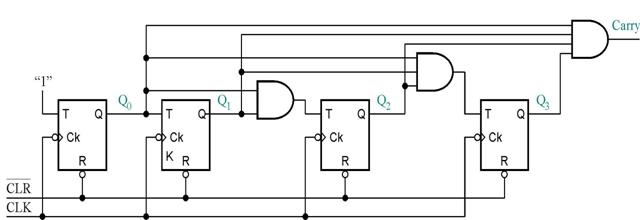

Figura 1 Generarea semnalelor T0 - T3 si T4 (Carry).

Semnalul Carry se genereaza

din semnalul T3 si Q3 si se aplica intrarii T0 a numaratorului urmator in cazul

extinderii capacitatii de numarare.

In cazul generarii seriale a valorilor T in cazul cel mai defavorabil,

durata minima a impulsului de tact este data de: TCK min = tP(CK

→Q) +(n − 2)tPSI +Δt .

Dezavantaj: -tp mai mare decat in cazul generarii paralele a valorilor T Avantaje: -se utilizeaza numai porti SI cu doua intrari.

In cazul generarii paralele a valorilor T , durata minima a impulsurilor de tact este:

TCK min = tP(CK →Q) + tPSI +Δt

Se observa ca tp este mai mic decat la numaratoarele asincrone cu acelasi numar de bistabile (frecventa de tact mai ridicata). Din acest motiv aceasta este varianta preferata la realizarea numaratoarelor in integrate.

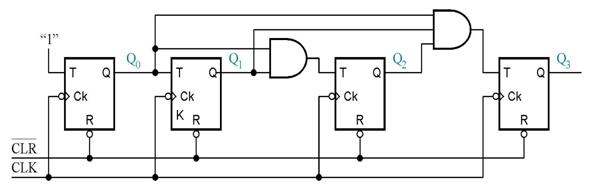

3.2. Numaratorul sincron binar direct pe 4 biti

Descrierea functionarii

Schema unui numarator binar sincron pe 4 biti cu generarea paralela a semnalului T.

Relatiile pentru generarea valorilor T sunt cele ce nu contin pe T anterior. Fiecare valoare T este generata doar pe baza valorilor Q pentru a scurta timpul de generare. Astfel intarzierea de generare este doar a unei singure porti SI. Impulsurile de tact CK se aplica simultan la toate bistabilele. Exista de asemenea o intrare de initializare comuna /CLR pentru toate bistabilele. Numaratorul numara doar in sens direct (crescator), iar iesirea CARRY serveste pentru interconectarea numaratorului reprezentat cu un alt numarator identic pentru bitii superiori Q Q si se conecteaza la intrarea T care devine practic T al celui de al doilea numarator.

3.3. Numarator sincron reversibil

Descrierea functionarii

3.4. Numarator sincron BCD

Descrierea functionarii

3.5. Numarator sincron presetabil

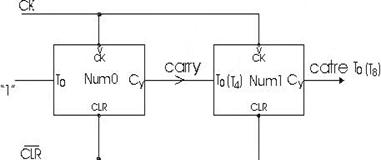

3. Extinderea capacitatii de numarare

Pe langa legatura amintita trebuie interconectate si intrarile de tact si de stergere ca in figura urmatoare ce prezinta interconectarea a doua numaratoare sincrone pe 4 biti:

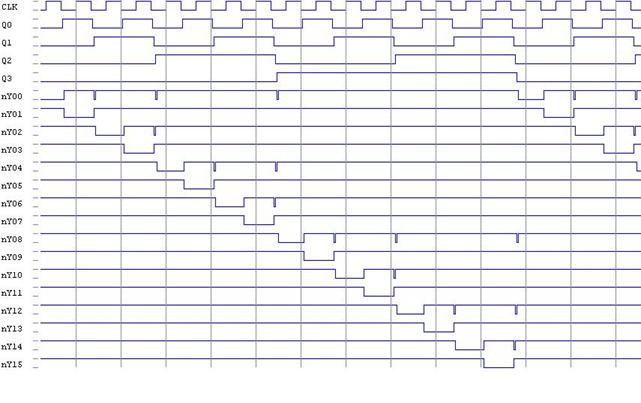

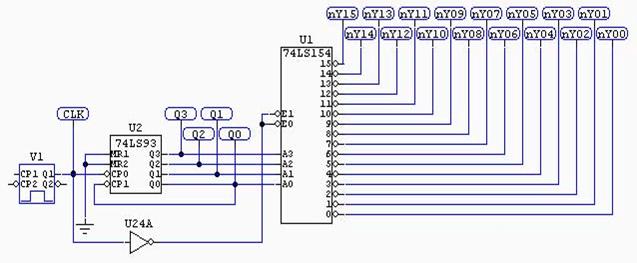

3.7. Decodificarea iesirii numaratoarelor

3.8. Sinteza numaratoarelor sincrone

4. DIVIZOARE DE FRECVENTA

Orice numarator este in acelasi timp un divizor de frecventa, raportul de divizare fiind chiar modulul p al numaratorului. Cel mai simplu caz este cel cu divizare cu un raport fix, iar cel mai flexibil - divizorul programabil de frecventa, la care raportul de divizare este specificat din exterior si se poate modifica oricand. Este important de aratat ca nu intotdeauna factorul de umplere la iesirea divizorului este , existand aplicatii in care acest aspect nu este deranjant. Daca se doreste un factor de umplere de exact trebuie adaugata logica suplimentara, asa cum se va vedea in exemplele urmatoare. Daca raportul de divizare este un numar par, de exemplu 2 k, cea mai simpla metoda de a obtine un factor de umplere de este de a diviza mai intai cu k si apoi cu 2 (cu un bistabil D sau JK comandat pe front).

4.1. Divizoare de frecventa cu un numar fix 4.2. Divizoare programabile de frecventa

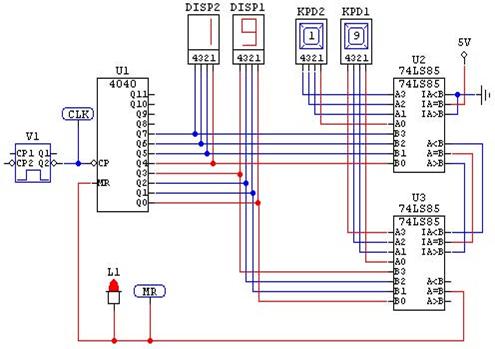

Schema din figura x utilizeaza un numarator asincron CMOS (4040) si doua comparatoare pe 4 biti pentru a specifica raportul de divizare. Numaratorul evolueaza direct, de la 0 pana la valoarea prestabilita de [KPD2 :KPD1], moment in care cele doua comparatoare sesizeaza egalitatea si activeaza semnalul de stergere MR. Adaugand un al treilea comparator se obtine in acelasi mod un divizor programabil de frecventa pe 12 biti. Schema prezentata este una care functioneaza foarte bine in regim de simulare digitala, dar nu in realitate deoarece foloseste circuite CMOS si TTL LS in acelasi montaj. Pentru a rezolva acest neajuns, cel mai bine este sa se foloseasca variantele HC sau HCT ale circuitelor prezentate: 74HCT4040 si 74HCT85, caz in care schema nu va mai prezenta nici un neajuns.

Intrebari: Indicati potentialele probleme ale schemei din figura x.

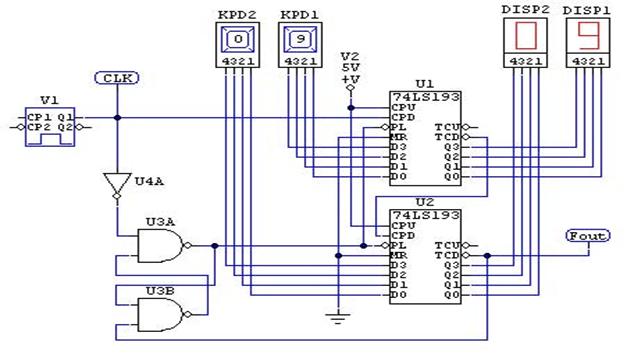

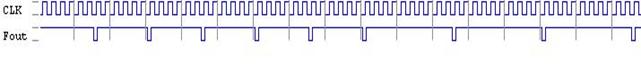

Al doilea exemplu de divizor programabil utilizeaza doua numaratoare sincrone configurate sa evolueze in sens invers (U1 si U2) si un latch RS de memorare a impulsului de stergere, asa cum a fost prezentat in figura 11. Functionarea divizorului este simpla: [KPD2:KPD1] specifica raportul de divizare, numararea se face in sens descrescator de la p spre 0, starea 0 determinand stergerea latch-ului RS si incarcarea numaratoarelor cu p. Diagramele de semnal (figura 4.x) indica o divizare initiala cu 5, urmata de schimbarea raportului si o divizare cu 8.

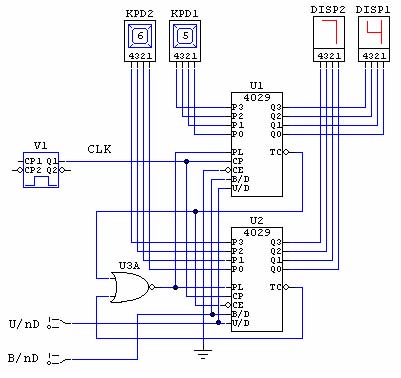

Cel de-al treilea exemplu de divizor programabil de frecventa este si cel mai versatil: utilizand doua numaratoare CMOS 4029 si incarcarea comandata de o poarta SAU-NU cu un numar de intrari egal cu numarul de circuite 4029 utilizate, circuitul ofera:

-numarare in sens crescator, de la p la 255 (U/nD = 1);

-numarare in sens descresator, de la p la 0 (U/nD = 0);

-numarare binara (B/nD = 1);

-numarare zecimala (B/nD = 0).

Intrebare: Specificati unde se afla iesirea divizorului din figura x si forma semnalului divizat.

5. APLICATIILE NUMARATOARELOR

Tabelul x

Sinteza principalelor tipuri de numaratoare

|

Tip numarator |

Front |

Reset |

Load |

TTL |

CMOS |

Observatii, comentarii |

||||

|

Cod |

n |

Cod |

n | |||||||

|

A, H |

74LS293 | |||||||||

|

Asincron |

A, H |

74LS393 |

2 x 74LS293 intr-o capsula | |||||||

|

binar |

|

A, H |

Disponibile iesirile Q0, Q3-Q13 | |||||||

|

direct |

A, H |

Disponibile toate iesirile Q0-Q11 | ||||||||

|

A, H |

Iesiri Q3-13, oscilator intern, RC extern | |||||||||

|

Asincron |

74LS290 |

Zecimal, reset activ SUS | ||||||||

|

BCD |

74LS390 |

2 x 74LS293 intr-o capsula | ||||||||

|

direct | ||||||||||

|

A, L |

S, L |

74LS161 | ||||||||

|

Sincron |

S, L |

S, L |

74LS163 | |||||||

|

binar |

A, H |

A,H | ||||||||

|

direct |

↑sau ↓ |

A, H |

2 numaratoare intr-o capsula | |||||||

|

Sincron BCD direct |

↑ ↑ ↑ ↑sau ↓ |

A, L S, L A, H A, H |

S, L S, L A, H - |

74LS160 74LS162 |

2 numaratoare intr-o capsula | |||||

|

Universale |

A, L |

Reversibil, BDC / binar, fara stergere | ||||||||

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 7834

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2024 . All rights reserved