| CATEGORII DOCUMENTE |

Circuite numaratoare

In lucrarile precedente au fost prezentate notiunile fundamentale care descriu functionarea circuitelor combinationale (porti logice, porti de transmisie si multiplexoare) precum si celulele elementare ale circuitelor secventiale (bistabilele D si JK). Sistemele digitale se constituie ca o combinatie intre aceste doua clase de circuite: blocurile combinationale stabilesc relatii matematice intre diferitele intrari si iesiri ale circuitelor secventiale.

Numaratoarele constituie o clasa importanta a aplicatiilor cu circuite bistabile si sunt utilizate in sistemele secventiale in care se doreste incrementarea succesiva a unor valori binare sau zecimale. Fiecare din semnalele de iesire ale numaratorului (reprezentand unul din bitii semnalului generat) se repeta periodic dupa un multiplu al perioadei de ceas, astfel incat un circuit numarator poate fi privit in ansamblul sau si ca un divizor al frecventei semnalului de ceas.

Obiective

Obiectivul lucrarii de fata este prezentarea detaliilor de proiectare a circuitelor numaratoare sincrone si asincrone implementate in tehnologia CMOS. Este pus un accent deosebit pe compromisurile intre viteza de numarare si complexitatea circuitului, compromisuri care trebuie acceptate in proiectarea structurilor numaratoare performante.

Fundamentarea teoretica

Toate structurile digitale care utilizeaza celule bistabile au proprietatea comuna de a impune o corelare temporala a semnalelor de circuit; astfel, pentru o functionare corecta a unui sistem secvential este necesara o ordine bine definita a evenimentelor de comutare asociate intrarilor si iesirilor circuitelor bistabile. In caz contrar celulele bistabile ar putea fi inscrise cu biti gresiti. Cea mai des implementata metoda de a determina comutarea simultana a elementelor bistabile este utilizarea unui semnal de sincronizare, periodic, distribuit tuturor celulelor din circuit. Frecvent, acest semnal este numit semnal de sincronizare sau de ceas pentru ca este si semnalul cu cea mai mare frecventa din circuit. Functionalitatea intregului sistem este asigurata prin comutari ale iesirilor circuitelor bistabile simultan cu unul din fronturile semnalului de ceas. Aceste circuite se numesc sincrone datorita dependentei temporale intre semnalele de circuit si semnalul global de sincronizare.

O alta abordare posibila ce asigura functionarea corecta a circuitelor secventiale este aceea prin care se impune o corelare in timp a evenimentelor de comutare cu semnale care determina tranzitiile respective; se elimina in acest fel nevoia pentru semnale de referinta externe, iar circuitele rezultate se numesc asincrone. In cele ce urmeaza sunt prezentate detalii de proiectare atat pentru circuitele numaratoare sincrone cat si pentru cele asincrone, urmarind a pune in evidenta avantajele si dezavantajele celor doua categorii de circuite.

Numaratoare sincrone

Numarator crescator (count up)

Un numarator binar sincron numara de la 0 la 2n-1, unde n reprezinta rezolutia numaratorului si indica numarul de biti pe care se exprima numerele generate. Cum circuitele bistabile pot fi asociate unor celule de memorie controlate prin semnalele de comanda (R si S, J si K) iar fiecare astfel de celula elementara memoreaza un bit, putem spune ca rezolutia numaratorului este egala cu numarul de bistabile. Astfel, fiecare bistabil din structura circuitului numarator reprezinta un bit. Procesul prin care valorile numerice generate (in format binar) se incrementeaza crescator se implementeaza conform urmatorului algoritm: bistabilul ce reprezinta cel mai putin semnificativ bit (bistabilul LSB) complementeaza iesirea Q la fiecare perioada a semnalului de ceas, iar bistabilele de ordin superior comuta iesirea doar daca iesirile Q ale bistabilelor corespunzatoare bitiilor de ordin inferior sunt "1".

Spre exemplu, numarului q3q2q1q0=0011 ii urmeaza valoarea q3q2q1q0=0100: q0 se complementeaza la fiecare perioada de ceas (pe front crescator sau descrescator), q1 se complementeaza pentru ca toti bitii de rang inferior sunt "1" (in acest caz doar q0), iar q2 se complementeaza pentru ca bitii de rang inferior (q0 si q1) sunt "1". Schema unui numarator sincron crescator este prezentata in figura F6.1.

Figura F6.1. Numarator sincron crescator, varianta 1

Din schema precedenta observam ca desi circuitul este sincron conform principiului enuntat anterior, exista un timp de propagare asociat portilor SI care determina ca intrarile de comanda ale bistabilelor sa nu fie aplicate simultan cu frontul descrescator al semnalului de ceas. Aceasta intarziere contribuie semnificativ la degradarea timpului de propagare necesar pentru generarea semnalelor asociate fiecarei iesiri de bistabil, timp direct proportional cu numarul de biti ai numaratorului. O solutie partiala pentru aceasta problema este data de utilizarea unor porti SI cu intrari multiple, asa cum este prezentat in figura F6.2. Aceasta solutie elimina dezavantajul conectarii in cascada a unui numar (mare) de porti SI, dar introduce, la randul sau, alte probleme de proiectare: prima o constituie numarul de intrari al portilor SI asociate bitilor de rang superior (fan-in crescator liniar cu rezolutia numaratorului), iar a doua este data de numarul intrarilor de porti conectate la o singura iesire a unui bistabil de ordin inferior (fan out pentru bistabil). De exemplu, pentru un numarator pe 12 biti, poarta SI corespunzatoare bistabilului MSB are un fan-in egal cu 11, iar bistabilul LSB are un fan-out de 10. Spre comparatie, in primul caz fiecare bistabil avea un fan-out de 1, iar portile un fan-in egal cu 2. Este evident faptul ca pentru numaratoare pe multi biti ambele metode sunt deficitare in ceea ce priveste timpul de propagare prin structurile combinationale SI.

Un compromis intre cele doua metode poate oferi o solutie in cazul numaratoarelor pe multi biti: pentru exemplul numaratorului de rezolutie 12, putem organiza bistabilele in 3 grupe a cate 4 astfel incat in cadrul fiecarui grup de 4 sa utilizam porti cu intrari multiple, iar cele trei grupe sa fie conectate prin porti cascadate.

Figura F6.2. Numarator sincron crescator, varianta 2

Numarator descrescator (count down)

In cazul numaratoarelor binare crescatoare, un bit (cu exceptia LSB) isi schimba valoarea daca toti bitii de ordin inferior sunt "1"; pentru numaratoarele descrescatoare este valabil cazul opus: un bit arbitrar (cu exceptia LSB) isi schimba valoarea daca toti bitii de ordin inferior sunt "0". Dupa numarul q3q2q1q0=0100 urmeaza numarul q3q2q1q0=0011: q0 se complementeaza la fiecare perioada de ceas, q1 si q2 se complementeaza pentru ca toti bitii de ordin inferior sunt "0". Implementarea la nivel de schema cu bistabile a unui numarator descrescator (F6.3) este similara cu varianta pentru numaratorul crescator, doar ca se utilizeaza iesirea negata a fiecarui bistabil.

Figura F6.3. Numarator sincron descrescator

Numarator reversibil (count up/down)

Asemanarile dintre cele doua tipuri de numaratoare descrise anterior conduc la ideea implementarii unui circuit capabil sa numere fie crescator, fie descrescator, in functie de un bit de comanda MS (Mod Select). Diferenta dintre cele doua tipuri de numaratoare consta doar in alegerea iesirii bistabilului, astfel ca se utilizeaza doua porti SI pentru a face selectia intre cele doua iesiri. Logica SAU permite ca iesirea bistabilului care a fost selectata sa se constituie in comanda pentru bistabilul de ordin superior (F6.4).

Figura F6.4. Numarator sincron reversibil pe trei biti

Numarator in inel

Numaratorul in inel implementeaza principiul unui registru de deplasare seriala, in care iesirea ultimului bistabil (LSB) este conectata la intrarea primului bistabil (MSB). Este uzual ca doar un bit "1" sa treaca de la un bistabil la altul, atunci cand semnalul de ceas este HIGH. Figura F6.5 prezinta un numarator in inel pe patru biti. Daca presupunem ca pornim din starea q3q2q1q0=1000, la primul puls de ceas bitul "1" trece la q2 iar numaratorul se gaseste in starea q3q2q1q0=0100. In urmatoarele doua perioade de ceas circuitul trece prin starile q3q2q1q0=0010 si q3q2q1q0=0001, dupa care se revine la starea initiala. Pentru fiecare din perioadele ulterioare in care semnalul de ceas este HIGH, bitul "1" care trece de la o iesire de bistabil la alta determina ca starile circuitului sa se repete.

Figura F6.5. Numarator sincron in inel

Trebuie remarcat faptul ca un numarator in inel utilizeaza mai multe bistabile pentru acelasi numar de stari, in comparatie cu numaratorul binar: pentru valori pe patru biti, numaratorul in inel trece prin 4 stari distincte, in timp ce un numarator binar ofera la iesiri toate cele 16 combinatii posibile. Avantajul numaratoarelor in inel este dat de lipsa vreunei structuri combinationale care sa decodeze iesirea unui bistabil pentru a genera comanda bistabilului urmator. Pentru ca numaratorul in inel sa functioneze este necesara inscrierea unui bit "1" in unul din bistabilele cascadate. Circuitul trebuie sa treaca printr-o faza de initiere prin aplicarea unui impuls preset unuia dintre bistabile si clear celorlalte. Acest lucru presupune existenta unor pini de control suplimentari la fiecare bistabil.

Un caz particular al numaratorului in inel este numaratorul Johnson. Cele doua circuite sunt aproape identice; exceptie face conexiunea dintre bistabilul corespunzator MSB si cel corespunzator LSB: la intrarea primului bistabil se conecteaza iesirea negata a ultimului bistabil. Circuitul este prezentat in figura F6.6. Pornind de la starea initiala q3q2q1q0=0000, la primul impuls de ceas in bistabile vom avea inscrise valorile 1000, la al doilea impuls valorile 1100, urmand ca circuitul sa treaca succesiv prin starile 1110, 1111, 0111, 0011, 0001. Pentru o valoare prestabilita a numarului de biti din numarator (n), numaratorul binar trece prin toate cele 2n combinatii posibile, numaratorul in inel prin n stari distincte, iar numaratorul Johnson prin 2n stari distincte.

Figura F6.6. Numarator Johnson

Atunci cand se impune un anumit numar de tranzitii distincte, numaratorul Johnson reprezinta un compromis intre numaratorul binar si cel in inel in ceea ce priveste numarul ce celule bistabile. De asemenea, logica de decodare a starilor este mai simpla decat cea corespunzatoare numaratorului binar, insa mai complicata fata de cazul unui numarator in inel (numaratorul in inel nu are logica de decodare, insa decodarea starilor peste care sare un numarator Johnson se implementeaza cu porti SI cu doua intrari).

Numaratoare asincrone

Circuitele numaratoare asincrone au caracteristic faptul ca celulele bistabile din structura lor nu sunt comandate cu un semnal de ceas comun. Comutarea iesirii unui bistabil are loc la comanda primita de la iesirea bistabilului de rang inferior, in timp ce primul bistabil este comandat de un eveniment logic extern (care poate fi si unul repetitiv, cu proprietati similare unui semnal de ceas). Datorita modului de conectare al elementelor bistabile, numaratoarele asincrone se mai numesc si numaratoare cu propagarea comenzii. Un astfel de circuit pe patru biti este prezentat in figura F6.7.

Se poate observa din figura precedenta ca un numarator asincron nu implica (in cazurile putin complicate) utilizarea unor structuri logice aditionale. Insa desi este mai simplu de proiectat, exista o serie de dezavantaje asociate acestui circuit:

viteza numaratorului cu propagarea comenzii este mai mica fata de cea a numaratoarelor sincrone, pentru numaratoare pe multi biti; intr-un numarator sincron toate celulele bistabile comuta simultan, pe cand intarzierea structurii asincrone este data timpul necesar propagarii comenzii prin lantul de bistabile.

interconectarea circuitelor asincrone in sistemele digitale complexe (in marea lor majoritate sincrone) ridica dificultati de proiectare si interfatare din punct de vedere al corelatiei temporale a semnalelor.

Figura F6.7. Numarator asincron pe patru biti

Optimizarea vitezei circuitelor numaratoare sincrone

In practica, circuitele numaratoare utilizate in aplicatiile de mare viteza sunt implementate in conformitate cu schemele principiale prezentate in F6.8a si F6.8b. Cele doua circuite reprezinta numaratoare crescatoare cu transport serial, respectiv paralel a comenzii de numarare. Circuitele sunt formate din celule bistabile T (bistabile JK cu comanda comuna "1") care au o intrare suplimentara (EN, enable) ce activeaza/dezactiveaza iesirea. Semnalul qi de pe pinul de iesire poate varia doar daca intrarea EN este HIGH. In cazul ambelor scheme se poate observa ca cel mai putin semnificativ bit se complementeaza la fiecare front pozitiv de ceas, iar bitii de rang superior se complementeaza doar daca bitii anteriori sunt "1". Deosebirea importanta dintre cele doua structuri este modalitatea prin care semnalul CEN (count enable) se propaga de la un bistabil la altul (traseele punctate). Pentru structura cu transport serial, semnalul CEN se transmite ca urmare a unei conexiuni seriale de la o poarta SI la cea adiacenta superior; pentru circuitul cu transport paralel, comanda CEN se transmite prin intermediul iesirii bistabilului de rang inferior.

Figura F6.8. Numaratoare cu transport serial (a) si paralel (b), scheme principiale

Circuitul cu transport paralel este mai rapid, iar diferenta de viteza este data de timpul necesar propagarii semnalului CEN; considerand o tranzitie a iesirii q0 de la "0" la "1" ca urmare a activarii comenzii CEN, pentru structura cu transport serial este necesar un timp de propagare mai mare pentru transmiterea modificarii bitului, timp dat de propagarea bitului q0 prin trei porti SI cascadate. Pentru schema cu transport paralel intarzierea este asociata timpului de propagare printr-o singura poarta SI. Rezulta astfel ca perioada minima a semnalului de ceas poate fi mai mica in acest al doilea caz, iar circuitul poate opera la frecvente mai mari. In aplicatii de mare viteza (cum ar fi numaratoarele din familiile XC3000, XC3100 sau XC4000 produse de Xilinx ) circuitele dezvoltate pe schema principiala cu transport paralel ofera cele mai bune performante. Structura cu transport paralel prezinta si unele limitari deosebit de importante atunci cand se doreste implementarea unor circuite numaratoare pe mai multi biti (mai mult de 7-8 biti). Aceste aspecte au fost subliniate si in paragraful 1.2.1.1:

iesirea bistabilului de rang i trebuie sa comande n-i porti logice, unde i<n (n este rezolutia numaratorului); cel mai defavorabil caz este pentru bistabilul corespunzator LSB care are un fan-out egal cu n-1. Este necesar ca circuitul bistabil sa furnizeze la iesire un curent suficient de mare pentru a avea putere de comanda asupra tuturor intrarilor de porti ce formeaza parametrul fan-out.

numarul de intrari ale portilor SI necesare creste cu cresterea rezolutiei n; cel mai defavorabil caz este pentru poarta de rang MSB care are n intrari. Acest aspect devine problematic odata cu cresterea rezolutiei n. In acest caz se prefera utilizarea unui arbore de porti cu 2-3 intrari a carui functionalitate sa fie echivalenta cu cea a portii cu fan-in mare.

Desi structura cu transport serial este mai putin rapida, nu prezinta dezavantajele mentionate anterior referitoare la parametrii fan-in si fan-out ai portilor/bistabilelor si permite implementarea unor circuite numaratoare cu rezolutie mai mare. In combinatie cu alte tehnici de optimizare a vitezei, aceasta alternativa poate oferi cea mai buna solutie pentru numaratoare foarte lungi.

Gasirea unei solutii acceptabile pentru problemele mentionate reprezinta compromisul care trebuie acceptat intre complexitatea logicii combinationale si viteza maxima a numaratorului. Este util ca in proiectarea circuitelor optimizate pentru operare la frecvente inalte sa se adere la regula conform careia un circuit trebuie proiectat nu pentru viteza maxima, ci pentru viteza corecta (optima).

Desfasurarea lucrarii

Propagarea semnalelor in numaratoarele asincrone

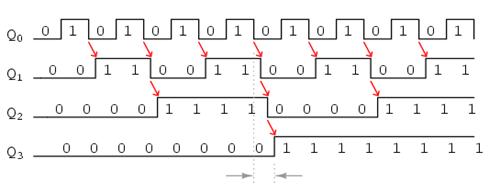

Structurile de numaratoare asincrone au dezavantajul acumularii intarzierilor de propagare intre celulele bistabile, efect care este cu atat mai pronuntat cu cat numarul de bistabile cascadate este mai mare. Optimizarea caii critice de propagare prin reducerea numarului de bistabile nu este o solutie, deoarece in acest fel se reduce corespunzator si numarul de biti ai numaratorului. Efectul de "riplu" (intalnit si in cazul circuitelor aritmetice sumatoare cu propagarea bitului carry) afecteaza functionarea structurii numaratoare prin introducerea unor intarzieri ce pot fi inacceptabile in unele aplicatii. Figura F6.9 prezinta acest efect asupra semnalelor de iesire ale numaratorului.

Figura F6.9. Efectul intarzierilor de propagare pentru numaratoare asincrone

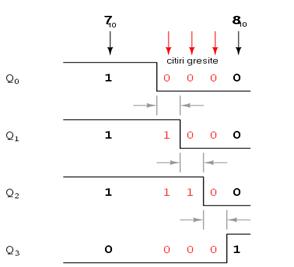

Se observa ca bistabilele nu comuta toate simultan. Timpul de propagare necesar semnalului de comanda (tranzitia din "1" in "0" a iesirii bistabilului anterior) sa determine comutarea iesirii se acumuleaza, iar efectul este comutarea iesirii unui bistabil de rang superior mult dupa ce comanda a fost primita. Modul in care intarzierea cumulata afecteaza valorile binare generate de numarator este pus in evidenta daca presupunem ca semnalul de iesire q3q2q1q0 este citit imediat dupa comutarea unui bistabil de rang intermediar; figura F6.10 evidenteaza valorile gresite generate in cazul in care iesirea numaratorului se citeste prea repede.

Pentru un numarator asincron pe 12 biti, studiati efectul cumularii intarzierilor partiale asupra semnalelor de iesire generate. Determinati care este timpul minim necesar pentru ca iesirea circuitului sa se stabilizeze, presupunand ca la intrarea bistabilului corespunzator bitului LSB se aplica un semnal repetitiv.

Figura F6.10. Erori generate la functionarea numaratoarelor asincrone

Propagarea semnalelor in numaratoarele sincrone

Pentru verificarea functionalitatii numaratoarelor sincrone se va utiliza bistabilul JK master slave proiectat in cadrul aplicatiilor lucrarii de laborator 4. Sa se proiecteze un numarator sincron crescator, pe opt biti, cu transport serial, corespunzator schemei de principiu din figura F6.1. Studiati modul in care intarzierile datorate timpilor de propagare prin structurile combinationale SI afecteaza functionarea corecta a circuitului. Masurati intarzierea semnalelor q0, q4 si q11 fata de frontul activ al semnalului de ceas care determina comutarile acestor semnale. Explicati in ce conditii numaratorul poate genera valori gresite datorita intarzierilor de propagare. Determinati frecventa maxima a semnalului de ceas pentru care numaratorul pe 12 biti functioneaza corect.

Intrebari si probleme

Verificati corectitudinea circuitului din figura F6.1 pentru un numarator pe patru biti pornind de la diagrama de tranzitii si tabelul de adevar corespunzator implementarii cu bistabile JK.

Desenati schema de principiu la nivel de porti logice a bistabilelor JK si D cu pini Preset si Clear.

Determinati schema electrica la nivel de porti logice a unui numarator reversibil, asincron, pe patru biti.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 6876

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved