| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

la CEF

Elemente de tehnologie de fabricatie

Inceputul anilor 1980 a insemnat trecerea de la tehnologia bipolara la cea unipolara,in special la cea CMOS. Incepand cu anii 1990,aproape in exclusivitate,circuitele integrate produse au fost CMOS. Schimbarea de tehnologie s-a produs cand au aparut circuitele pe scara larga VLSI,cand tehnologia bipolara nu mai era corespunzatoare,alternativa fiind tehnologia CMOS.

Tehnologia de fabricatie a circuitelor CMOS necesita ca tranzistoarele de tip canal n (nMOS) si cele de tip canal p (pMOS) sa fie realizate pe acelasi substrat al circuitului. Pentru a alatura ambele dispozitive nMOS si pMOS, trebuie create regiuni in care tipul semiconductorului sa fie opus tipului substratului. Aceste regiuni sunt numite insule, fantani (wells) sau tuburi (tubes) O insula de tip p este creata pe un substrat de tip n sau, alternativ, o insula de tip n este creata pe un substrat de tip p. In tehnologia de fabricatie n-well CMOS prezentata, tranzistorul nMOS este creat pe substratul de tip p,iar tranzistorul pMOS este creat in insula de tip n(n-well) care este construita pe substratul p.

Procesul incepe prin crearea unor regiuni insula de tip n (n-wells) pentru tranzistoarele pMOS prin implantarea de impuritati in substrat. Apoi un strat subtire de oxid este realizat in zonele care inconjoara regiunile active nMOS si pMOS. Poarta subtire de oxid este realizata prin oxidare termica. Acesti pasi sunt urmati de crearea unor regiuni p+ si n+ (implantari sursa, drena si canal-stop) si la final metalizare (crearea de interconexiuni metalice)

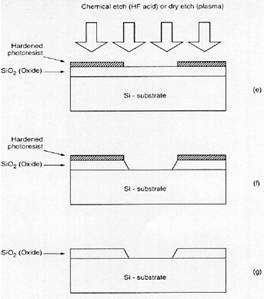

Figura-1: Secventa simplificata a procesului de fabricatie a circuitului integrat CMOS n-well (cu insule de tip n) cu un singur strat de polisiliciu, prezentand doar pasii importanti de fabricati

Fiecare dintre pasii de proiectare are nevoie ca pe pastila sa fie definite anumite regiuni cu masti adecvate. Prin urmare, circuitul integrat poate fi vazut ca o multime de straturi de siliciu, polisiliciu, difuzie, metal si dioxid de siliciu, de forme diferite si cu proprietati electrice diferite. Pentru fiecare strat, care se creaza pe pastila, trebuie realizat un sablon, o masca.

Unul dintre procedeele de transfer al unei masti pe un strat al circuitului se numeste litografiere. Deoarece fiecare strat are propriile cerinte pentru transpunerea mastilor, secventa de litografiere trebuie repetata pentru fiecare strat, folosind o masca diferita.

Figura.2: Pasii de proiectare pentru partitionarea cu dioxid de siliciu.

Reguli de proiectare

Proiectarea mastilor pentru un circuit dat, folosind un procedeu particular, trebuie sa respecte un set de restrictii geometrice sau reguli numite in general reguli de proiectare.

Aceste reguli specifica de obicei dimensiunea minima a liniilor pentru obiectele fizice de pe pastila cum ar fi traseele de metal si polisiliciu sau zonele de difuzie, dimensiunile minime ale formelor si dimensiunile minime de separare intre doua forme.

Daca un traseu metalic este prea subtire, de exemplu, este posibil ca traseul sa cedeze in procesul de fabricatie sau dupa aceea, rezultand un circuit deschis. Daca doua trasee sunt plasate prea aproape unul de cealalt pot forma un nedorit scurt-circuit prin contopire in timpul procesului de fabricatie sau dupa.

Obiectivul principal al regulilor de proiectare este acela de a se atinge o productivitate si o calitate generala bune, folosind cea mai mica arie posibila de siliciu, pentru orice circuit realizat cu o tehnologie particulara.

De observat ca exista o contradictie intre o productivitate mai ridicata, care se obtine prin geometrii conservative, si o mai buna densitate (folosirea suprafetei de Si) obtinuta prin plasarea cu densitate ridicata a obiectelor pe pastila. Regulile de proiectare specificate pentru o tehnologie particulara reprezinta un optim rezonabil in termeni de productivitate si densitate.

Trebuie mentionat, totusi, ca regulile de proiectare nu reprezinta limite stricte, care separa proiectarile corecte de cele incorecte. Un proiect care nu respecta unele din regulile specificate poate conduce totusi la un circuit operational cu productivitate rezonabila, pe cand un alt proiect care respecta toate regulile poate sa conduca la un circuit, care nu este functional sau care are o productivitate foarte scazuta. In rezumat, respectand regulile de proiectare creste considerabil probabilitatea fabricarii unui produs de succes, cu productivitate ridicata.

Regulile de proiectare sunt specificate de obicei in doua moduri:

Reguli micronice, in care restrictiile sunt specificate in termeni absoluti, ca dimensiuni in micrometri;

Reguli Lambda, care specifica restrictiile de proiectare in termenii unui singur parametru (lambda) cu care se scaleaza proportional toate restrictiile geometrice.

Regulile Lambda au fost propuse initial pentru a simplifica regulile de proiectare micronice industriale si a permite scalarea diferitelor procese. Se poate mentiona ca majoritatea proceselor CMOS submicronice nu sunt usor de cuprins intr-o scalare liniara. Regulile Lambda trebuie folosite cu precautie in geometriile submicronice.

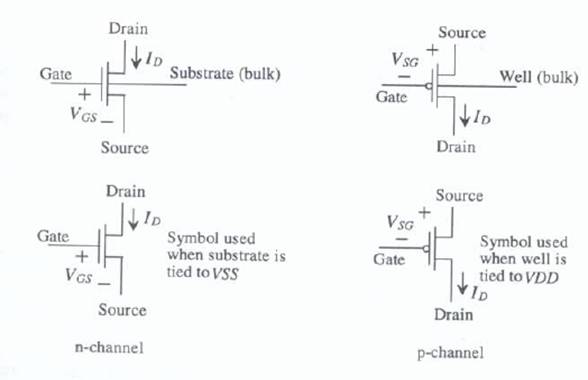

Simboluri

Cand substrat-ul este legat la VSS si fantana este conectata la VDD se utilizeaza modelele simplificate, afisate in partea de jos a figurii. Este important sa retinem ca tranzistorul MOS este un aparat cu 4 terminale si ca sursa si drena sa sunt interschimbabile.

Figura-3: Simboluri utilizate pentru tranzistoare MOS cu canal n si p

Zone de lucru si caracteristicile specific

In cele ce urmeaza va fi examinata functionarea tranzistorului zona de saturatie si in cea de trioda facand trimitere si la o a treia zona, zona de taiere.

Zona de trioda

Consideram figura 5.9, unde Vgs > VTHN , astfel incat suprafata de sub oxid este intoarsa si VDS > 0 , provocand scurgerea unui curent de drift intre drena si sursa. In analiza initiala, vom considera VDS suficient de mic incat tensiunea de prag si grosimea suprafetei de scurgere sa fie aproximativ constante.

Trebuie initial sa gasim sarcina incarcata pe capacitatea oxidului,C'ox. Voltajul, conform sursei tranzistorului CMOS, a canalului la o distanta y fata de sursa este notat V(y).Diferenta de potential intre electrodul portii si canal este apoi VGS -V(y).Raportul sarcina pe unitatea de arie in stratul inversat este dat de:

Q'ch=C'ox VGS-V(y)]

Stim ca o sarcina Q'b este prezenta in stratul inversat de la aplicarea tensiunii de prag, VTHN , necesara pentru transmiterea intre drena si sursa.Aceasta sarcina este data de: Q'b=C'oxVTHN

Sarcina totala din canal disponibila pentru transmiterea unui curent intre drena si sursa este determinata de diferenta acestor doua ecuatii sau:

Q'1(y C'ox(VGS-V(y)-VTHN)

unde Q'1 este sarcina din canalul inversat.

Fig 5.9. calculul comportamentului caracteristicii in regiunea de trioda

Diferentiala rezistentei unei regiuni de canal cu lungimea dy si grosimea W este data de :

unde n este media mobilitatii electronului prin canal avand unitatea de masura cm2/Vsec. Mobilitatea este doar un raport al vitezei electronului cm/sec,in campul electric V/cm. Acest parametru este folosit in modelul de parametrii BSIM, pentru a potrivi cele 4 curbe ale modelului SPICE la rezultatele masurate. De asemenea, pentru dispozitivele cu canal scurt mobilitatea descreste cand viteza purtatorilor incepe sa se satureze. Acest lucru cauzeaza cresterea stratului efectiv al rezistentei din ecuatia de mai sus, rezultand intr-o scadere a curentului de drena.

Diferentiala tensiunii in functie de diferentiala rezistentei este:

![]()

sau substituind Q'1(y) din ecuatiile de mai sus si rearanjand obtinem ecuatia:

IDdy=WnC'ox(VGS-V(y)-VTHN)dV(y)

Acum putem defini un nou parametru pentru MOSFET: transconductanta. Pentru un MOSFET cu canal-n, acest parametru este dat de:

![]() ,si pentru un MOSFET

cu canal-p, este data de:

,si pentru un MOSFET

cu canal-p, este data de:

![]() , unde p este

mobilitatea deschizaturilor intr-un tranzistor P-MOS. Valori tipice ale KP in

procesul CN20 sunt 50A/V2

pentru cele cu canal-n si 17A/ V2 pentru tranzistoarele cu canal-p.

, unde p este

mobilitatea deschizaturilor intr-un tranzistor P-MOS. Valori tipice ale KP in

procesul CN20 sunt 50A/V2

pentru cele cu canal-n si 17A/ V2 pentru tranzistoarele cu canal-p.

Curentul poate fi obtinut integrand partea stanga a ecuatiei IDdy=WnC'ox(VGS-V(y)-VTHN)dV(y), de la sursa la drena, adica de la 0 la L, si partea dreapta de la 0 la VDS.Acest lucru este aratat in continuare :

![]()

sau

![]() .

.

Aceasta ecuatie este valida cand tranzistorul MOSFET opereaza in regiunea de trioda. Acest lucru in cazul cand canalele induse se extind de la sursa la drena. In plus putem rescrie ultima ecuatie definind urmatorul parametru al transconductantei:

![]()

sau :

![]() .

.

Ecuatia echivalenta pentru un MOSFET cu canal-p operand in regiunea de trioda este:

![]()

unde tensiunea de prag a MOSFET-ului cu canal-p este luata ca fiind pozitiva.

Toate tensiunile din ultimele 4 ecuatii sunt pozitive.

Zona de saturatie

Tensiunea V(L) din ecuatia

![]()

este VDS intotdeauna mai mic decat diferenta VGS - VTHN,deci de-a lungul canalului se afla sarcina inversata 0. Cand VDS = VGS -Vthn, sarcina inversata subordonata grilei la L(jonctiunea drena canal) este 0.Aceasta tensiune drena sursa este numita VDS,sat (=VGS-VTHN),si indica momentul in care sarcina de canal devine taiata la interfata canalului de drena.

Cresterile tensiunii VDS nu cauzeaza o crestere a curentului de drena(vom vedea ca acest lucru nu este in totalitate adevarat. Un efect numit modularea lungimii canalului cauzeaza o crestere a curentului de drena cu cresterea tensiunii drena-sursa). Figura 5.10 arata ca zona de golire dintre drena si cresterile substratului duc la taierea canalului. Daca VDS este marita pana cand zona golirii substratului drenei se extinde de la drena la sursa si astfel se spune despre dispozitiv ca este taiat direct. In aceste conditii pot circula curenti mari cauzand probleme dispozitivelor.

Tensiunea maxima pentru lungimea canalelor aproape de valoarea minima,care poate fi aplicata intre drena si sursa MOSFET este reglata de tensiunea "punchtrough" (vezi Appendix A).Pentru canalele lungi,tensiunea maxima este setata de tensiunea de taiere(de frangere) a drenei(n+)implant/substrat dioda,specificata de asemenea in Appendix A.

Cand un

MOSFET functioneaza cu canalul lui taiat acesta este VDS ≥ VGS - VTHN si VGS ≥ VTHN, si opereaza in regimul de saturatie. Substitutia

lui VDS,sat in ecuatia ![]() produce:

produce:

Fig 5.10 CMOS in saturatie

Putem defini o lungime de canal electric a CMOS-ului ca diferenta dintre lungimea canalului de drena,neglijand difuzia laterala,si grosimea suprafetei de scurgere, Xd, intre drena n+ si canalul de sub oxidul de grila de

Lelec=Ldrawn-Xd.

Substituind in ecuatia de mai sus obtinem o mai buna reprezentare a curentului de drena:

![]()

Calitativ,acest lucru inseamna ca in timp ce grosimea suprafetei de scurgere creste cu cresterea VDS curentul de drena va creste la fel. Aceste efect este numit modularea lungimii canalului. Pentru a determina schimbarea in iesirea curentului cu tensiunea drena-sursa vom face derivata:

Valori tipice pt λc, numite parametrii modularii lungimii canalului,aranjate de la valori mai mari de 0.1 pentru dispozitivele cu canale scurte la 0.01 pt dispozitivele cu canale lungi. Ecuatia de mai sus a lui Id poate fi rescrisa luand in considerare modularea lungimii canalului ca:

![]()

Pentru aplicatii digitale vom lua λc=0, iar pentru aplicatii analogice, λc este masurat normal.

In figura 5.11 sunt aratate curbe tipice pentru un canal-n MOSFET. Se arata cum dispozitivele par sa intre in saturatie mai devreme decat e precizat de VDS = Vgs - VTHN.Actuala distributie de sarcina in canal este constanta ,ea este mai degraba o functie de VDS. Q'(y) descreste cu departarea de sursa MOSFET, cauzand Q'(L) sa devina 0 mai devreme(v. fig.5.10). Alt motiv,in special pentru dispozitivele cu canal scurt,la intrebarea de ce MOSFET devin saturate mai devreme, este ca mobilitatea nu este constanta; aceasta este viteza de saturatie pe deasupra unei tensiuni sigure VDS (relatata la campul electric si lungimea canalului),cauzand VDS,sat si IDS,sat sa scada. Aratate in Appendix A sunt curbele pentru ambele canale n si p ale MOSFET, cu marimile variind, impreuna cu tensiunea de prag si transconductanta parametrilor pentru MOSFET in procesul CN20, folosit pentru calcule.

Fig 5.11. caracteristicile curent tensiune

Zona de taiere

Se considera situatia in care tensiunea de grila depaseste tensiunea de prag, dispozitivul fiind in conductie, cu canalul format. Pentru valori mici ale lui VDS , atunci cand VDS < VGS - V tn , stratul de inversie se intinde de la sursa la drena. Dispozitivul lucreaza ca un rezistor variabil controlat de o tensiune.

Pe masura ce VDS creste , tensiunea intre poarta si drena scade, dar IDS inca are o crestere. Cand VDS =VGS -V tn campul electric E prezent la capatul dinspre drena si dielectricul portii se reduce la o asemenea valoare incat stratul de inversie nu mai este asigurat. In aceasta situatie se spune ca a avut loc taierea (pinch-off) canalului. Aceasta situatie este prezentata in figura de mai jos. Curentul de la drena la sursa este saturat si notat cu IDSAT .

O crestere in

continuare a tensiunii VDS fata de VDSAT conduce la

crearea unei zone fara inversie, ca in figura de mai jos.

Datorita proprietatii de continuitate IDS este egal cu IDSAT. Zona formata, dispunand de un

Caracteristica I-V a tranzistorului NMOS, cu canal indus, este data mai jos.

Modelul de semnal mic in zona de saturatie

Inainte de a consemna modelele de semnal mic pentru CMOS este indicat sa se reaminteasca cateva ecuatii esentiale.

Tensiunea de prag a unui CMOS cu canal n este data de:

![]() (9.1)

(9.1)

Curentul de drena in regiunea de saturatie,VDS>VGS-VTHN:

![]() (9.2)

(9.2)

unde λc este parametrul de modulare al lungimii canalului iar λm este parametrul de modulare al mobilitatii.

Definim β(=MUZ*C'OX*W/L=KP*W/L) astefel incat curentul de drena in regiunea de saturatie poate fi scris ca:

![]() (9.4)

(9.4)

unde am presupus ca VDS,sat este aproximativ 0 si λ=λc+λm. Curentul de drena al CMOS cu canal n in regiunea de trioda(VDS<VGS-VTHN) este dat de:

![]() (9.5)

(9.5)

Cand tranzistorul opereaza inaintea regiunii de prag,VGS<VTHN, curentul de drena, presupunand VDS>100 mV si VGS<VTHN-100mV este dat de:

![]() (9.6)

(9.6)

Cosideram circuitul din figura 9.1. Sursele de DC vor fi marcate cu litere mari si indici(ex VGS) si sursele de AC vor avea litere mici cu indici(ex. vgs). Suma componentelor continue si alternative vor fi marcate cu litera mica si indici mari(ex. vGS).

Fig. 9.1-determinarea transconductantei de inaintare

In fig 9.1 se arata ce se intampla cu curentul de drena cand aplicam o tensiune alternativa vgs. Presupunem in urmatoarele ca VGS>>vgs. Deoarece CMOS e in regiunea de saturatie, VDS>VGS-VTHN, iar curentul de drena(AC+ DC) este dat de :

![]() (9.7)

(9.7)

Transconductanta de iesire,gm, a CMOS este data de:

![]() (9.8)

(9.8)

Figura 9.2 ilustreaza un model de circuit ce foloseste acest rezultat.Remarcati ca sursele de cc au fost indepartate;acesta este o schema de semnal mic alternativ al CMOS.Putem sa ne imaginam TEC-MOS ca fiind SCCT sau un amplificator de transconductanta.

Fig. 9.2-schema de semnal mic alternative pt schema din fig. 9.1

Cand vgs devine comparabil in amplitudine cu VGS,variatia transconductantei poate fi remarcata in castigul amplificatorului.

Daca tensiunile

alternative sunt suficient de mici astfel incat vgs<<VGS si

produsul componentelor AC si DC ale tensiunii drena-sursa cu parametrii de

modulare este mai mic decat 1, ![]() ,

ecuatia (9.8) poate fi scrisa ca

,

ecuatia (9.8) poate fi scrisa ca

![]() (9.9)

(9.9)

Din fig 9.2 se observa ca, curentul AC RMS prin drena este dat de

![]() (9.10)

(9.10)

Transconductanta CMOS-ului ce opereaza inainte de regiunea de prag:

(9.11)

(9.11)

Impedanta de intrare este data de

![]() (9.12)

(9.12)

Conductanta tranzistorului inainitea regiunii de prag creste liniar cu ID,in timp ce atunci cand opereaza peste regiunea de prag,conductanta creste proportional cu ID. Modelul din fig 9.2 este utilizat atat pentru ambele cazuri(sub si peste prag).

Intre fiecare dintre cele 4 terminale ale CMOS exista o capacitate. Mai mult,valoarea fiecareia dintre aceste capacitate poate depinde de conditiile bias ale tranzistorului.

fig 2.30 Capacitatile MOS

Considerand structura din fig urmatoare (a),putem identifica urmatoarele:

Capacitatea dintre grila si canal C1=WLCox;

Capacitatea dintre canal si

substrat ![]() ;

;

Capacitatea datorata suprapunerii polisiliciului grilei cu zonele sursei si drenei, C3 si C4,insa acestea nu se pot scrie ca WLDCox,datorita marginirii liniilor de camp electric.

Capacitatea jonctiunii dintre sursa/drena si substrat. Dupa cum se poate vedea in fig (b),aceasta capacitate este impartita in 2 componente:Cj,capacitatea placii inferioare asociata cu partea inferioara a jonctiunii si Cjsw ,capacitatea lateral. Aceasta distinctictie e necesara datorita faptului ca diferite geometrii de tranzistor renunta la diferite valori ale perimetrilor pentru jonctiunea S/D

De obicei se specifica Cj si Cjsw ca o capacitate pe unitate de suprafata sau

lungime. De remarcat ca fiecare capacitate de jonctiune poate fi exprimata ca Cj=Cj0[1+VR/ФB]m unde VR este tensiunea inversa aplicata jonctiunii, ФB este potentialul jonctiunii,iar m este o putere,de obicei intre 0.3 si 0.4.

(a) (b)

Fig 2.31. (a) capacitatile MOS, (b) descompunerea capacitatii S/D

Modelul de semnal mic,frecvente inalte

Pentru a obtine modelul de frecvente inalte al CMOS,vom adauga capacitatile modelului de frecvente joase. Capacitatile dintre drena si sursa,notate Cdb si Csb, si capacitatea grilei asupra "field region",Cgb,in timp ce capacitatea dintre grila si drena este notata cu Cgd iar cea dintre grila si sursa cu Cgs.

Fig. 9.7 Schema de semnal mic la frecvente inalte

Consideram circuitul din fig. 9.8. Pentru ca potentialul pa capacitoarele Cdb si Csd este fix,putem sa le neglijam din analiza urmatoare de frecventa. Tensiunea alternative grila-sursa este data de:

iar transconductanta, presupunand gmvgs>>vgsjωCgd,este data de

![]()

unde gm0=id/vgs(0) este transconductanta la joasa frecventa.

Fig 9.8 circuit utilizat pentru determinarea dependentei frecventei de transconductanta de iesire

Fig 9.9 circuitul echivalent de semnal mic pentru 9.8

Castigul de current al CMOS-ului:

este definite ca fiind frecventa la care valoarea castigului de current a tranzistorului este unitara

sau

sau

Aceasta expresie neglijeaza timpul de trecere al purtatorilor prin canal, care, in general,este neglijabil.

Parametrii de maxim interes(in functie de zona de lucru)

Transconductanta:

Factorii de castig(A/V2)

Tensiunea de prag:

Gate threshold tensiunea este definita ca VTH=Vin si da aceeasi valoare a Vout

![]()

![]()

![]()

![]()

Corespondenta coduri parametrii (spice - teorie)

Parametrii sunt definiti mai jos

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2339

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved