| CATEGORII DOCUMENTE |

Laborator

Utilizarea mediului ActiveHDL pentru proiectarea, simularea si implementarea structurilor de calculatoare numerice

2. Prezentarea machetei de laborator cu circuitul hardware reconfigurabil FPGA Spartan 3 XC3S400FG456

Obiectiv: Laboratorul se constituie ca un indrumar pentru lucrul cu mediul de proiectare, simulare si implementare ActiveHDL pentru structuri de calculatoare numerice. Tot aici se va gasi si o prezentare a machetei de laborator care va fi folosita la implementari cu descrierea pinilor utilizati.

Atragem atentia ca toate etapele prezentate in acest laborator vor fi utilizate si in celelalte laboratoare deci este esentiala intelegerea acestora. Parcurgerea etapelor pentru proiectarea, simularea si implementarea circuitelor este obligatorie exact in ordinea in care sunt prezentate in cele ce urmeaza. Orice abatere de la aceasta ordine va avea drept urmare aparitia unor erori structurale sau functionale.

Desfasurarea lucrarii: Proiectarea unor circuite care sa fie apoi implementate pe structuri hardware reconfigurabile, de tipul FPGA, se face prin utilizarea unor medii speciale de proiectare. De regula, fiecare fabricant de circuite reconfigurabile furnizeaza si propriile instrumente software de sinteza si de implementare. Mediul de proiectare, simulare, implementare ActiveHDL realizat de firma Aldec permite selectarea instrumentelor software pentru sinteza si implementarea circuitelor logice in functie de fabricant, astfel incat acesta poate lucra cu o clasa foarte mare de circuite reconfigurabile. De asemenea acesta are trei metode prin care poate descrie circuitele logice: prin limbaj de descriere hardware, prin editarea schematica a circuitului sau prin masini de stare, pentru circuitele secventiale.

Dupa descrierea circuitului mediul ActiveHDL permite simularea comportamentului in timp a acestuia, astfel incat este posibila verificarea corectitudinii circuitului descris inainte ca acesta sa fie procesat pentru implementarea in FPGA.

Sinteza si implementarea sunt etapele care permit configurarea circuitului reconfigurabil selectat. Functionarea acestuia se testeaza folosind machetele de laborator.

Toate etapele prezentate mai sus vor fi parcurse de-a lungul laboratoarelor pentru proiectarea unor arhitecturi de structuri de calculatoare numerice, simularea comportamentului acestora si implementarea lor.

O parte din etapele prezentate in continuare se vor referi la un exemplu de circuit: dar pasii parcursi, asa cum am amintit, sunt universali valabili, indiferent de tipul circuitului.

Obiectivul este proiectarea unui sumator complet pe un bit, folosind editorul schematic din ActiveHDL. Apoi se doreste simularea acestuia si in ultima faza implementarea acestuia pe macheta pentru a se observa functionarea sa. Se vor citii fazele expuse in cele ce urmeaza si apoi se vor particulariza pentru sumator.

Crearea unui spatiu de lucru si a unui proiect pentru descrierea circuitului, simulare si implementare

Descrierea circuitelor logice folosind ActiveHDL

Exista mai multe metode pentru a descrie circuitele in ActiveHDL.

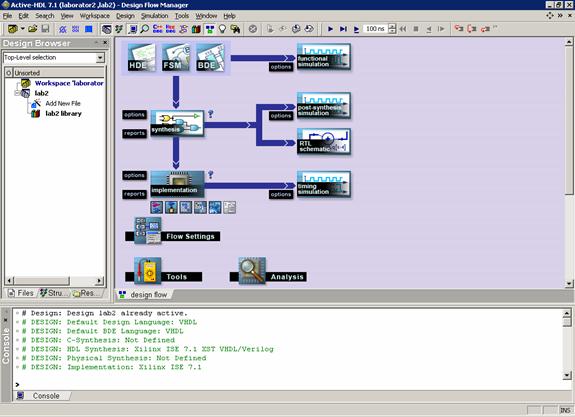

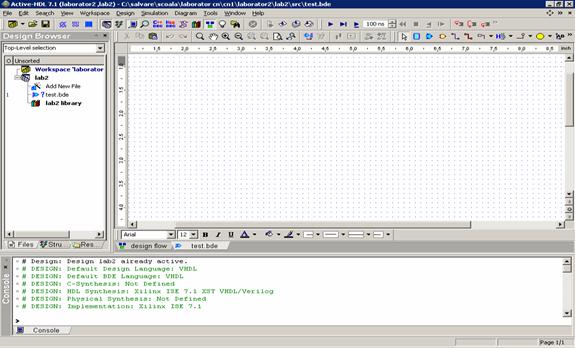

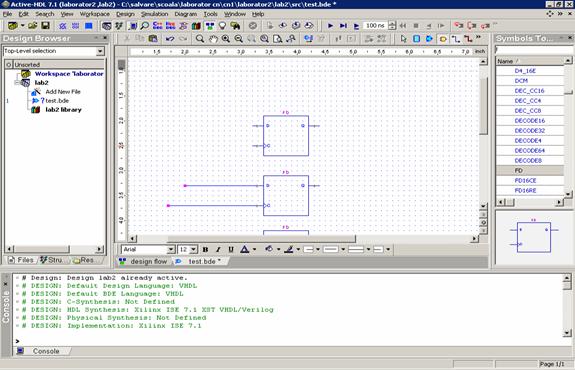

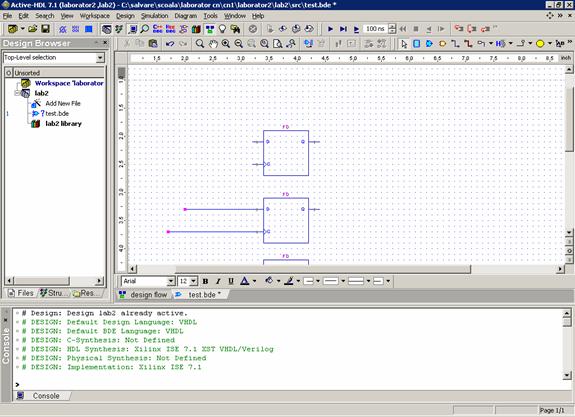

Dupa crearea proiectului si setarea optiunilor pentru lucrul cu macheta se observa fereastra principala de tipul celei de mai jos.

![]()

Pentru crearea unui fisier nou in proiect se selecteaza Add new file (inconjurat sus).

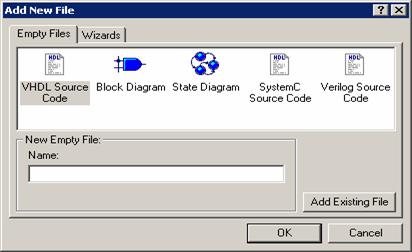

Exista mai multe metode pentru a descrie circuitele logice in ActiveHDL.

- descrierea folosind cod sursa: VHDL, Verilog sau SystemC sunt limbaje de descriere hardware. Lucrul cu acestea necesita cunostinte despre limbajul respectiv.

- descrierea folosind editorul schematic;

- descrierea folosind diagrame de stare.

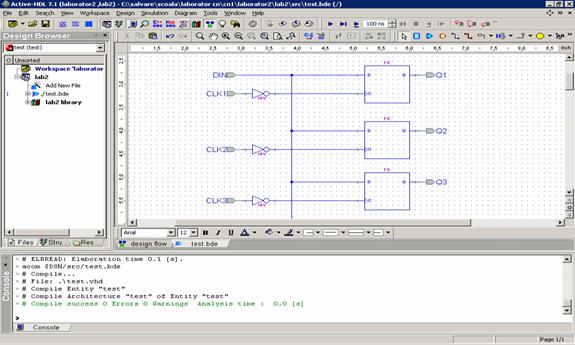

Pentru descrierea folosind editorul schematic se urmeaza urmatorii pasi:

- se selecteaza din fereastra AddNewFile optiunea BlockDiagram si se scrie un nume pentru circuit in campul Name:

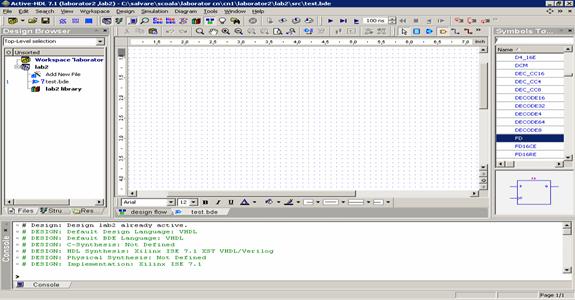

- se plaseaza componentele corespunzatoare accesand fereastra SymbolToolBox:

a) se apasa butonul cu pictograma corespunzatoare:

![]()

![]()

b) din fereastra care apare in partea dreapta se "trag" cu

ajutorul mouse-ului componentele dorite - fiecare componenta se

gaseste intr-o librarie (director). Atunci cand nu se

specifica altceva, componentele se vor lua din libraria Built-in

symbols:

b) din fereastra care apare in partea dreapta se "trag" cu

ajutorul mouse-ului componentele dorite - fiecare componenta se

gaseste intr-o librarie (director). Atunci cand nu se

specifica altceva, componentele se vor lua din libraria Built-in

symbols:

c) se efectueza legaturile intre componente folosind instrumentul Wire:

![]()

![]()

d) Se plaseaza terminalele circuitului:

![]()

![]()

Pentru redenumirea terminalelor se da dublu click pe terminal si astfel se obtine accesul la numele acestuia

e) Pentru reasezare componente, editare sau stergere se apasa instrumentul Select sau se apasa tasta ESC

![]()

f) dupa ce a fost descris circuitul se realizeaza compilarea schemei.

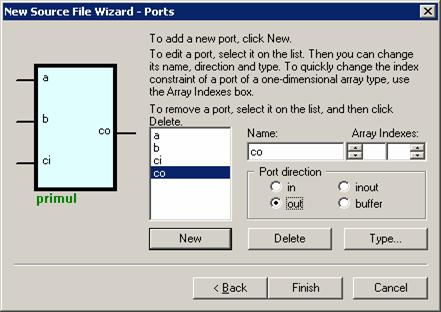

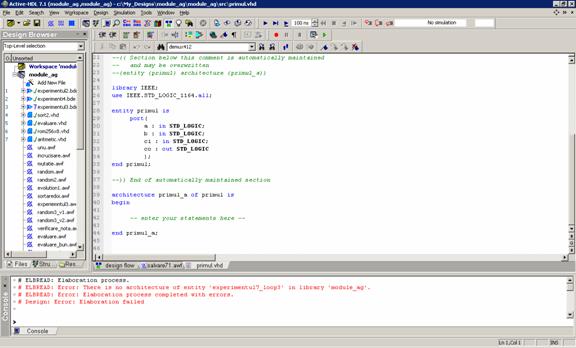

Pentru descrierea cu limbajul de descriere hardware VHDL se urmeaza urmatorii pasi:

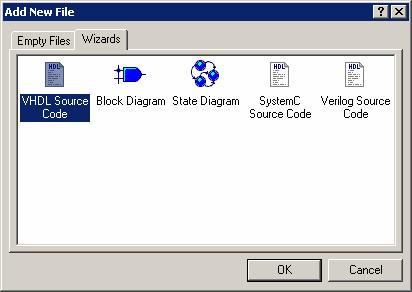

a) se selecteaza din fereastra AddNewFile tag-ul Wizards si optiunea VHDL Source Code si se apasa OK

b) urmatoarea fereastra se lasa neschimbata si se apasa Next

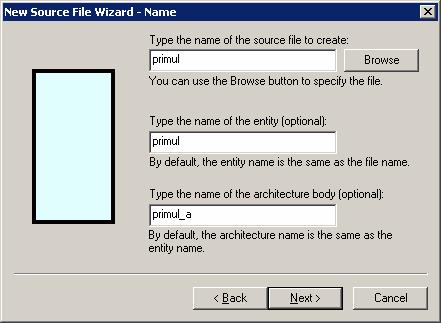

c) in fereastra urmatoare se scriu numele fisierului, numele entitatii si numele arhitecturii:

d) In fereastra urmatoare se apasa tasta New pentru introducerea porturilor circuitului. Se specifica directionalitatea acestora:

e) Se apasa butonul Finish, in acest moment pe ecran va fi creat un fisier template care contine declaratiile entitate, arhitectura si porturile declarate in entitate. Aici se va permite editarea ulterioara a programului VHDL. Dupa editare se va compila.

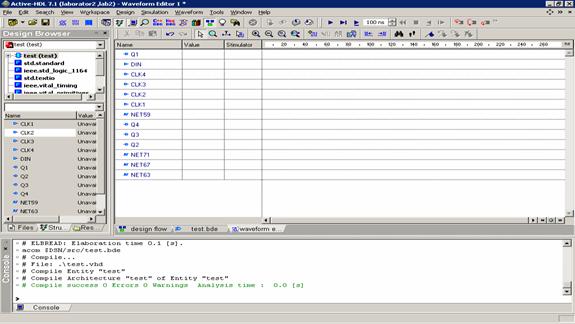

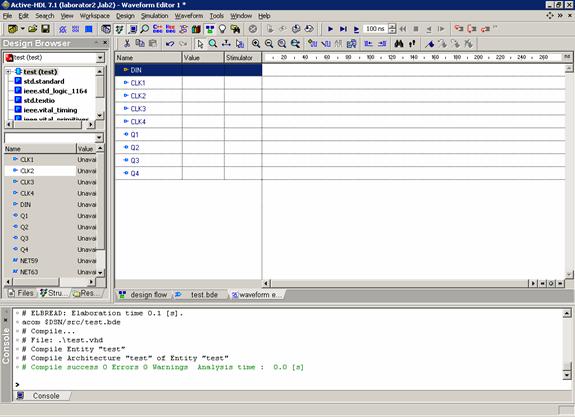

Simularea circuitelor folosind mediul ActiveHDL

Pasii efectuati pentru simularea circuitelor folosind mediul ActiveHDL sunt aceeasi indiferent daca este vorba despre simularea circuitelor descrise cu editorul Schematic sau a circuitelor descrise in limbajul VHDL.

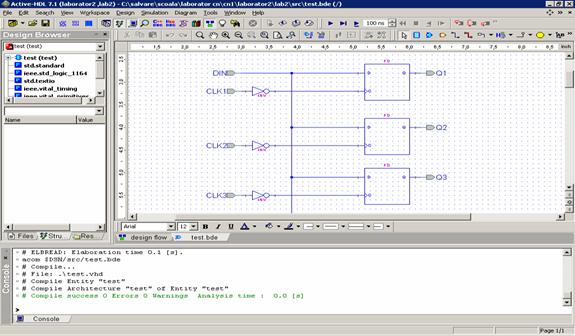

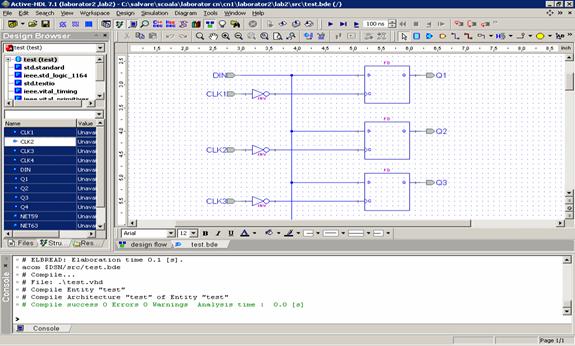

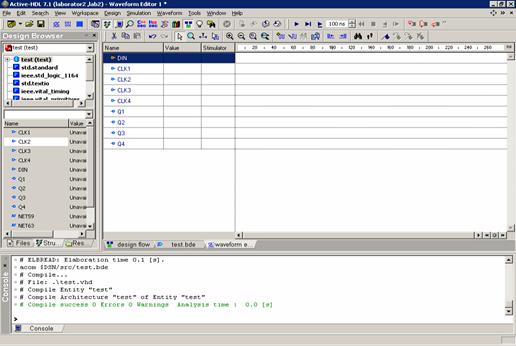

Dupa ce circuitul a fost descris si compilat se realizeaza simularea acestuia:

![]()

![]()

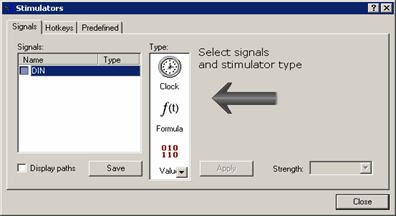

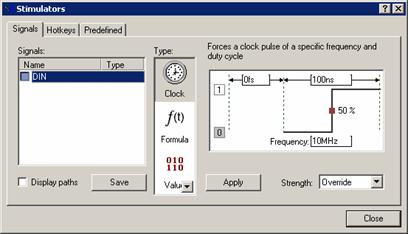

In lista Type se selecteaza tipul Stimulului.

De exemplu daca se selecteaza stimul de tip Clock se va genera un semnal periodic cu frecventa configurabila din fereastra:

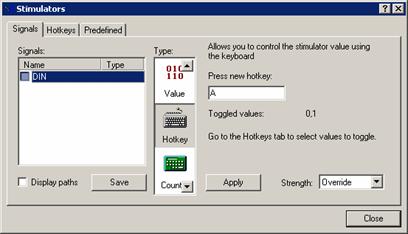

Daca se selecteaza HotKey se va permite generarea de semnale aperiodice, starea intrarii se schimba la apasarea tastei. Tasta este selectabila:

Se apasa Apply pentru fiecare intrare setata cu un stimul iar in final Close.

![]()

Simulatorul va rula un interval de timp selectat din lista de langa buton.

Pentru simulare se folosesc urmatoarele butoane:

|

|

Rulare un pas pentru un interval de timp setat |

|

|

Oprire simulator |

|

|

Repornire simulare |

Pentru stergerea formelor de unda se apasa click dreapta pe fereastra cu formele de unda si se selecteaza "Clear All Waveforms after Cursor".

Sinteza si implementarea circuitelor folosind mediul ActiveHDL. Descarcarea fisierului de configuratii in FPGA

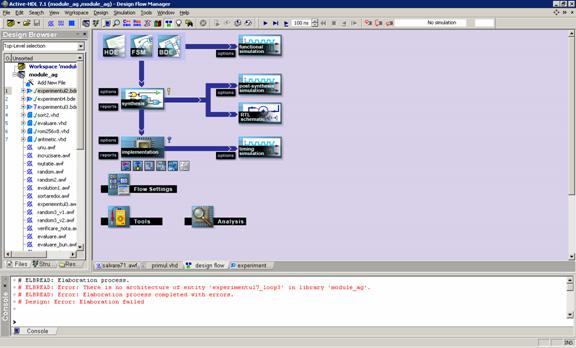

Dupa crearea proiectului, descrierea circuitelor si simularea lor se va afisa fereastra principala a proiectului (se selecteaza tag-ul design flow sau din meniu View - Flow).

![]()

Se apasa in dreptul lui Design File butonul Browse si se cauta fisierul .vhd al circuitului care se doreste implementat. Daca circuitul a fost realizat cu editorul schematic atunci fisierul .vhd cu acelasi nume cu al fisierului schematic se afla in subdirectorul Compile in directorul unde se afla proiectul. Daca circuitul a fost descris folosind limbajul VHDL atunci fisierul .vhd se va afla in subdirectorul SRC din directorul unde se gaseste proiectul. Automat, in campul Constraints File va aparea calea catre fisierul de constrangeri .ucf. Aceasta cale trebuie notata pentru urmatorul pas! Se apasa OK.

![]()

In fereastra Implementation Options se fac urmatoarele setari: Device - 3s400fg456,

Speed Grade -- -4, se debifeaza optiunea Use default UCF file iar apoi, prin actionarea

butonului Browse din dreptul optiunii se cauta calea unde a fost generat fiserul de

constrangeri .ucf (de obicei aceeasi cu cea a fisierului rezultat al sintezei). Se bifeaza Generate Programming File.

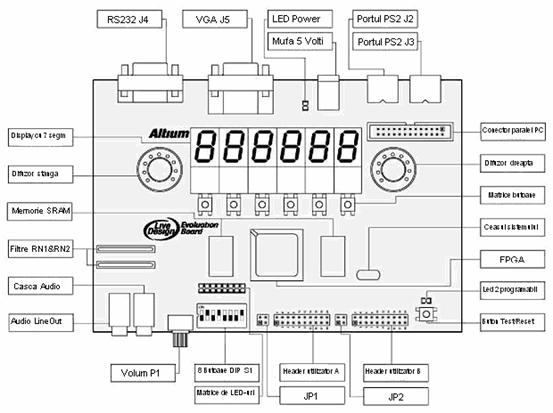

Prezentarea machetei de laborator

Implementarea structurilor descrise se face pe macheta de laborator cu FPGA Xilinx Spartan 3, XCS300FG456 -4.

Circuitul FPGA se afla conectat, pe anumiti pini, la mai multe circuite periferice: afisoare LED 7 segmente, LED-uri, butoane, comutatoare, port serial, port VGA etc.

Circuitele periferice utilizate pe parcursul laboratoarelor sunt urmatoarele:

8 circuite butoane - comutatoare reprezentate cu SW_DIP7..SW_DIP0, localizate jos, centru, asa cum este reprezentata schema in figura de mai sus;

6 circuite butoane cu revenire, aflate in centrul machetei, sub afisoarele 7 segmente, reprezentate cu SW_USER5..SW_USER0;

1 circuit buton test-reset aflat in partea dreapta, jos la macheta, SW_TEST;

8 LED-uri aflate deasupra butoanelor - comutatoare LED7..LED0;

6 afisoare 7 segmente fiecare aflate in partea centrala a machetei: DIG0..5SEG0..7.

Ordinea in care au fost declarate circuitele este de la stanga la dreapta (exemplu LED0 este led-ul din partea stanga).

Pentru a putea lucra cu aceste periferice, porturile logice din circuitul prelucrat trebuie asociate cu pinii fizici ai FPGA-ului conectati la circuitele periferice.

De exemplu, daca avem urmatorul circuit logic:

![]()

Porturile sw0 si sw1 sunt porturi logice si ele trebuie conectate la comutatoarele sw0 si sw1 de pe macheta. Pentru aceasta trebuie cunoscut care pini fizici ai FPGA-ului sunt conectati la cele doua comutatoare. In tabelul de mai jos sunt dati toti pinii fizici corespunzatori circuitelor periferice de pe macheta utilizati pe parcursul laboratoarelor:

Denumirile pinilor corespund cu denumirile acestora pe macheta.

|

Pin schema macheta |

Pin fizic FPGA |

|

sw_dip0 |

y6 |

|

sw_dip1 |

v6 |

|

sw_dip2 |

u7 |

|

sw_dip3 |

aa4 |

|

sw_dip4 |

ab4 |

|

sw_dip5 |

aa5 |

|

sw_dip6 |

ab5 |

|

sw_dip7 |

aa6 |

|

sw_user0 |

d1 |

|

sw_user1 |

c1 |

|

sw_user2 |

b6 |

|

sw_user3 |

a15 |

|

sw_user4 |

b20 |

|

sw_user5 |

c21 |

|

led0 |

w2 |

|

led1 |

y1 |

|

led2 |

y2 |

|

led3 |

y3 |

|

led4 |

w4 |

|

led5 |

w5 |

|

led6 |

y5 |

|

led7 |

w6 |

|

dig0_seg0 |

c6 |

|

dig0_seg1 |

b8 |

|

dig0_seg2 |

e7 |

|

dig0_seg3 |

c5 |

|

dig0_seg4 |

e6 |

|

dig0_seg5 |

b5 |

|

dig0_seg6 |

a4 |

|

dig1_seg0 |

b10 |

|

dig1_seg1 |

a12 |

|

dig1_seg2 |

c10 |

|

dig1_seg3 |

a9 |

|

dig1_seg4 |

b9 |

|

dig1_seg5 |

a10 |

|

dig1_seg6 |

e9 |

|

dig2_seg0 |

e15 |

|

dig2_seg1 |

e16 |

|

dig2_seg2 |

a14 |

|

dig2_seg3 |

d14 |

|

dig2_seg4 |

d13 |

|

dig2_seg5 |

b13 |

|

dig2_seg6 |

e13 |

|

dig3_seg0 |

b17 |

|

dig3_seg1 |

b18 |

|

dig3_seg2 |

a18 |

|

dig3_seg3 |

b15 |

|

dig3_seg4 |

d17 |

|

dig3_seg5 |

c17 |

|

dig3_seg6 |

e17 |

|

dig4_seg0 |

d19 |

|

dig4_seg1 |

f18 |

|

dig4_seg2 |

c20 |

|

dig4_seg3 |

c19 |

|

dig4_seg4 |

c18 |

|

dig4_seg5 |

b19 |

|

dig4_seg6 |

d18 |

|

dig5_seg0 |

f19 |

|

dig5_seg1 |

g17 |

|

dig5_seg2 |

e19 |

|

dig5_seg3 |

d21 |

|

dig5_seg4 |

d20 |

|

dig5_seg5 |

e18 |

|

dig5_seg6 |

c22 |

Cerinte laborator:

1. Sa se identifice circuitele periferice de pe macheta

2. Parcurgand etapele descrise mai sus sa se proiecteze, simuleze si implementeze un circuit de adunare a trei numere pe un bit (sumator complet pe un bit) avand schema de mai jos.

2.a. Se va crea proiectul. Se va descrie circuitul prezentat in figura de mai jos.

2.b. Se va realiza simularea astfel: pe portul se va conecta ca stimul un semnal de ceas cu frecventa 8 MHz. Pe portul B se va conecta ca stimul un semnal de ceas cu frecventa 4 MHz. Pe portul C se va conecta ca stimul tasta C. Se va simula comportamentul circuitului pentru C=0 si C=1 trecand prin toate starile intrarile A si B.

2.c. Se va realiza sinteza si implementarea circuitului pe macheta FPGA conectand porturile logice ca in tabelul de mai jos:

|

Port logic |

Circuit macheta |

|

a |

sw_dip0 |

|

b |

sw_dip1 |

|

ci |

sw_dip2 |

|

s |

led0 |

|

co |

led1 |

2.d. Se va descarca programul si se va opera cu el pe macheta.

Criterii de evaluare:

|

2P |

|

|

2a |

3P |

|

2b |

4P |

|

2c |

3P |

|

2d |

2P |

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1935

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved