| CATEGORII DOCUMENTE |

Exemplu de memorie EEPROM - ATMEL AT28C256

Circuitul AT28C256 este o memorie in tehnologie CMOS, de 256 Kbit organizata pe 32Kocteti. Are timpul de acces la citire de 150nsec si un curent de 50mA (in standby de 200μA).

Memoria suporta 104 pana la 105 cicli de scriere cu o durata de retinere de 10 ani.

Se alimentaza cu o tensiune de 5 V..

Circuitul poate fi accesat ca o memorie RAM static, fara nici o componenta aditionala.

Contine registri de pagina de 64 octeti, lucru ce permite scrierea a 1 pana la 64 octeti simultan (deoarece scrierea este mai lenta deat l amemoria RAM statica (3 pana la 10 ms pe pagina)adresa si cei 1 la 64 octeti de data sunt pastrati in latch, fapt ce permite eliberarea magistralelor). Dupa incarcrea adresei de pagina si a datelor, in timpul unui ciclu de scriere, adresa este incrementata automat si scrierea este realizata fara asistenta procesorului. Sfarsitul scrierii este semnalizat printr-un fanion pe pinul de data I/O7.

Dupa incheierea ciclului de scriere, un alt ciclu de citire sau scriere poate fi initializat.

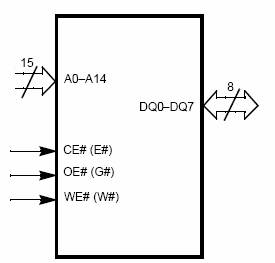

Fig. 2.10 Pinout-ul si functiile pinilor circuitului de memorie EEPROM

Operarea cu circuitul de memorie EEPROM.

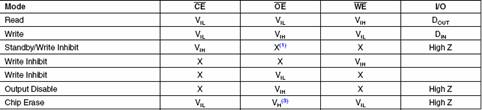

Fig.2.11. Functiile memoriei EEPROM si modurile de operare

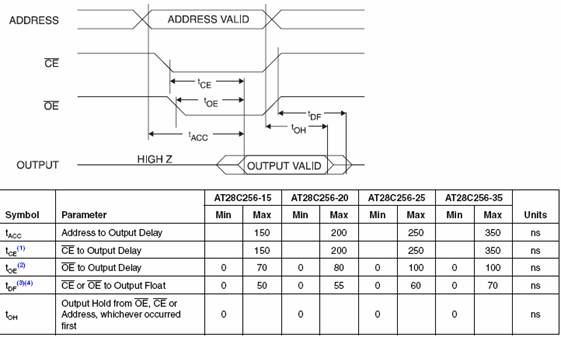

Citire. Circuitul este accesat ca si o memorie RAM static. Data din memorie de la adresa de pe magistrala este citita daca CE si OE sunt la nivel LOW si WE este HIGH. Liniile de date sunt in stare de High Impedance (High Z, tri-state, impedanta ridicata) daca una dintre CE sau OE sunt la nivel HIGH. Vezi fig.2.12

Fig.2.12. Ciclul de citire al memoriei EEPROM

Scriere pe octet.

Circuitul poate fi scris fara a fi sters in prealabil. Exista si optiunea de stergere a intregului chip.

Un impuls negativ pe liniile WE sau CE (cu CE respectiv WE pe nivel LOW), si OE pe nivel HIGH, initiaza un ciclu de scriere. Adresa este memorata pe frontul coborator al CE sau WE, oricare dintre ele coboara ultimul, iar data este memorata de primul front ridicator al WE sau CE. Odata ciclul initiat el se va derula automat, sfarsitul sau va fi semnalizat de bitul de data I/O7 citit printr-o actiune de citire de tip Polling. Vezi fig.2.13.

Fig.2.13 Ciclul de scriere al memoriei EEPROM

Scrierea pe pagina

Circuitul AT28C256 permite scrierea unei pagini de 1 pana la 64 de octeti. Operatia de scriere pe pagina este initiata ca si scrierea pe octet, primul octet putand fi urmat de alti 63 de octeti, fiecare dintre ei trebuind sa fie scrisi la cel mult 150 ms distanta. Liniile de adresa A6-A14 (care denota o pagina) trebuie sa fie mentinute constante p eparcursul scrierii celor 1 la 64 octeti.. Liniile A0 la A5 specifica adresa octetului in pagina. Vezi fig. 2.14

Data Polling. Aceasta operatie se executa pentru a determina daca ciclul de scriere s-a incheiat. O incercare de citire a datei pe parcursul ciclului de scriere (cat timp scrierea nu s-a incheiat) va rezulta prin citirea ultimului octet complementat pe pinul I/O7. Cand scrierea s-a incheiat, bitul este trecut la valoarea sa adevarata. si operatiile de citire/scriere pot fi initiate din nou.

Ciclul de stergere.

2.2.d) Exemplu de memorie FLASH - AMD Am28F256

Memoria FLASH Am28F256 este o memorie nevolatila de 256Kbit organizata pe 32Kocteti. Este o memorie rapida, cu ciclul de citire de 70nsec. Pentru scriere insa are nevoie sa fie stearsa in prealabil (operatie ce dureaza in medie 1 sec), stergerea facandu-se pe intregul chip. Pentru stergere si scriere este necesara aplicarea unei tensiuni suplimentare VPP de 12V, care nu este necesara la operatia de citire. Operatia de scriere dureaza 10 msec.

Curentul consumat este de 30 mA maximum in cicli activi (scriere, stergere, scriere si de 100 μA maximum in standby.

Suporta minimum 104 cicli de scriere/stergere

Pinii memoriei FLASH sunt prezentati in fig.2.15

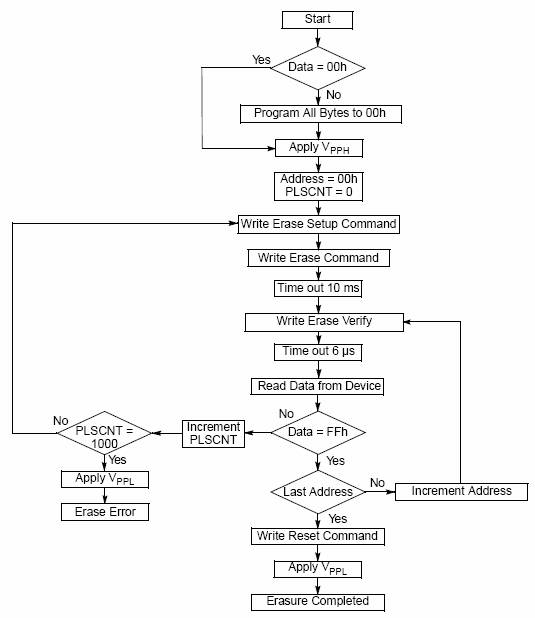

Operatia de citire se executa identic cu memoriioe EPROM. Pentru stergere si scriere insa, ciclii sunt specifici. In fig.2.16 si 2.17 sunt prezentate ordinograma si diagrama temporala a operatiei de stergere. Circuitul de memorie este programat sa execute aceasta operatie astfel:

Se dau doua comenzi de stergere, prima pentru setare, a doua de startare a executiei. Circuitul , in prima faza scrie toata memoria cu 00h dupa care sterge tot continutul (octetii vor avea valoarea FFh). In incheiere, este necesara verificarea corectitudinii datelor. Daca aceasta nu s-a incheiat corect (exista biti care nu sunt setati pe 1 logic)se relanseaza operatia de stergere. Se estimeaza ca sunt necesare, in mod normal, 100 de repetari a stergerii pentru incheierea acesteia cu succes. Daca dupa 1000 de cicli memoria nu este stearsa, se considera eroare de stergere si se renunta.

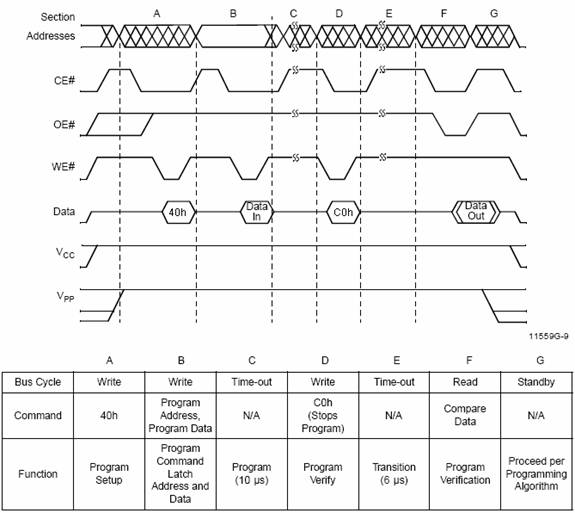

Operatia de scriere octet cu octet, se desfasoara tot dupa un program, prezentat in fig. 2.18, cu diagrama in fig.2.19.

Fig.2.18. Ordinograma operatiei de scriere

Fig.2.19. Diagrama temporala a operatiei de scriere.

2.3. Organizarea memoriei la microcontrolerul 80C552 din familia 8051

Unitatea centrala a microcontrolerul 80C552 manipuleaza operanzi in trei zone de memorie (vezi fig.2.20):

memorie de program externa[1] de dimensiune de pana la 64Kocteti

memorie de date externa de dimensiune de pana la 64Kocteti

memorie de date interna de 256 octeti suprapusa cu 128 octeti de memorie ce contine Registri cu Functii Speciale (SFR)[2]. In total 384 octeti.

Memoria de date interna este divizata in 3 sectiuni: partea de jos de 128 octeti de RAM Data intern (de la 0 la 127), partea de sus de 128 octeti de RAM Data intern (de la 128 la 255) si zona de 128 octeti de SFR (de la 128 la 255). Ultimele doua zone (SFR si zona 128 la 255) impart aceeasi arie de adresare, sunt deci suprapuse, selectia se face prin modurile de adresare.

SFR sunt locatii de memorie cu functie de registru prin care CPU comunica cu periferia microcontrolerului - atat date cat si comenzi. Inclusiv Acumulatorul, PSW, Stack Pointer-ul si Data Pointer-ul sunt inclusi in SFR. Nu fac parte din SFR, avand o alta locatie, Program Counter-ul si cele 4 Blocuri de registri de uz general.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1945

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved