| CATEGORII DOCUMENTE |

Sisteme de memorie

1. Ierarhia memoriilor

Odata cu cresterea vitezei UCP, limitarea viteyei sistemelor de calcul poate fi datorata timpului de acces al memoriei. Pentru a se evita pierderea ciclurilor UCP datorita timpului de acces al memoriei, au fost dezvoltate memorii mai rapide. Costul acestor memorii nu permite insa utilizarea lor exclusiva intr-un sistem de calcul. Aceasta conduce la necesitatea existentei unei erarhii de memorii, care permite utilizarea unei combinatii de memorii mai rapide (cu cost ridicat) si mai lente (cu un cost relativ redus).

Actualmente, tendinta generala a calculatoarelor mari, cat si a calculatoarelor personale, este extinderea utilizarii ierarhiilor de memorii. Motivul principal a acestei tendinte se datoreaza modului in care opereaza programele. Prin analize statistice ale unor programe tipice s-a constatat ca in orice interval de timp dat referintele la memorie tind sa se restranga in zone locale ale memoriei. Aceasta proprietate este cunoscuta sub numele de localitate a referintelor. Exista trei concepte asociate cu localitatea referintelor: localitatea spatiala, temporala si secventiala. Aceste concepte sunt definite in continoare.

Localitatea spatiala. De multe ori, un program utilizeaza date si instructiuni ale caror adrese sunt apropiate unele de altele in spatiul de adrese. De exemplu, referintele la elementele unui tablou apar intodeauna in cadrul unei anumite zone limitate din spatiul de adrese . Similar, daca UCP face referire la o instructiune I de un cuvant, memorata la o adresa data A, instructiunea cea mai probabila de a fi referentiata in continuare de catre UCP este cea mai imediat urmatoare dupa I, a carei adrese este A+1.

Localitatea temporala. Datele sunt instructiunile referite recent au o posibilitate ridicata de a fi referite in viitorul apropiat. De exemplu, un grup de instructiuni dintr-o bucla interativa sau o subrutina pot fi executate in mod repetat, rezultand o frecventa ridicata a referintelor la adresele acestora.

Localitatea secventiala. Majoritatea instructiunilor dintr-un program sunt executate intr-o ordine secventiala. Instructiunile care pot determina executia intr-o ordine diferita de cea secventiala sunt salturile sau apelurile de proceduri. Acestea reprezinta insa doar intre 20% si 30% din totalul instructiunilor. De aceea, intre 70% si 80% din instructiuni sunt executate in aceeasi ordine in care ele sunt pastrate in memorie.

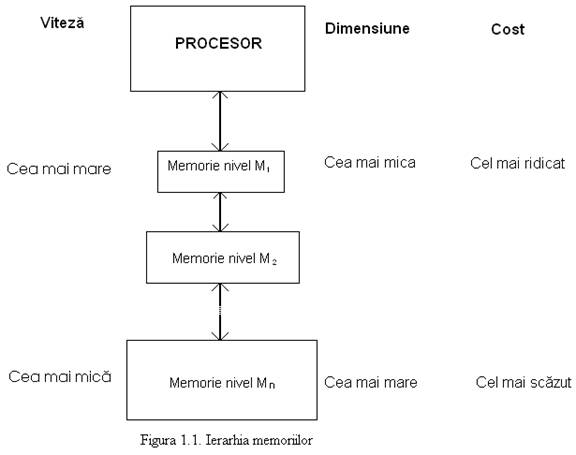

In mod uzual, se poate considera ca diferitele unitati de memorie dintr-un sistem tipic formeaza o ierarhie de memorie (M1,M2,.,Mn), dupa cum se arata in figura 1.1. Nivelul cel mai inalt, M1, este repreyentata de unitatea de memorie cea mai rapida, cu dimensiunea cea mai redusa, si cu costul cel mai ridicat, fiind amplasat cel mai aproape de procesor. Urmatorul nivel, M2, care este mai lent, are dimensiuni mai mari si un cost mai redus decat nivelul M1, fiind amplasat mai departe de procesor. Acelasi lucru este valabil pentru nivelele M3 pana la Mn. In general, pe masura ce nivelul creste, viteza si deci costul pe bit creste in mod proportional, ceea ce tinde sa micsoreze capacitatea memoriei de la acel nivel.

Din cauza proprietatii de localitate a referintelor, in general transferurile de date au loc in blocuri cu dimensiuni fixe (numite uneori pagini sau linii). Blocurile sunt transferate numai intre doua nivele adiacente la un moment dat. Nivelul superior - cel care este mai apropiat de procesor - are o dimensiune mai redusa si este mai rapid (deoarece utilizeaza o tehnologie mai costisitoare) decat nivelul mai inferior. Daca datele solicitate de procesor se afla intr-un anumit bloc al nivelului superior, aceasta reprezinta un succes (hit). Daca datele nu se afla in nivelul superior, cererea reprezinta un esec (miss). Rata de succes Rs (hit rate), sau raportul de succes, reprezinta raportul intre numarul acesului la memorie pentru care se obtine un succes si numarul total de accesuri la memorie. Aceasta rata este utilizata adesea ca o masura a performantei pentru ierarhia de memorie. Rata de esec Re=1 - Rs este raportul intre numarul accesurilor la memorie pentru care se obtine un esec si numarul total de accesuri la memorie.

In general, oro de cate ori exista un bloc in memoria de nivel i. Exista o copie a acestui bloc in fiecare din nivelele inferioare i+1,,n. De asemenea, ori de cate ori un bloc nu este gasit in memoriea M1, se transmite o cerere pentru acest bloc la nivelele succesive inferioare pana cand blocul este localizat , de exemplu in memoria Mi. Deoare ce fiecare nivel are o capacitate limitata, atunci cand nu mai exista spatiu in memoria Mi si trebuie incarcat un bloc din memoria Mi+1, se inlocuieste un bloc din Mi utilizand o strategie de inlocuire predefinita. Aceste strategii sunt gestionate prin hardwere si prin sistemul de operare.

Timpul de acces este timpul pentru accesul la nivelul superior a ierarhiei de memorie, care cuprinde timpul pentru a determina daca accesul este un succes sau un esec. Penalizarea pentru esec este timpul necesar inlocuirii unui bloc din nivelul superior cu blocul corespunzator din nivelul inferior, plus timpul necesar pentru furnizarea acestui bloc procesorului.

Avantajul principal al unui sistem de memorie ierarhic este faptul ca in majoritatea timpului informatia este preluata din nivelul cel mai rapid M1. Astfel, timpul de acces mediu al memoriei este apropiat de timpul de acces al nivelului superior, in timp ce costul mediu unitar al sistemului de memorie este apropiat de costul nivelului inferior.

Componentele sistemului de memorie pot fi plasate in patru grupe, preyentate in continoare.

Registre UPC. Registrele de viteza ridicata ale UPC sunt utilizate ca memorie de lucru pentru pastrarea temporara a instructiunilor si datelor. Ele formeaza de obicei un set de registre cu scopul general pentru pastrarea datelor. Fiecare registru poate fi accesat pentru citire sau scriere intr-un singur ciclu de acces.

Memoria principala (primara). Aceasta memorie externa rapida pastreaza programe si date care sunt in uz curent. Locatiile memoriei principale sunt adresate direct prin instructiunile de incarcare si memorare ale UCP. Cu toate ca se utilizeaza o tehnologie similara cu cea a setului de registre al UCP, accesul este mai lent din cazul faptului ca memoria principala este separata fizic de UCP. Capacitatea memoriei principale este cuprinsa in general intre 64 MB si 1 GB, iar timpii de acces tipici sunt de cateva cicluri de acces.

Memoria secundara. Acest tip de memorie este o capacitate mult mai mare, dar in acelasi timp este mult mai lenta decat memoria principala. Memoria secundara pastreaza programe si date care nu sunt solicitate in mod constant de UCP. Este utilizata de asemenea atunci cand capacitatea memoriei principale este depasita. Infomatia din memoria secundara este accesata indirect prin programe de intrare/iesire care transfera informatii intre memoria principala si cea secundara. Tehnologiile reprezentative pentru memoria secundara sunt discurile magnetice fixe si discurile optice, ambele avand mecanisme de acces electromecanice relativ lente. Capacitatile de memorare de mai multi GB sunt obisnuite, iar timpii de acces se masoara in milisecunda.

Memoria cache. Majoritatea calculatoarelor si procesoarelor au un alt nivel de memorie (uneori mai multe asemenea nivele) numita memorie cache, care este pozitionata logic intre registre UCP si memoria principala. Capacitatea de memorie a memoriei cache este mai mica decat cea a memoriei principale, dar cu un timp de acces de unul la 3 cicluri de ceas, memoria cache este mai rapida decat memoria principala, deoarece o parte a acesteia sau intreaga memorie cache se poate afla in aceeasi capsula cu UCP. Memoriile cache sunt componente esentiale ale calculatoarelor cu performante ridicate. Spre deosebire de celelalte trei tipuri de memorie, memoriile cache sunt de obicei transparente programatorului. Memoria principala si memoriile cache implementeaza impreuna memoria externa adresata direct de instructiunile UCP.

Pe masura avansului tehnologic, costul memoriilor semiconductoare a scazut considerabil, cea ce a permis utilizarea in sisteme de calcul a unor a unor memorii semiconductoare de dimensiuni mari ca memorii principale. Ca urmare, majoritatea datelor necesare pot fi incalcate in avans in memoriile semiconductoare, prin care se pot satisface o mare parte din referintele la memorie. De aceea, impactul vitezei memoriilor de masa asupra sistemului de calcul este in scadere.

2. Tipuri de memorii

O caracteristica fundamentala a unei memorii este ordinea sau secventa in care informatiile pot fi accesate. Pot fi distinse patru tipuri de metode de acces:

Metoda de scriere a informatiilor intr-o memorie poate fi reversibila sau permanenta . Memoriile la care citirea si scrierea pot fi efectuate in timpul functionarii sunt numite memorii cu citire-scriere. Toate memoriile utilizate pentru memorare temporara sunt de acest tip. Memoriile semiconductoare cu citire-scriere sunt numite de obicei memorii cu acces aleator (RAM), aceea ce reprezinta o folosire improprie a termenului, deoarece exista si alte tipuri de memorii care sunt cu acces aleator.

Memoriile al caror continut nu

poate fi modificat sunt numite memorii numai de citire (ROM - Read-Only

Memory). O memorie ROM este astfel o memorie care nu se poate sterge.

Aceasta este citita utilizand metode de acces aleator ca cele pentru

memoriile RAM. Memoriile ROM sunt utilizate pe scara larga pentru

memorarea programelor de control cum sunt microprogramele. Alte aplicatii

cuprind programe de sistem sau subrutine de biblioteca pentru functii

utilizare frecvent. Discurile compact, cum sunt discurile CD-ROM,

reprezinta o clasa de memorie secundara ROM care utilizeaza

un mecanism de citire-scriere optic.

Memoriile al caror continut nu

poate fi modificat sunt numite memorii numai de citire (ROM - Read-Only

Memory). O memorie ROM este astfel o memorie care nu se poate sterge.

Aceasta este citita utilizand metode de acces aleator ca cele pentru

memoriile RAM. Memoriile ROM sunt utilizate pe scara larga pentru

memorarea programelor de control cum sunt microprogramele. Alte aplicatii

cuprind programe de sistem sau subrutine de biblioteca pentru functii

utilizare frecvent. Discurile compact, cum sunt discurile CD-ROM,

reprezinta o clasa de memorie secundara ROM care utilizeaza

un mecanism de citire-scriere optic.

O memorie semiconductoare ROM este fabricata ca si orice alta capsula de citit integrat, datele fiind inscrise in circuit ca parte a procesului de fabricatie. Aceasta are dezavantajul ca procesul de includere a datelor are un cost fix relativ ridicat, ceea ce este acceptabil numai pentru cantitati mari. Atunci cand este necesar doar un numar redus de memorii ROM cu un aumit continut, o alternativa mai putin costisitoare este memoria PROM (Programmable Read-Only Memory). In cazul memoriei PROM, procesul de scriere este executat prin semnale electrice de catre furnizor sau utilizator intr-un moment ulterior fabricatiei circuitului. Procesu lde scrier, numit "programare", este executat off-line utilizand un echipament special. Memoria PROM asigura flexibilitate la un cost modest, dar are dezavantajul ca nu poate fi sters.

O alta variatie a memoriei ROM este memoria EPROM (Erasable

Programmable Read-Only Memory). Aceasta este citita si inscrisa

electric, ca si memoria PROM, insa inaintea unei operatii de

scriere toate celulele de memorare trebuie sterse pentru a avea

acceasi stare initiala prin expunerea capsulei la o

radiatie ultravioleta. Acest proces de stergere poate fi

executat in mod repetat.

O forma mai atractiva de memorie ROM este memoria EEPROM (Electrically Erasablr Programmable Read-Only Memory). Aceasta memorie poate fi inscrisa in orice moment fara a-i sterge continutul. Operatiunea de scriere trebuie efectuata pe blocuri si necesita un timp considerabil mai lung decat operatiunea de citire. Memoria EEPROM are avantajul ca poate fi actualizata on-line, utilizand semnele obisnuite de control, adrese si date. Acest tip de memorie este potrivit pentru pastrarea programelor de control si ca un inlocuitor al memoriei secundare in anumite aplicatii.

La anumite tehnologii de memorie, informatiile memorate se pierd dupa o perioada de timp daca aceasta nu este refacuta. Trei din caracteristicile memoriileor care pot distruge informatiile in acest fel sunt citirea distructiva, memorarea dinamica si volatilitatea. La anumite memorii metoda de citire distruge informatiile memorate; acest fenomen este numit citire distructiva (DRO - Destructive Reandout). Memoriile la care citirea nu afecteaza informatiile memorate sunt caracterizate prin citire nedistructiva (NDRO - Non-Destructive Reandout). La memoriile DRO fiecare operatiune de citire trebuie urmata de o operatiune de scriere care reface starea originala a memoriei. Aceasta refacere este efectuata automat utilizand un registru buffer. Operatiunea de citire transfera cuvantul din locatia adresata in registu buffer. Continutul bufferului este rescris apoi in locatia originala.

Anumite memorii au proprietatea ca informatia memorata are tendinta sa se modifice dupa un anumit timp, datorita unui proces fizic. De exemplu, la anumite memorii semiconductoare o sarcina electrica dintr-un condensator reprezinta valoarea binara 1, iar absenta sarcinii reprezinta valoarea binara 0. In timp, condensatorul tinde sa se descarce, determinand pierderea informatiei daca sarcina nu este refacuta printr-un proces numit reimprospatare. Memoriile care necesita o reimprospatare periodica sunt numite memorii dinamice, spre deosebire de memoriile statice, care nu necesita reimprospatare. Majoritatea memoriilor care utilizeaza tehnici de memorare magnetica sau optica sunt statice. O memorie dinamica este reimprospatata in acelasi mod in care sunt refacute informatiile intr-o memorie de citire distructiva. Continutul fiecarei locatii este citit periodic in registree buffer, iar apoi este rescris sub forma amplificata in locatia originala.

Continutul unei memorii poate fi distrus de asemenea prin eliminarea sau defectarea sursei sale de alimentare. O memorie este volatila daca lipsa tensiunii de alimentare distruge informatiile memorate. Memoriile RAM semiconductoare dinamice si statice sunt volatile, in timp ce memoriile ROM si variantele lor sunt nevolatile. Majoritatea memoriilor secundare magnetice si optice sunt nevolatile.

3. Indicatori de performanta ai memoriilor

Din punctul de vedere al utilizatorului, cele mai importante caracteristici ale unei memorii sunt capacitatea si performanta. Performanta unei memorii este determinata in principal la cata la care informatiile pot fi citite din memorie sau scrise in memorie. Cei mai importanti indicatori de performanta utilizati sunt timpul de acces, durata ciclului, rata de transfer si fiabilitatea. Acestea sunt descrise in continuare.

Timpul de acces al unei memorii cu acese aleatoriu, notat cu tA, este timpul necesar pentru a executa o operatie de citire sau scriere pentru o cantitate fixa de informatii, de exemplu, un cuvant. Acest timp este calculat din momentul in care memoria primeste o cerere de citire sau scriere pana in momentul in care datele sunt disponibile pentru utilizarea sau sunt memorate. Timpul de acces pentru citire nu este intodeauna egal cu timpul de acces pentru scriere. Pentru o memorie cu acces non-aleator, timpul de acces este timpul necesar pentru a pozitiona mecanismul de citire-scriere la locatia dorita.

Desi densitatea de memorare a crescut rapid pentru principalele tehnologii de memorare, timpii de acces au scazut intr-o rata mult mai lenta. Viteza memoriilor a crescut lent, dar viteza de calcul a procesoarelor a crescut mult mai rapid. Asa cum vom prezenta in acest capitol, se utilizeaza diferite tehnici de proiectare pentru cresterea ratei efective la care UCP poate accesa informatiile memorate in sistemul de memorare al calculatorului.

Durata ciclului, notata cu tM, se refera in primul rand la memoriile cu acces aleator si consta in timpul de acces si timpul suplimentar necesar inainte de a putea incepe un al doilea acces. Anumite memorii cu citire distructiva nu pot initia un nou acces inainte de a fi executata o operatie de refacere sau reimprospatare. De aceea, timpul minim care trebuie sa treaca intre inceperea a doua operatii de acces consecutive poate fi mai mare decat timpul de acces tA.

Rata de transfer, notata cu rM, este cantitatea maxima de informatii care pot fi transferate in sau din memorie in unitatea de timp. Aceasta rata este masurata in biti pe secunda sau cuvinte pe secunda. Daca w este numarul de biti care pot fi transferati simultan cu memoria, rata de transfer este rM = w/tM biti/s. Daca tM = tA, atunci rM = w/tA . Anumite tipuri de memorii, in particular memoriile seriale, necesita un timp de acces tA ridicat pentru a initia o noua operatie de acces; insa, odata ce operatia este initiata, transferul datelor poate avea loc la o rata rM mult mai mare decat w/tA . In asemenea cazuri, fabricantul pune la dispozitie specificatii independente pentru tA, tM, rM si parametrii de performanta asociati.

Fiabilitatea este masurata prin timpul mediu intre defecte (MTBF - Mean Time Between Failures). In general, memoriile fara parti in miscare au o fiabilitate mult mai ridicata decat memoriile care implica o deplasare mecanica, precum discurile magnetice. Chiar si la memoriile fara parti in miscare, apar probleme de fiabilitate, in particular atunci cand se utilizeaza densitati de memorare sau rate de transfer foarte ridicate. Codurile detectoare de erori si codurile corectoare de erori pot creste fiabilitatea orcarui tip de memorie.

4. Memoria principala semiconductoare.

Memoria principala semiconductoare este de obicei o memorie cu acces aleator (RAM). Acest tip de memorie se distinge prin faptul ca fiecare locatie de memorare poate fi accesata independent, cu un timp de acces fix care este independent de pozitia locatiei accesteia.

4.1.Memorie RAM dinamic

Ca si la circuitele de RAM static, pe un chip de RAM dinamic memoria este organizata intr‑o matrice formata din linii si coloane de celule de memorie. Circuitele RAM dinamic sint de capacitate mai mare decit cele de RAM static, dar ele necesita citirea si inscrierea repetata a celulelor e memorie, proces care este numitimprospatarea memoriei (refresh). Intervalul de timp necesar intre doua improspatarivariaza de la 1 la 100 ms. Pentru o functionare la 70 C, intervalul tipic de improspatare este de

2 ms. Desi o linie de celule este improspatata in timpul unei citiri sau a unei scrieri, referintele aleatoare la memorie nu pot garanta ca fiecare cuvint al memoriei este improspatat in acest interval de 2 ms. De aceea, este necesar un mod sistematic de improspatare a memoriei, prin cicli de improspatare.

Intr‑un ciclu de improspatare a memoriei se trimite la circuitele de memorie a adresa de linie si se efectueaza o operatie de citire pentru a improspata linia de celule selectata. Totusi, ciclurile de citire difera de un ciclu normal de citire a memoriei in mai multe privinte :

‑ Intrarea pe adresele circuitelor de memorie nu vine de pe magistrala de adrese, ci adresa de linie este furnizata de un numarator binar numit numarator al aresei de improspatare (refresh address counter). Acest numarator este incrementat cu 1 pentru fiecare ciclu de improspatare a memoriei, astfel incit el trece secvential prin toate adresele de linie. Adresa coloanei nu este implicata, pentru ca toate elementele de pe o linie sint improspatate simultan.

‑ In timpul unui ciclu de improspatare a memoriei, sint activate toate circuitele de memorie, astfel incit improspatarea sa se efectueze simultan asupra tuturor. Astfel se reduce numarul de cicli de improspatare. Intr‑un ciclu de citire obisnuit, este activat la un moment dat un singur circuit.

‑ In plus fata de intrarea 'Chip Enable' de activare a circuitului, un RAM dinamic are in muod normal un pin pentru activarea iesirii datelor. Aceste doua intrari de comanda sint combinate intern astfel incit iesirea datelor este fortata in starea de impedanta ridicata daca nu sint activate ambele intrari. In timpul unui ciclu de improspatare a memoriei, iesirea datelor este dezactivata, prin pinul corespunzator. Acest lucru este necesar pentru ca sint selectate toate circuitele din aceeasi coloana si iesirile lor de date sint conectate impreuna. Pe de alta parte, in timpul unui ciclu obisnuit de citire a memoriei, este selectata o singura linie; de aceea, semnalul de activare a iesirii datelor este activat pentru fiecare linie.

Pentru memoriile RAM cu densitate mai mare, adresa de linie si adresa de coloana impart in general aceeasi pini, reducind astfel numarul de pini ai dispozitivului. Pentru aceste memorii RAM au fost produse circuite integrate care includ logica de reimprospatare si ceea ce mai este necesar pentru a controla pinii de adrese de linie/coloana. Firma Intel furnizeaza pentru aceasta controller‑ul de RAM dinamic 8203, care este proiectat special pentru dispozitivele de memorie RAM dinamica 2117, 2118 si 2164. Vom studia mai departe folosirea lui 8203 cu 2164, care este un dispozitiv 64Kx1. Diagramele bloc pentru 2164 si 8203 se afla in figura 10‑2 (8203 poate avea doua moduri, in functie de pinul 16K/64K/; este prezentata numai asignarea pentru modul 64K).

2164 contine 4 tablouri cu 128x128 celule, dar numai 8 pini de adresa, pentru ca adresa de linie si adresa de coloana impart aceeasi pini si sint receptionate una dupa alta. Adresa de linie este strobata de un puls negativ pe pinul RAS/, iar cu RAS/ in 0 adresa de coloana este strobata de un puls negativ pe pinul CAS/. Cei mai semnificativi biti ai adresei de linie si de coloana specifica unul din cele 4 tablouri. In timpul unui ciclu de improspatare a memoriei, intrarea de adrese A7 nu este folosita si toate cele 4 tabele de celule sint simultan improspatate. Aceasta permite ca intreul dispozitiv sa fie improspatat in 128 de cicli.

Diagramele de tmip pentru ciclii de citire, scriere si improspatare se afla in figura 10‑3. Pentru un ciclu de citire, WE/ trebuie sa fie inactiv inainte de aplicarea pulsului CAS/ si ramine inactiv pina la terminarea pulsului CAS/. Dupa ce este strobata adresa de coloana, RAS/ este ridicat si cu RAS/ 1 si CAS/ 0, sa face disponibil bitul de date pe DOUT. Pentru un ciclu de scriere, semnalul DIN trebuie aplicat in timp ce CAS/ trece in 0, dar dupa ce pinul WE/ a trecut in 0. Scrierea se efectueaza prin pinul DIN, in timp ce RAS/, CAS/ si WE/ sint 0. Pinul DOUT este tinut in starea de impedanta ridicata in timpul acestui ciclu. Pentru un ciclu e improspatare, adresa de linie este strobata si pinul CAS/ este tinut inactiv. Pinul DOUT este pastrat in starea de impedanta ridicata.

8203 este proiectat pentru a elibera semnale corespunzatoare ca timing pentr 2164. Liniile OUT7/‑OUT0/ furnizeaza adresele de linie si de coloana, secventiate corespunzator, RAS1/‑RAS0/ furnizeaza stroburile pentru adresa de linie pentru pina la doua bancuri de 2164 si CAS/ si WE/ dau strobul adresei de coloana si semnalele de activare a scrierii pentru toate circuitele 2164 din modul. Se observa ca adresele eliberate de 8203 sint inversate, ceea ce nu este o problema, dar inseamna ca, atunci cind toate liniile de adresa au zerouri, se vor accesa ceklulele avind adresele de linie si coloana cu toti bitii 1.

B0, intrarea de selectare

a bancului, determina activarea pinului RAS/. AL7‑AL0

sint folosite pentru a genera adresa de linie si AH7‑AH0

pentru adresa de coloana. In mod normal, divizarea timpului pantru un ciclu de

improspatare este generata in interiorul lui 8203, dar pinul REFRQ permite ca

ciclii de improspatare sa fie initiati de o sursa externa. Selectia modului se

face prin pinul PCS/. El este numit Selectare protejata a circuitului

(protected chip select) pentru ca, odata ce devine activ, ciclul de memorie nu

mai poate fi abortat, chiar daca el se intoarce imediat in starea inactiva.

Iesire XACK/ este un strob care indica, in timpul unui ciclu de citire, daca datele sint disponibile sau, in timpul unui ciclu de scriere, daca datele au fost inscrise. El poate fi folosit pentru a stroba datele in tampoanele de iesire a datelor si pentru a trimite semnalul de READY catre procesor. Iesirea SACK/ semnalizeaza inceputul unui ciclu de acces la memorie si daca in timp ce se face o cerere catre memorie are loc un ciclu de improspatare, semnalul SACK/ este sters, pina cind incepe ciclul de citire sau de scriere. Daca se stie ca timpul de acces la memorie este suficient de mic pentru a garanta ca o citire va fi terminata la sfirsitul perioadei de ceas T3 sau ca o scriere va fi terminata la sfirsitul lui T4, atunci iesirea SACK/ poate fi folosita ca semnal de READY, in locul iesirii XACK/, salvind astfel stari de asteptare (wait) care ar putea apare prin folosirea lui XACK/.

Intre X0 si X1 trebuie conectat un oscilator sau, daca OP2 este conectat la +12V, trebuie aplicat pe CLK un semnal de ceas extern. Acest semnal poate veni de la o linie de ceas a magistralei sau de la un ceas inclus in modulul de memorie. Pentru alimentarea principala este necesara numai o sursa de +5V dar, daca se foloseste intrarea OP2 este necesara si o tensiune de +12V (REFRQ este de fapt un pin cu doua scopuri, putind fi folosit si pentru citiri in avans).

Un mod de a reduce numarul de circuite necesare pentru memoria RAM dinamica este de a pune in fiecare dispozitiv de memorie logica sa de improspatare. Un astfel de circuit este numit RAM integrat si, cu exceptia acceselor la memorie care sint efectuate uneori de ciclii de improspatare, dispozitivul apare utilizatorului ca un RAM static. Un exemplu este Intel 2186/7, care este un RAM integrat de 8Kx8. Asignarea pinilor pentru acest circuit este in esenta aceeasi ca pentru circuitele de RAM static,el avind pinii OE/, WE/ si CE/ care servesc acelorasi scopuri.

Trebuie subliniat ca circuitele RAM dinamic au unele avantaje fata de cele de RAM static, in special cind memoria este mare :

‑ Densitate mare : Pentru memoria RAM statica, o celula tipica necesita 6 tranzistoare MOS. Structura unei celule dinamice este mai simpla si poate fi implementata cu 3 sau chiar 1 tranzistor MOS. Ca urmare, se pot pune intr‑un singur chip mai multe celule de memorie si numarul de circuite de memorie necesar pentru a implementa un modul de memorie este redus. O dimensiune obisnuita pentru un circuit RAM dinamic este de 16Kx1 si sint de asemenea disponibile dispozitive de 64Kx1.

‑ Consum redus de putere : Consumul de putere pe bit de RAM dinamic este mult mai mic decit pentru RAM static. Disiparea puterii este mai mica de 0,05mW pe bit pentru RAM dinamic si este tipic de 0,2mW pe bit de RAM static. Aceasta caracteristica reduce necesitatile de putere ale sistemului si reduce costul. In plus, consumul de putere pe RAM dinamic este extrem de scazut in modul 'standby', ceea ce il face avantajos pentru proiectarea unei memorii nevolatile prin folosirea unei surse de putere (backup power source).

‑ Economie : Circuitele RAM dinamic sint mai ieftine pe bit decit cele de RAM static. Totusi, RAM‑ul dinamic necesita si alte circuite in plus si de aceea, ca economie nu apare nici un avantaj la construirea unor sisteme mici de memorie.

4.2. Celula de memorie si unitatea de memorie

O celula de memorie este blocul consecutiv al unei unitati de memorie. Desi se utilizeaza o diversitate de tehnologii, toate celulele de memorie semiconductoare reprezinta urmatoarele proprietati:

Au doua stari stabile (sau semi-stabile), care pot fi utilizate pentru a reprezenta valori binare 0 si 1.

Pot fi inscrise (cel putin o data) pentru setarea starii.

Pot fi citite pentru sesizarea starii.

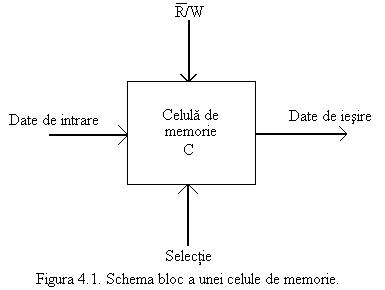

O schema bloc a unei celule care memoreaza un bit de informatie este prezentata in figura 4.1. Linia de selectie determina daca celula este selectata (validata), Linia R/W (Read/Write) determina daca trebuie efectuata o operatie de citire sau de scriere asupra celulei selectate. Atunci cand linia R/W este 0, se efectuiaza o operatie de citire, care determina trecerea datei memorate printr-un amplificator de detectie (sense amplifier) si transmiterea acesteia pe linia de iesire. Intr-un mod similar, atunci cand linia R/W este 1, se efectuiaza o operatie de scriere, care determina ca data de pe linia de intrare sa fie memorata in cadrul celulei.

O celula de memorie poate fi construita utilizand un numar redus de tranzistoare (unul pana la sase tranzistoare, in functie de tehnologie). Restrictia principala asupra proiectaii unei celule este dimesiunea sa. Obiectivul este ca dimensiunea celulei sa fie cat mai redusa, astfel incat sa fie impachetate mai multe celule in spatiul disponibil din cadrul unei capsule.

Exista doua tipuri de memorii cu acces aleator, statice (SRAM) si dinamice (DRAM). Atat memoriile statice cat si cele dinamice sunt volatile, deci informatia memorata este pierduta atunci cand alimentarea cu energie este intrerupta. Memoriile statice constau din celule asemanatoare cu bistabile utilizate in proiectarea logica. Celulele memoriilor SRAM difera la bistabile in principal prin metodele utilizate pentru adresarea celulelor si transferul datelor. Se utilizeaza linii multifunctionale care minimizeaza complexitatea celulelor de memorare si numarul de conexiuni ale celulelor, facilitand astfel fabricarea matricelor 2D de celule de memorare cu dimensiuni mari. Memoriile statice retin datele atunci cand un cuvant este citit de acesta. De aceea aceste memorii au proprietatea ca citirea este nedistructiva.

Intr-o celula de memorie DRAM, starile 1 si 0 corespund prezentei sau absentei unei sarcini memorate intr-un condensator controlat de un circuit de comutare, de obicei un tranzistor. Condensatorul unei celule DRAM trebuie reincarcat periodic. Operatia de reincarcare a condensatoareloreste numita reimprospatare. Deci, o memorie DRAM trebuie sa contina un circuit de reimprospatare si sa alterneze operatiile de reimprospatare cu accesele normale la memorie. Datele continute in memoriile dinamice trebuie rescrise in locatia corespunzatoare de memorie dupa fiecare operatie de citire. De aceea, memoriile dinamice sunt caracterizate prin proprietatea ca citirea este distructiva.

Deoarece o celula de memorie DRAM poate fi construita utilizand un singur tranzistor, in timp ce o celula de memorie SRAM necesita pana la sase tranzistoare, la memoriile dinamice se obtine o densitate de memorare mai ridicata. In consecinta, o memorie RAM dinamica este mai putin costisitoare decat o memorie RAM statica corespunzatoare. Pe de alta parte, o memorie RAM dinamica necesita un circuit de reimprospatare. Pentru memorii de dimensiuni mari, costul fix al circuitului de reimprospatare ete mai mult decat compensat de costul variabil mai redus al celulelor RAM dinamice. Astfel, memoriile RAM dinamice sunt favorizate pentru memorii de dimensiuni mari. Un alt aspect este ca memoriile RAM statice sunt mai rapide decat memoriile RAM dinamice.

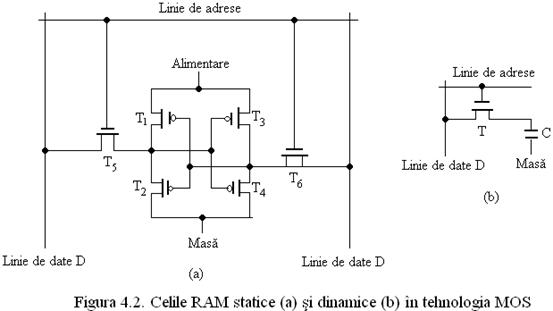

Pentru memoriile RAM se utilizeaza atat tranzistoare bipolare cat si MOS, dar MOS este tehnologia dominanta pentru memoriile de dimensiuni mari. Figura 4.2 prezinta exemplele de celule RAM MOS de tip static si dinamic. La celula statica (figura 4.2(a)), activarea semnalului de pe linia de adresa (numita si linia de cuvant) de catre decodificatorul de adresa selecteaza celula pentru operatia de citire sau scriere. Cele doua linii de date (numite si linii de bit) sau utilizate pentru transferu datei memorate si a complementului acestuia celula si driverele de date.

Figura 4.2(b) prezinta o celula simpla de memorie dinamica. Aceasta celula contine un tranzistor T in tehnologia MOS, avand rol de comutator, si un condensator C, care memoreaza un bit de date. Pe langa alimentare si masa, celula are doar doua conexiuni externe: o linie de date (bit) si o linie de adrese (cuvant). Pentru scrierea unei informatii in celula, se aplica un semnal 1 sau 0 pe linia de date. Se aplica apoi un semnal cu valoarea logica 1 pe linia de adrese pentru a comuta tranzistorul T. Aceasta actiune transfera o sarcina la condensatorul C daca linia de date este 1; nu se transfera nici o sarcina in caz contrar. Pentru citirea celulei, se activeaza linia de adresa, ceea ce va transforma sarcina memorata in condensatorul C pe linia de date unde aceasta este detectata. Deoarece produsul de citire este distructiv, data care este citita este amplificata si apoi rescrisa in celula; acest produs poate fi combinat cu operatia de reimprospatare periodica necesara pentru memoriile dinamice. Avantajele acestei celule DRAM sunt dimensiunea sa redusa si consumul de putere redusa.

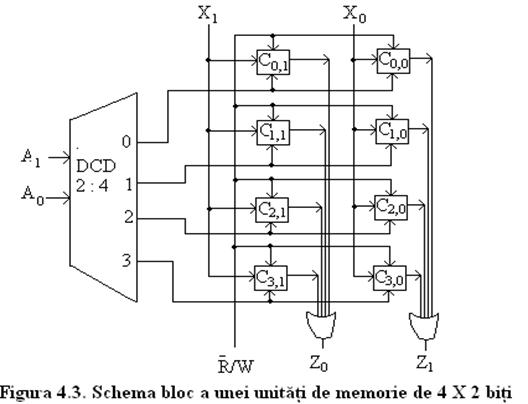

O unitate de memorie este o matrice de celule de memorie. Structura interna a unei unitati de memorie de m cuvinte si n biti pe cuvant consta din m * n celule de memorie. Intr-o unitate de memorie, fiecare celula poate fi adresata individual sau un grup de celule pot fi adresate simultan. De obicei, un sistem de calcul are o dimensiune fixa a cuvantului. Daca un cuvant are n biti, atunci trebuie adresate simultan n celule de memorie, ceea ce permite ca celulele sa aiba o linie selectie comuna. O unitate de memorie avand patru cuvinte de 2 biti este ilustrata in figura 4.3.

Oricare cuvant poate fi selectat cu ajutorul liniilor de adresa A1 si A0. Operatia care trebuie executata asupra cuvantului selectat este determinata de linia R/W. De exemplu, daca liniile de adresa A1 si A0 sunt selectate la 1, respectiv 0, este selectat cuvantul 2. Daca linia R/W este setata la 1, atunci datele de pe liniile de intrare de date X1 si X0 sunt memorate in celulele C2,1 , respectiv C2,0 . Similar, daca linia R/W este setata la 0, datele din celulele C2,1 si C2,0 sunt transmise pe liniile de iesire de date Z1 , respectiv Z0 .

4.3. Organizarea memoriilor

Fiecare circuit integrat de memorie contine o matrice de celule de memorie. Se utilizeaza mai multe organizari a celulelor de memorie li a gogicii functionale dintr-o capsula de memorie semiconductoare. Vom preyenta in continuare doua metode de organizare: 1D si 2D.

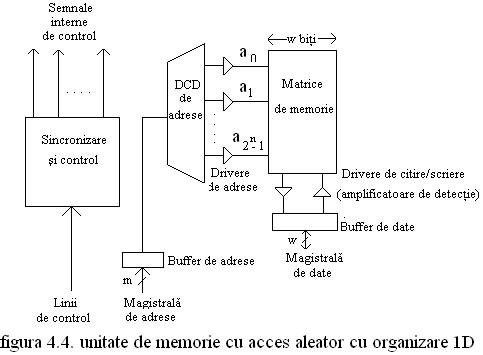

Figura 4.4. prezinta un exemplu de organizare 1D. Matricea de memorie este compusa dintr-un numar mare (2m) de locatii adresabile, fiecare din acestea memorand un cuvant de w biti. Bitii individuali nu sunt adresabili direct, exceptand cazul in care w = 1. O memorie de acest tip are capacitatea de 2m X w biti sau 2m cuvinte. Aceasta memorie functioneaza dupa cum urmeaza. Mai intai, adresa locatiei care trebuie accesata este transferata prin magistrala de adrese in bufferul de adrese al memoriei. Adresa este apoi decodificata de catre decodificatorul de adresa, care selecteaza locatia ceruta de matricea de memorie. O linie de control indicata tipul accesului care trebuie executat. Daca este ceruta o operatie de citire, continutul locatiei adresate este transferat de la matricea de memorie in bufferul de date si de aici pe magistrala de date in locatia selectata din unitatea de memorie. Daca este ceruta o operatie de scriere, cuvantul care trebuie memorat este transferat de pe magistrala de date in locuinta selectata din unitatea de memorie. Deoarece de obicei nu este necesar sau de dorit sa se permita citirea si scrierea simultana, magistralele de date (de intrare si de iesire) sunt combinate adesea intr-o singura magistrala bidirectionala de date.

Marticea de memorie este formata dintr-un numar mare de celule de memorie identice de 1 bit si interconexiunilel acestora. Numarul liniilor conectate la o celula si functiile lor depind de tehnologia memoriei si de metoda de adrese utilizata. Fiecare celula este conectata la un set de semnale de date, adrese si de control. O linie fizica are adesea mai multe functii logice; de exemplu, aceasta poate fi utilizata atat ca o linie de date, cat si de adrese. Pe fiecare linie conectata la matricea de memorie, exista de obicei un driver cu rol de amplificator de semnal. In figura 4.4 putem observa mai multe seturi de drivere pentru liniile de date si de adrese. Driverele, decodificatoarele si circuitele de control formeaza circuite de acces ale memoriei si acestea pot avea impact semnificativ asupra dimensiunii si costului memoriei.

Celulele de memorie sunt aranjate fizic in matrici regulate pentru a reduce costul conexiunilor intre celule si a circuitelor de acces. In general, adresa de memorie este partitionata in d parti astfel incat adresa Ai a celulei Ci devine un vector d-dimensional (Ai,1 , Ai,2 ,. . ., Ai,d) = Ai . Fiecare din cele d parti ale cuvantului de adresa este conectata la un codificator de adresa separat si un set separat de drivere de adresa. O celula este selectata activand simultan toate cele cele d linii de adrese ale sale. O unitate de memorie cu acest tip de adresare este numita d-dimensionala. Astfel, memoria din figura 4.4 este unidimensionala (1D).

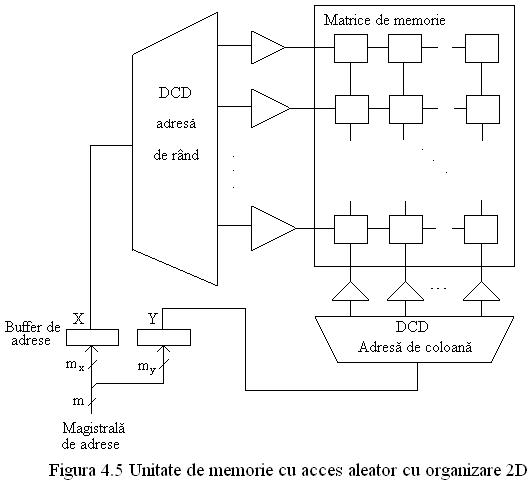

Cea mai obisnuita organizare de memorie este organizarea bidimensionala (2D) sau linia-coloana prezentata in figura 4.5., unde, pentru simplitate, circuitele de date si de control sunt omise. Cuvantu lde adrese de m biti este divizata in doua parti, X si Y, constand din mx , respectiv my biti. Celulele sunt aranjate intr-o matrice rectangulara de Nx<2mx linii si Ny<2my coloane, astfel ca numarul total cde celule este Nx Ny . Organizarea 2D necesita un numar mult mai redus de circuite de acces decat organizarea 1D pentru aceeasi capacitate de memorie. De exemplu, daca Nx= Ny=N, numarul driverelor de adresa necesare este 2N, in timp ce organizarea 1D din figura 4.4 este un numar de NxNy=N2 drivere de adresa. In locul unui singur decodificator de adresa 1:N2 , sunt suficiente doua decodificatoare de adresa 1:N. In plus, organizarea 2D favorizeaza structurile bidimensionalepermise de tehnologia VLSI.

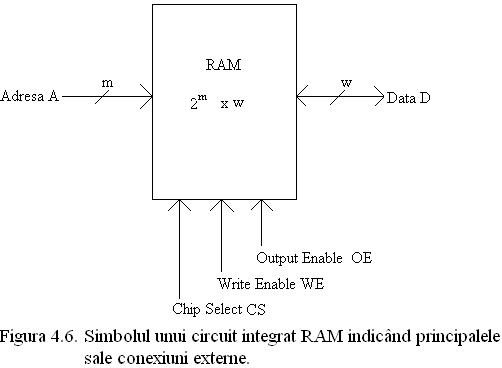

Un circuit integrat de memorie RAM contine in mod tipic toate circuitele de acces, incluzand decodificatoare de adresa, drivere si circuite de control. Figura 4.6 prezinta simbolul unui circuit generic de memorie RAM de 2m x w biti si identifica liniile sale de control. WE este linia de validare a scrierii (Write Enable); are loc o operatie de scriere(citire) a memoriei daca WE= 1(0). Linia de selectie a circuitului CS (Cip Select) activeaza o operatie cu memoria. Un cuvant este accesat pentru citire sau scriere numai atunci cand CS este activat. Aceasta linie semnalizeaza faptul ca magistrala de date are un cuvant pregatit pentru a fi inscris in memori RAM, sau, in cazul unei operatii de citire, faptul ca magistrala de date este pregatita pentru receptiona un cuvant de date. Memoria RAM din figura 4.6 are o magistrala bidirectionala de date D, care este concreta direct la toate locatiile adresabile de memorare, astfel incat necesita o a treia linie de control, de validare a iesirii OE (Output Enable). La operatiile de scriere (intrare) aceasta linie este dezactivata (OE = 0), permitand ca D sa aiba functia de magistrasa de intrare pentru toate locatiile de memorare. Numai locatia adresata memoreaza cuvantul receptionat pe magistrala de date. La operatiile de citire (iesire), OE este activat (OE = 1), astfel incat locatia de memorie adresata transfera datele sale pe magistrala de date D.

4.4. Parametri ai memoriilor DRAM

Timpul de acces (tA) reprezinta timpul scurs intre plasarea adresei de linie pe magistrala de adrese si momentul in care cuvantul solicitat apare in bufferul de iesire. Durata ciclului (tM) pentru un sir aleator de adrese este timpul minim intre operatiile secventiale de citire a memoriilor. Durata ciclului are o valoare mai mare decat timpul de acces, deoarece fiecare acces este urmat de o scriere interna pentru reancarcarea condensatorului celulei de memorie. Un alt motiv ca semnalele de control sunt dezactivate de sfarsitul unei operatii si ele trebuie reactivate pentru a incepe o noua operatie. Timpul necesar pentru rescrierea continutului memoriei si pentru reactivarea semnalului RAS este numit timp de preincarcare RAS (tRP - RAS Precharge time).

Considerand un acces pentru citire unei memorii DRAM, vor avea urmatoarele operatii:

Procesorul transmite adresa datei care trebuie accesata pe magistrala de adrese.

Controlerul de memorie determina adresele de linie si de coloana necesare pentru accesul datei in modulul de memorie.

Controlerul de memorie transmite prima parte a adresei (adresa de linie) la memorie se activeaza semnalul RAS. Ca urmare, decodificatorul adresei de linie selecteaza linia corespunzatoare in care este memorata data, sau citeste intreaga linie si o depune intr-un buffer. Timpul de acces la linie (tRA - Row Access time), numit si timp de acces aleator (random access time) sau timp de acces (tA), este timpul dintre activarea semnalului RAS si selectia liniei corespunzatoare sau prezenta datei solicitate in bufferul de iesire.

Controlerul de memorie transmite a doua parte a adresei (adrea de coloana) la memorie li activeaza semnalul CAS. Intarzierea intre semnalele RAS si CAS (tRCD - RAS-to-CAS delay) reprezinta perioada de timp dintre activarea semnalului RAS si activarea semnalului CAS. Ca rezultat al activarii semnalului CAS, decodificatorul adresei de coloana selecteaza coloana corespunzatoare in care este memorata data. Data solicitata va fi disponibila intr-o perioada de timp numita timp de acces la coloana (tCA - Colums Access time) de la activarea semnalului CAS. Pentru memoriile sincrone, se utilizeaza de obicei un alt parametru, care este strans legat de timpu lde acces la coloana: latenta semnalului CAS (CAS Latency - t CL sau CL), acest timp este exprimat ca un numar intreg de cicluri de ceas intre activarea semanlului CAS si momentul in care data solicitata este disponibila in bufferul de iesire.

Data selectata este transmisa din bufferul de iesire pe magistrala de date.

Timpul de acces aleator (tRA), numit si timp de acces (tA), poate fi calculat ca tRA = tRCD + tCA . De obicei, timpul de acces aleator este marcat pe capsulele DRAM prin -70, -60, -50 (sau -7, -6, -5). Aceste marcaje se refera la tRA ca fiind 70ns, 60ns, 50ns.

4.5. Tehnologii pentru memoriile DRAM

4.5.1. Categorii de memorii DRAM

Aproape toate tipurile de memorii DRAM au

aceeasi intarziere initiala pentru accesul la primul cuvant de

memorie (intre 50 ns si 60 ns), deoarece intern toate memoriile DRAM

functioneaza intr-un mod similar. Diferitele tipuri de memorii DRAM

utilizeaza tehnici diferite pentru executarea operatiilor

secventiale dupa citirea primului cuvant de memorie, cu rezultate

diferite in privinta performantelor obtinute. Majoritatea

castigurilor de performanta se obtin prin ''ascunderea''

operatiilor interne in diferite moduri.

Aproape toate tipurile de memorii DRAM au

aceeasi intarziere initiala pentru accesul la primul cuvant de

memorie (intre 50 ns si 60 ns), deoarece intern toate memoriile DRAM

functioneaza intr-un mod similar. Diferitele tipuri de memorii DRAM

utilizeaza tehnici diferite pentru executarea operatiilor

secventiale dupa citirea primului cuvant de memorie, cu rezultate

diferite in privinta performantelor obtinute. Majoritatea

castigurilor de performanta se obtin prin ''ascunderea''

operatiilor interne in diferite moduri.

Initial au fost utilizate memorii DRAM cu interfata asincrona, deoarece procesoarele erau relativ lente. Mai recent, a fost realizate interfate sincrone cu caracteristici avansate. Este posibil ca memoriile sincrone sa fie inlocuite prin memorii bazate pe protocoluri, cum ar fi Rambus DRAM.

O interfata asincrona este cea la care este necesara o perioada minima de timp pentru a asigura ca o operatie sa fie trminata. Fiecareia din operatiile interne ale unei memorii DRAM asincrone i se asigneaza intervalele minime de timp, astfel incat daca apare un impuls de ceas inainte de terminarea acestui interval minim, trebuie sa se astepte din nou impuls de ceas inainte ca urmatoarea operatie sa poata incepe. Din aceasta cauza, memoriile asincrone au performante limitate.

Pentru cresterea performantelor memoriileo asincrone, producatorii de memorii au crescut numarul de biti pe acces, au suprapus diferite operatii pentru minimizarea timpului necesar, sau au eliminat unele operatii pentru anumite tipuri de acces.

Utilizarea unor porturi de I/E cu un numar mai mare de biti reprezinta metoda cea mai simpla si cea mai eftina de crestere a performantelor. Un asemenea port necesita pini suplimentari de I/E, ceea ce implica o dimensiune mai mare a capsulei. Similar segmentarea aditionala a matricii de memorii si utilizarea mai multor linii de I/E creste dimensiunea circuitului. Ambele metode conduc la cresterea pretului memoriilor DRAM. Un alt dezavantaj este ca iesirile multiple determina la cresterea curentului absorbit, ceea ce reduce viteza, deoarece datele nu pot fi citite pana cand semnalele nu se stabilizeaza. Aceste probleme au limitat de obicei numarul liniilor de I/E la 4 sau 8, determinand ca proiectantii sa caute alte metode de crestere a performantelor.

Prin eliminarea unor operatii interne si suprapunerea diferitelor operatii au fost realizate mai multe tipuri de memorii DRAM asincrone, cum sunt memoriile FPM (Fast Page Mode), EDO (Extended Data Out) si BEDO (Burst Extended Data Out). Acestea sunt descrise in sectiunile urmatoare.

O alta categorie de memorii DRAM este cea care utilizeaza o intefata sincrona. Prin implementarea unei interfete sincrone, s-au eliminat perioadele de asteptare de catre procesor, obtinandu-se de asemenea unele avantaje suplimentare. In cazul functionarii sincrone, se memoreaza anumite informatii de la procesor in circuitele latch ale memoriei DRAM sub controlul ceasului sistem, Aceste circuite pastreaza adresele,datele si semnalele de control, ceea ce permite procesorului sa execute alte operatii. Dupa un numar specific de cicluri de ceas, datele devin disponibile si procesorul le poate citi de pe liniile de iesire.

Un alt avantaj al unei interfete sincrone este ca ceasul sistem este singurul semnal de sincronizare care trebuie furnizat memoriei DRAM. Aceasta elimina necesitatea propagarii unor semnale multiple de sincronizare. Intrarile sunt de asemenea simplificate, deoarece semnalele de control, adresele si datele pot fi memorate fara temporizarile de stare si mentinere monitorizate de procesor. Avantajele similare se obtin si pentru operatiile de iesire.

Toate memoriile DRAM care au o interfata sincrona sunt cunoscute sub numele generic SDRAM. Acestea cuprind JEDEC SDRAM, PC100 SDRAM, DDR SDRAM (Double Data Rate SDRAM), CDRAM (Cache DRAM), ESDRAM (Enhanced SDRAM) si altele.

O alta categorie este reprezentata de memoriile DRAM bazate pe protocoale. Categoriile precedente de memorii au linii separate de adrese, date si control, care limiteaza vitaza la care poate functiona circuitul cu tehnologia curenta. Pentru eliminarea acestui dezavantaj, au fost proiectate memorii DRAM bazate pe protocoale, care implementeaza toate aceste semnale pe aceiasi magistrala. Cele mai cunoscute memorii din aceasta categorie sunt DRDRAM (Direct Rambus DRAM) si SLDRAM (SyncLink DRAM).

4.5.2. FPM DRAM

Prin implementarea unor moduri speciale de acces, se pot elimina anumite operatii interne pentru anumite tipuri de acces. Prima implementare de acest tip este numita acces in mod pagina (Page Mode), care a fost prezentata in sectiunea 4.4.1. Prin aceasta metoda, semnalul RAS este mentinut activ, astfel incat o intreaga linie de date (sau o pagina) este mentinuta in bufferele interne de coloana. Continutul acestor buffere poate fi apoi accesat doar prin ciclarea semnalului CAS. Aceasta asigura operatii operatii de citire mult mai rapide, deoarece timpii de setare si mentinere pentru adresa de linie sunt eliminati. Acest tip de acces este avantajos doar pentru unele operatii.

Memoria Fast Page Mode (FPM) utilizeaza o imbunatatire a accesului in mod pagina prin eliminarea timpului de setare a adresei de coloana in timp ciclului de pagina. Aceasta sa realizatprin activarea bufferelor pentru adresele de coloana pe frontul descrescator al semnalului RAS, si nu al semnalului CAS. Deoarece semnalul RAS ramane in starea logica 0 pe durata intregului ciclu de pagina., aceasta permite ca setarea adresei sa se realizeze de indata ce adresa de coloana este valida, fara a se astepta frontul descrescator al semnalului CAS.

Memoria FPM este putin mai rapida decat memoria DRAM conventionala. Avantajul acestei memorii este consumul de putere redus, in principal datorita faptului ca in timpul accesului in mod pagina refacerea continutului celulelor nu ete necesara. Desi memoria FPM a reprezentat o inovatie fata de memoria DRAM conventionala, are si anumite dezavantaje. Cel mai important dezavantaj este ca bufferele se dezactiveaza atunci cand CAS devine 1 logic, ceea ce creste durata ciclului cu cel putin 5 ns.

4.5.3. EDO DRAM

Memoria EDO (Extended Data Out), numita si memoria HzperPage Mode, reprezinta o alta imbunatatire a memoriei DRAM asincrone. In cazul memoriei EDO, o operatie de citire poate incepe inainte de terminarea ultimuluui acces. Bufferele de iesire nu se dezactiveaza la frontul crescator al semnalului CAS. Aceasta permite ca durata minima a ciclului pentru semnalul CAS sa fie redusa.

Memoria EDO utilizeaza aceleasi dimensiuni a capsulei ca si memoria DRAM conventionala Costurile de productie a memoriei EDO esste aceeasi ca si cele ale memoriei FPM. Imbunatatirea performantelor fata de memoria FPM este in jur de 5 pana la 10%. Memoria EDO asigura performante corespunzatoare cu magistrale de memorie avand fregvente de pana la 83 MHz. In cazul in care circuitele cunt suficient de rapid (cu timpi de acces de 55 ns sau mai mici), memoria EDO poate fi utilizata chiar si cu o magistrala de memorie de 100 MHz. Unul din avantajele memoriei EDO este ca toate seturile de circuite ale placilor de baza actuale permit utilizarea acesteia fara probleme de compatibilitate, spre deosebire de unele memorii utilizate actualmente.

4.5.4. BEDO DRAM

In cazul memoriei BEDO (Burst EDO), Memoria EDO este combinata cu tehnologia pipeline s icircuite latch speciale pentru a reduce timpul de acces. Adaugarea unui mod de transfer expliziv (''burst'') si utilizarea unei arhitecturi cu bancuri duale asigura o temporizare de 4-1-1-1 la 66 MHz. Modul de transfer exploziv este o imbunatatire a modului pagina, deoarece dupa furnizarea primei adrese urmatoarele 3 adrese sunt generate intern, eliminandu-se timpul necesar furnizarii unei noi adrese de coloana.

4.5.5. SDRAM

Toate memoriile care nu au interfata sincrona sunt cunoscute sub numele generic SDRAM (Synchronous DRAM). Aceste memorii cuprind PC100, SDRAM, PC133 SDRAM, DDR SDRAM, CDRAM, ESDRAM si altele. Totusi tipul de memorie care se numeste tot mai adesea SDRAM este memoria sincrona elaborata conform standardului JEDEC (Joint Electron Devive Engineering Council). JEDEC este un comitet al asociatiei Industriei Electronice din S.U.A., care elaboreaza standarde electrice pentru incapsulare, configuratia pinilor si alte caracteristici ale dispozitivelor semiconductoare.

Principiul memoriei SDRAM.

Memoria DRAM sincrona este complet diferita in ceea ce priveste arhitectura sa si metodele de control fata de memoria DRAM asincrona. Prima diferenta este configuratia memoriei SDRAM, care utilizeaza o arhitectura cu unitati (bancuri) multiple. Modulele tipice SDRAM, au 2 sau 4 bancuri pe modul, permitand ca un banc sa fie preancarcat in timp ce celelante sunt citite sau scrise. Altfel, nu numai ca timpii de preincarcare sunt mascati, dar pot fi accesate simultan linii multiple in fiecare banc al memoriei.

A doua diferenta este ca memoria SDRAM poate functiona in mod exploziv pentru 1 bit, 2 biti, 4 biti, 8 biti, sau o pagina completa. In mod exploziv, la fiecare tranzactie cu memoria se transfera mai multe locatii cu adrese consecutive. Modul exploziv este avantajos deoarece instructiunile si datele sunt in ordine secventiala in majoritatea timpului. De exemplu , atunci cand este prezenta o memorie cache L2, sunt transferate blocuri de memorie de dimensiune fixa, continand cuvinte cu adrese consecutive. Modul exploziv este controlat printrun registru de mod care poate fi setat la punerea sub tensiune si poate fi modificat in timpul functionarii. Acest registu controleaza tipul transferului exploziv (secvential sau intretesut), lungimea transferului exploziv si latenta semanlului CAS.

Un alt factor care deosebeste memoria DRAM sincrona de memoria DRAM asincrona este metoda de control. Memoria DRAM asincrona este controlata de setul de circuite pe baza relatiei de temporizare dintre semnalele RAS, CAS, WE si OE.Memoria DRAM sincrona este controlata prin comenzi care sunt plasate pe magistrala, acestea fiind interpretate pe frontul crescator al semnalului de ceas.

Viteza memoriilor SDRAM este exprimata prin MHz, si nu in nanosecunde. Astfel exista o corespondenta intre viteza magistralei si viteza memoriilor, deoarece teoretic memoria SDRAM permite functionarea fara stari de asteptare, la o rata de un ceas pe ciclu de ceas, dupa o intarziere intiala. O indicatie a vitezei este durata ciclului de ceas, care este marcato deobicei pe capsulele de memorie. De exemplu, calori ca -12, -10 sau -8 aflate pe o capsula SDRAM indica durata minima a ciclului de ceas pentu componenta respectiva, in ns. O valore -10 inseamna ca frecventa maxima a ceasului de memorie este de 100 MHz.

Tipuri de memorii SDRAM

Memorile SDRAM originale nu functionau corespunzator la frecvente de peste 83 MHz. Unele module SDRAM deveneau instabile chiar la o frecventa a magistralei de 83 MHz. Pentru a solutiona aceasta problema, in 1998 firma Intel a introdus specificatia PC100 ca un ghid pentru ca producatorii sa construiasca module care sa functioneze corect pe o magistrala sistem de 100 MHz, utilizand setul de circuite i440BX al Intel. Prin specificatia PC100, Intel a elaborat un numar de recomandari pentru lungimea si latimea traseelor, spatiul dintre acestea, numerele de straturi ale placii imprimate, specificatii pentru programarea memoriei EEPROM (SPD) etc. O memorie SDRAM care se conformeaza acestei specificatii este numita memorie PC100. In mod ideal , memoria PC100 poate atinge o temporizare de 4-1-1-1. La o frecventa de 100 MHz, exista 100 . 106 cicluri de ceas pe secunda si se poate transfera maxim un cuvant (8 octeti) in fiecare ciclu. Rata de transfer maxima teoretica este deci de 800 MB/s.

Deosebiri SRAM/DRAM

Principalul avantaj al memoriei dinamice (DRAM) este pretul foarte redus pentru obtinerea unei celule. De altfel, acesta este si singurul plus pe care aceasta memorie il are in comparatie cu SRAM. In schimb performantele sint cu mult in urma memoriei statice (SRAM). Datorita modului prin care se comuta intre starile 0 si 1 si a modului in care se executa citirea celulei de memorie, SRAM nu are nevoie de rescriere a datelor dupa ce acestea au fost citite si nici de reimprospatarea celulei de memorie. Atfel ca timpii de acces sint mult mai mici iar viteza la care acest tip de memorie lucreaza depaste cu mult performantele memoriei dinamice. Datorita pretului de cost mare pentru obtinerea unei celule SRAM, acest tip de memorie este utilizat numai pentru fabricarea memoriei cache ce se implementeaza in placile de baza sub denumirea de cache level 2 (L2) ori pentru memoria cache level 1 (L1) ce este integrata in structura procesoarelor. Memoria cache L1 functioneaza la aceasi frecventa cu cea a procesorului in timp ce pentru memoria cache L2 frecventa de lucru este jumatate fata de frecventa procesorului. Memoria cache a fost introdusa ca un artificiu tehnologic, care trebuie sa suplineasca diferenta de frecventa dintre procesor si memorie.

4.5.6. HSDRAM

Memoria HSDRAM (High Speed SDRAM) utilizeaza circuite de memorie de calitate ridicata in scopul cresterii frecventei peste cea a memoriei SDRAM conventionale. Anumite circuite de memorie HSDRAM pot functiona mai fiabil si cu incalziri mai reduse la 133 Mhz, iar altele pot functiona la frecvente de 150 MHz sau 166 MHz. Memoria HSDRAM este compatibila cu memoria SDRAM conventionala, imbunatatind in acelasi timp performanta so stabilitatea sistemelor. Aceasta memorie era destinata initial sistemelor cu performante ridicate, cuprizand calculatoare personale, statii de lucru, servere, sisteme DSP si sisteme grafice. Ulterior, circuoitele de memorie HSDRAM se prezinta caracteristicile principale ale circuitelor de memorie, ca ESDRAM si DDR SDRAM.

Ca exemple de circuite de memorie HSDRAM se prezinta caracteristicile principale ale circuitelor SM 3603 si SC3604, care au fost produse de firma Enhanced Memory System in anul 1999.

Latente de functionare la 133 MHz: 3:2:2 (latenta semnalului CAS.)

Timp de acces de la semnalul de ceas: tRA = 34,6 ns;

Timp de aces aleator

Durata ciclului aleator

Latenta semnalului CAS este programabila (1,2,3)

4.4.7. ESDRAM

In scopul imbunatatirii performantei modulelor de memorii SDRAM conventionale, unii producatori au inclus o memorie statica SRAM in capsulele de memorie, acestea avand rolul unei memorii cache. O asemenea memorie este ESDRAM (Enhanced SDRAM), dezvoltata in anul 1997.

Memoria ESDRAM consta dintro memorie SDRAM si o memorie cache de linie. Aceasta memorie cache cu mapare directa pastreaza continutul liniei active, eliberand atunci matricea de memorie DRAM, astfel ca aceasta poate accesa o alta linie in timp ce continutul liniei precedente este transferat in bufferele de iesire. Principiul ete ca , in loc de a se incerca reducerea intarzierilor prin utilizarea unor componente mai rapide aceste intarzieri sunt ascunse prin suprapunerea anumitor operatii.

Intr-o memorie SDRAM conventionasa, datele trebuie refacute prin rescrierea continutului unei linii inainde de a putea activa o alta linie . Memoria ESDRAM suprapune transferul in mod exploziv al datelor dinb memoria cache de linie in bufferele de iesire cu operatia de preincarcare. Aceasta se numeste auto-preincarcare timpurie. Astfel timpul de reancarcare RAS este eliminat. De obicei, o matrice ESDRAM permite activarea simultana a mai multor linii(pagini).

4.4.8 Memoria FCRAM

FCRAM (Fest Cycle RAM) este o tehnologie dezvoltata de firma Fujitusu Microelectronis. Fiecare banc de memorie FCRAM este subdivizat in mini-zone. Aceasta subdiviziune imbunatateste timpul de acces aleator si reduce puterea consumata coparativ cu memoria SDRAM conventionala. Se utilizeaza o arhitectura pipeline cu trei etaje, care permite ca urmatorul acces aleator sa inceapa in timp ce data precedenmta este transmiss la iesire. Un set de operatii care specifica o adresa poate fi urmat imediat de operatia urmatoare fara a fi necesar sa se asteprte transmiterea datelor la iesire. Astfel operatia de preincarcare poate fi executata automat de memoria pe masura ce operatiile sunt terminate. Deci operatia de preincarcare este ascunsa.

Tehnologia FCRAM a fost dezvoltata pentru a imbunatati in mod semnificativ performantele la accesurilor aleatoare chiar si la frecvente reduse, prin reducerea ciclurilor inactive ori de cate ori este posibil. Ca rezultat, gradul de utilizare efectiva a magistralei va creste. Memoria FCRAM poate functiona cu o latenta a semnalului CAS egala cu 1, valoarea care nu este permisa de obicei de memoria SDRAM conventionala.

4.4.9. DDR SDRAM

Prezentare generala

Numele memoriei DDR (Double Data Rate) SDRAM provine de la tehnica transferarii datelor atat pe frontul crescator cat si pe cel descrescator al semnalului de ceas. De exemplu, la o frecventa a magistralei de 133 MHz memoria DDR SDRAM executa transferulrile de date la o frecventa de 266 MHz. Aceasta tehnica creste semnificativ eficienta magistralei de memorie pentru transferurile de date. Un model de memorie DDRAM

4.9.10.Memoria intermediara - cache

De-a lungul timpului, UCP-urile au fost intotdeauna mai rapide decat memoriile. Odata cu imbunatatirea memoriilor se imbunatateau si UCPurile, pastrand dezechilibrul. De fapt, odata cu posibilitatea plasarii a tot mai multe circuite pe un singur cip, proiectantii UCP folosesc aceste noi facilitati pentru benzi de asamblare si operare superscalara, facand UCPurile sa mearga si mai rapid. Proiectantii memoriilor au folosit de obicei noile tehnologii pentru a creste capacitatea cipurilor lor, nu viteza, asa ca problema pare sa se inrautateasca in timp. Semnificatia practica a acestui dezechilibru este aceea ca dupa ce UCP a lansat o cerere catre memorie, nu va primi cuvantul asteptat timp de multe cicluri UCP. Cu cat memoria este mai lenta, cu atat are UCP mai mult de asteptat. Se pot construi memorii la fel de rapide ca si UCP-urile, dar pentru ca acestea sa functioneze la viteza maxima ar trebui sa fie incorporate in cipul UCP (deoarece transferul pe magistrala este foarte lent). Plasarea unei memorii mari pe cipul UCP ii creste dimensiunile, deci ii creste costul, si chiar daca acesta nu ar fi fost o problema, un cip UCP nu poate depasi anumite limite ale dimensiunilor. Astfel alegerea se reduce la putina memorie rapida sau multa memorie lenta. Ce am prefera ar fi multa memorie rapida la un pret scazut. Solutia este o tehnica de combinare a unei cantitati mici de memorie rapida cu o cantitate mare de memorie lenta, astfel incat sa se obtina viteza memoriei rapide (aproape) si capacitatea celei mari la un pret moderat. Memoria mica, rapida, se numeste memorie

intermediara - cache. Ideea de baza a unei memorii intermediare este simpla: cuvintele de memorie cele mal frecvent utilizate sunt pastrate in memoria intermediara. Atunci cand UCP are nevoie de un cuvant, il cauta mai intai in memoria

intermediara. Numai daca nu il gaseste acolo il cauta in memoria principala. Daca un procent substantial de cuvinte se afla in memoria intermediara, timpul mediu de acces poate fi redus semnificativ. Succesul sau esecul depind de cantitatea de cuvinte care se afla in memoria intermediara. Programele nu acceseaza memoria complet la intamplare. Daca o anumita referire la memorie este la adresa A, este foarte probabil ca urmatoarea referire la memorie sa se afle in vecinatatea lui A. Un exemplu simplu este insusi programul. Cu exceptia ramificarilor si a apelurilor de proceduri, instructiunile sunt extrase din locatii de memorie consecutive. Mai mult, majoritatea programelor isi petrece timpul in cicluri, unde un numar limitat de instructiuni este executat iar si iar.

Memoria RAM VIDEO

O parte din memoria RAM superioara este utilizata de catre adaptoarele video. Aici este memorata imaginea (text sau grafica) ce urmeaza a fi afisata pe ecranul monitorului. Datorita nevoii constante de reimprospatare, memoria DRAM este mai lenta. Din acest motiv, noile adaptoare video folosesc o memorie specializata VRAM - Video RAM, situata pe placa video, mult mai rapida, dar si mai scumpa. Memoria video se gaseste pe adaptorul grafic si este folosita pentru stocarea imaginii ce apare pe monitor. Deoarece aceasta memorie este accesata de doua ori (de catre microprocesor - pentru a stoca informatia ce trebuie afisata pe ecran si de catre controller-ul video - pentru a citi informatia si a o transmite pe monitor), au fost create tipuri speciale de memorii numai pentru interfetele grafice

Memoria tampon pentru imprimanta - PRINTER BUFFER

Memoria tampon in care sunt stocate temporar (pana cand imprimanta Ie poate prelua) informatiile ce urmeaza a fi tiparite la imprimanta se numeste printer buffer. In acest mod calculatorul nu este blocat pe parcursul tiparirii; datele sunt transmise in memoria tampon pentru imprimanta, dupa care calculatorul isi poate relua lucrul.

Memoria RAM SHADOW

Microcalculatoarele bazate pe microprocesoare 386, 486 sau Pentium, care acceseaza memoria RAM pe magistrale de 32 sau 64 de biti, utilizeaza deseori o magistrala de 16 biti pentru memoria ROM, ceea ce reduce performantele sistemului. In plus, viteza de acces la memoria ROM este mult inferioara (150-200 ns), fata de viteza de acces la memoria DRAM (60 ns). Pentru a reduce numeroasele stari de asteptare datorate cererilor de acces la

date sau programe stocate in memoria ROM, informatiile din memoria ROM sunt duplicate in memoria RAM. Aceasta operatie este realizata de o componenta foarte puternica incorporata in microprocesoarele 386, 486, Pentium, denumita MMU - Memory Management Unit, Unitate de gestiune a memoriei. Memoria RAM in care s-a efectuat copierea se numeste memorie RAM shadow si este protejata la scriere,

comportandu-se ca o memorie ROM obisnuita. Memoria CMOS

Memoria CMOS - Complementary Metal-Oxide Semiconductor, semiconductor complementar din oxid metalic este o memorie de tip RAM speciala. Spre deosebire de memoria RAM obisnuita, care este volatila, memoria CMOS este semipermanenta, fiind alimentata la baterie. Evident, daca decuplati bateria, continutul memoriei CMOS se pierde si datele trebuie reincarcate sau transferate de pe un disc (daca au fost salvate in prealabil). Memoria CMOS poate fi scrisa si citita prin programul SETUP si contine informatii despre configuratia sistemului (de exemplu, memoria sistemului, numarul si tipul unitatilor de floppy si de hard-disc, tipul adaptorului video, etc). Tot in memoria CMOS sunt stocate data si ora curenta.

5. Memorii ROM programabile

Memoriile Rom sunt circuite de memorie ale caror continut este programat la fabricare si nu poate fi schimbat de utilizator. Ea este constituita dintr-un tranzistor cu efect de camp a carui tensiune de prag difera in functie de continutul informational al locatiei respective.

Daca la aplicarea unui impuls pozitiv pe grila tranzistorul conduce atunci el se comporta ca un scurtcircuit drena sursa, informatia inscrisa fiind 0 logic; daca ramane blocat atunci avem 1 logic.

Obtinerea unor tranzisotare cu tensiuni de prag diferite se face printr-un strat de oxid de grosime corespunzatoare intre grila tranzistorului si substrat.

Exista si memorii ROM-PROGRAMABILE (PROM si EPROM). Memoriile PROM sunt circuite de memorie al caror continut este programat o singura data de utilizator. Dupa inscriere informatia nu mai poate fi stearsa. Celula de memorie a unor astfel de circuite au la baza un fuzibil din polisiliciu care este ars la programare. Celula de baza a unei memorii PROM este realizata cu tranzistoare bipolare.

Initial toate fuzibilele memoriei sunt scurtcircuitate. Programarea unei celule inseamna arderea fuzibilului din nodul respectiv. Pentru programare se aplica impuls pozitiv pe baza, iar linia de bit DL se mentine la potential coborat. Curentul de emitor al tranzistorului, suficient de mare, produce arderea fuzibilului F. Programarea se face succesiv pe fiecare celula, selectia unei celule facandu-se prin liniile WL si DL.

Memoriile EPROM se folosesc pentru realizarea celulei de memorie un tranzistor cu efect de camp cu dubla poarta (grila), una comanda si una izolata.

Daca pe poarta izolata este acumulata

sarcina electrica negativa atunci aplicarea unor tensiuni pozitive pe grila a

doua (Vc) nu poate aduce in stare de conductie tranzistorul. Daca pe poarta izolata nu este acumulata o

sarcina atunci aplicarea tensiunii pozitive pe Vc creaza un camp care duce la

formarea canalului "n" si la linia de bit este 1 cand tranzistorul e jectarea de sarcini negative pe grila izolata se

face prin aplicarea unei tensiuni drena, si o tensiune pozitiva pe grila.

Tensiunea Vds mare, duce la campul electric intern intens, trec prin stratul de

oxid foarte subtire si se acumuleaza in grila izolata. Pentru stergerea

informatiei din celula si revenirea in stare neprogramata (tranzistor blocat)

se expune circuitul la actiunea radiatiei ultraviolete. Electronii din grila

preiau energie de la radiatie si trec inapoi in substrat prin stratul izolator.

Daca pe poarta izolata este acumulata

sarcina electrica negativa atunci aplicarea unor tensiuni pozitive pe grila a

doua (Vc) nu poate aduce in stare de conductie tranzistorul. Daca pe poarta izolata nu este acumulata o

sarcina atunci aplicarea tensiunii pozitive pe Vc creaza un camp care duce la

formarea canalului "n" si la linia de bit este 1 cand tranzistorul e jectarea de sarcini negative pe grila izolata se

face prin aplicarea unei tensiuni drena, si o tensiune pozitiva pe grila.

Tensiunea Vds mare, duce la campul electric intern intens, trec prin stratul de

oxid foarte subtire si se acumuleaza in grila izolata. Pentru stergerea

informatiei din celula si revenirea in stare neprogramata (tranzistor blocat)

se expune circuitul la actiunea radiatiei ultraviolete. Electronii din grila

preiau energie de la radiatie si trec inapoi in substrat prin stratul izolator.

Memoriile EEPROM folosesc un principiu

asemanator, numai ca pentru trecerea electronilor stratul izolator utilizeaza

efectul tunel (1s). Celula de memorie pentru acest tip de circuit este formata

din doua tranzistoare TEC obisnuite si un tranzistor care este de tip TEC-MOS.

Intr-o celula de memorie stearsa, grila izolata este incarcata cu sarcina

negativa si tranzistorul este blocat.

Memoriile EEPROM folosesc un principiu

asemanator, numai ca pentru trecerea electronilor stratul izolator utilizeaza

efectul tunel (1s). Celula de memorie pentru acest tip de circuit este formata

din doua tranzistoare TEC obisnuite si un tranzistor care este de tip TEC-MOS.

Intr-o celula de memorie stearsa, grila izolata este incarcata cu sarcina

negativa si tranzistorul este blocat.

Stergerea informatiei din celula se face astfel: se aplica tensiunea pozitiva (+20 V) pe linia de selectie cuvant punand in conductie tranzistorul T. Drena acestuia se conecteaza la potential zero si se aplica +20V pe linia de programare. Datorita campului electric intern mare. Electronii care trec din substrat prin efect tunel si se acumuleaza in grila izolata, formand o sarcina negativa.

Inscrierea informatiei in celula se face aplicand +20V pe linia selectie cuvant (WL) si +18V in drena tranzistorului in timp ce linia de programare este la potential zero. Campul electric format intre grila si substrat (substrat, grila) smulge electroni din grila a doua, aceasta acumuleaza sarcina pozitiva si tranzistorul intra in conductie prin formarea canalului "n" intre drena si sursa.

PROTECTIA MUNCII

Dispozitii generale:

Art. I:

1. Protectia muncii constituie un ansamblu de activitati institutionalizate avand ca scop asigurarea celor mai bune conditii in desfasurarea procesului de munca: apararea vietii, integritatii corporale si sanatatii salariatilor si altor persoane participante la procesul de munca.

2. Normele de protectie a muncii stabilite prin prezenta legii reprezinta un sistem unitar de masuri si aplicabilitate tuturor participantilor la procesul de munca.

3. Activitatea de protectie a muncii asigura aplicarea criteriilor economice pentru imbunatatirea conditiilor de munca si pentru reducerea efortului fizic precum si marimi adecvate pentru munca femeilor si a tinerilor.

Art.II:

1. Prevederile prezentei legii se aplica tuturor persoanelor juridice si fizice la care activitatea se defasoara cu personal angajat pe baza de contract individual de munca sau in alte conditii prevazute de lege.

2. In sensul prezentei legii, prin persoane juridice si fizice se intelege: agentii economici din sectorul public.

Art.III

1. Normele de protectie a muncii se aplica salariatilor, persoanelor angajate cu conventii civile, ucenicilor, elevilor, studentilor.

Art. IV:

1. Ministerul Muncii Sociale si Ministerul Sanatatii, prin organele lor de specialitate organizeaza, controleaza si coordoneaza activitatea de protectie a muncii.

2. Cercetarea, inregistrarea si evidenta accidentelor de munca si a bolilor profesionale, precum si autoirzarea din punct de vedere al protectiei muncii a unitatii din subordonarea ministerului si serviciilor mentionate se efectuiaza de catre organele proprii.

Art. V:

1. M.M.P.S. emite norme generale normative si alte reglementari de interes national, privind securitatea muncii si alte domenii ale protectiei muncii potrivit legii pentru toate unitatile, coordoneaza programarea de elaborare a normelor specfice.

2. Normele generale de protectia muncii cuprind reguli si masuri aplicabile in intreaga economie nationala.

3. Domeniile pentru care se elaboreaza normele generale de protectie a muncii sunt cuprinse in anexa 1 la prezenta legii.

4. Comisia Nationala pentru Controlul Activitatilor Nucleare, elaboreaza norme specifice A.Nucleare si exercita controlul cu privire la respectarea acestora.

5. Activitatea din economia nationala pentru care se elaboreaza norme specifice de protectie a muncii sunt cuprinse in anexa numarul 2 la prezenta legii.

6. Persoanele fizice si juridice sunt obligate sa elaboreze instructiuni proprii de aplicare a normelor de protectie a muncii in functie de particularitatile procesului de munca.

Art.VI:

1. M.S. emite norme obligatorii privind igiena muncii si avizeaza standarde si acte normativ elaborate, alte organe care care privesc sanatatea la locul de munca.

2. Domeniile pentru care se elaboreaza normele de igiena a muncii sunt cuprinse in anexa 1 la prezenta legii.

Art. VII:

1. Contractele colective de munca ce se incheie la nicelul activitatilor grupului de unitati, ramurilor de activitati precum si la nivelul national vor cuprinde obligatoriu clauza referitoare la protectia muncii in conformitate cu prevederile prezentei legii a caror aplicare e sa asigure prevenirea accidentelor de munca si a bolilor profesionale.

2. In contractele individuale de munca in conventii civile cu exceptia celor care au drept obiect activitati cosmice precum si contractelele de scolarizare vor fi stipulate clauze privind protectia muncii stabilindu-se si raspunderea muncii.

3. Conventiile internationale si contractele bilaterale incheiate de persoane juridice romane cu parteneri straini in vederea efectuarii de lucrari, persoanele romane pe teritoriul altor tari vor cuprinde clauze privind protectia muncii.

Art. VIII:

1. In reglementele privind organizarea si functionarea persoanelor juridice vor fi stabilite obligatii si raspunderi in domeniul protectiei muncii in conformitate cu prevederile prezentei muncii.

2. In functie de natura, complexitatea si riscrile specifice activitatii desfasurate, precum si de limba salariatilor, persoanele juridice vor stabili personalul cu atributii in domeniul protectiei muncii sau dupa caz vor organiza compartimente de protectie a muncii.

Art. IX:

1. Desfasurare activitatii de productie sau a prestatiilor de servicii este conditioanta de obtinerea autorizatiei de functionare din punct de vedere al p.m. emisa de catre inspectoratele de stat teritoriale pentru protectia muncii din subordinea organelor si a serviciilor prevazute in articolul IV aliniatul 2.

Art. X:

1. Cheltuielile oferite realizarii masurarii de protectie a muncii sunt finantate integral din costurile de produnctie a persoanelor juridice finantate de la bugetul de stat, respectiv din bugetul local.

Art. XI:

1. Activitatile de interes netional in domeniul protectiei muncii si surselor de acoperire a cheltuielilor necesare realizarii acestora se aproba de catre Guvern la propunerea M.M. si P.S.

2. Activitatile de cercetare stiintifica in domeniul protectiei muncii de interes national se finanteaza din fondurile prevazute pentru acestea potrivit legii.

Echipanentele tehnice. Echipementul individual si de lucru.

Alimentatia de protectie. Materiale igienico-sanitare.

Art. XII:

1. In sensul aplicarii legii sunt: masinile, utilajele, instalatiile, aparatura, dispozitiele, uneltele si alte mijloace asemanatoare, necesare in procesul muncii.

2. Echipamentele tehnice trebuie sa corespunda prevederile din normele, standardele si din reglenemtari referitoare la protectia muncii si sa nu reprezinte pericol pentru sanatatea sau viata salariatilor, a persoanelor aflate in unitate in nteres de serviciu, sau a altor persoane care se asigure protectia muncii potrivit prevederilor din articolul III.

3. Echipamentele tehnice din produnctia interna si din import trebuie sa fie dotate cu aparatura de masura si control al parametrilor tehnologiei, precum si de prevenire si avertizare a starilor de pericol.

4. Echipamentele tehnice pot fi fabricate, importate, comercializate si folosite numai daca indeplinesc conditii de protectia muncii, certificate de organele competente potrivit legii.

Art. XIII:

1. In sensul prezentei legii echipamentul de protectie individual cu care este dotat fiecare participant in procesul de munca pentru a fi protejat impotriva factorilor de risc.

2. Echipamentul individula de protectie se acorda obligatoriu si gratuit salariatilor, precum si altor categorii de persoane ce desfasoara activitati la persoanele juridice sau fizice prevazute la articolul II.

3. In cazul degradarii echipamentului individual de protectie respectiv al pierderii calitatii de productie, se acorda obligatoriu un nou echipament.

4. Degradarea sau pierdera echipamentului individual de protectie inainte de termenul de utilizare, prevazut din vina purtatorului, atrage raspunderea acestuia pentru prijudiciul cauzat, potrivit legii.

Art. XIV:

1. In sensul prezentei legii, individual de lucru, reprezinta mijloacele pe care persoanele juridice si fizice le acorda unui salariat in vederea utilizarii lor in timpul procesului de munca pentru a le proteja imbracamintea si incaltamintea.

2. Echipamentul individual de lucru se acorda de catre persoane juridice in conditii negiciate prin contractele colective de munca.

3. Cheltuielile necesare achizitionarii echipamentului individual de lucru sunt suportate, in proportie de 50% catre persoana juridica, din costurile de productie, sau din buget pentru unitatie finantate de la bugetul de stat, respectiv din bugetele locale, iar diferenta se suporta de catre beneficiari.

Art.XV:

1. Unitatile de productie de echipament individual de protectie si de echipament individual de lucru sunt obligate sa respecte conditiile de realizare a sortimentelor prevazute in standardele romane corespunzatoare.

2. Introducerea in fabricatie a sortimentelor noi de echipament individual de protectie si de lucru se poate face numai dupa avizarea prototipurilorde catre M.M. si P.S.

3. Sortimentele de echipament individual de protectie si de lucru, din import, pot fi comercializate si utilizate numai dupa certificare calitatii de productie a acestora de catre M.M. si P.S.

Art. XVI: