| CATEGORII DOCUMENTE |

| Astronomie | Biofizica | Biologie | Botanica | Carti | Chimie | Copii |

| Educatie civica | Fabule ghicitori | Fizica | Gramatica | Joc | Literatura romana | Logica |

| Matematica | Poezii | Psihologie psihiatrie | Sociologie |

ELEMENTE DE ALGEBRA BOOLEANA

1.1. FUNCTII LOGICE

Modul de lucru al circuitelor digitale este studiat cu

ajutorul algebrei

Boole (introdusa de George Boole in jurul anului 1850

si aplicata de

Claude

Shannon in 1938

la functiile logice binare). Aceasta algebra opereaza cu

sistemul de numeratie binar, simbolurile folosite fiind 0 si 1

Variabilele logice pot lua una din cele

doua valori (0 sau 1), iar

operatorii

fundamentali sunt SI, SAU si NU.

in definirea operatorilor logici vom

nota cu X, Y, Z variabilele logice.

Operatorul logic SI (notat cu . semn

care uneori poate lipsi) se

scrie X.Y=Z si semnifica:

daca X=1 SI Y=1 atunci Z=1;

altfel Z=0

Operatorul logic SAU (notat cu +) se scrie

X+Y=Z si semnifica:

daca X=1 SAU Y=1 atunci Z=1;

altfel Z=0

Operatorul logic NU (notat cu o bara

deasupra variabilei careia

i se aplica) se scrie ![]() =Y. Daca X=1

atunci Y=0; altfel Y=1.

=Y. Daca X=1

atunci Y=0; altfel Y=1.

Acesti operatori logici se utilizeaza in

schemele logice, sub forma

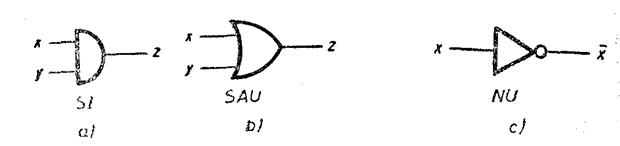

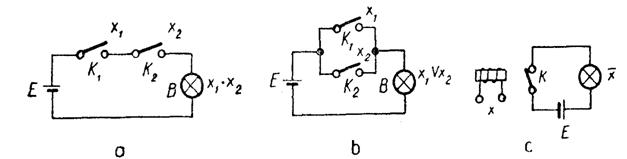

simbolurilor grafice date in figura 1.1.

Simbolurile din figura 1.1a si

1.1b

se mai numesc porti logice SI respectiv SAU iar

simbolul din figura

1.1c

se numeste inversor. De mentionat ca portile pot avea

si mai mult

de doua intrari.

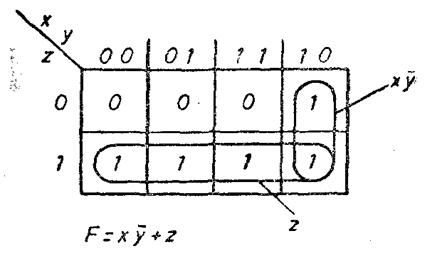

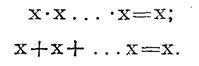

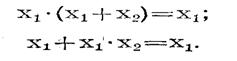

Pornind de la definitiile de mai sus s-au dedus teoremele algebrei

Boole date in tabelul 1.1.

Fig. 1.1. Principalele porti logice.

Cu ajutorul operatorilor SI, SAU si NU

se obtin functiile logice binare care au

domeniul de definitie si al valorilor multimea . Circuitele pentru care expresia functiei logice depinde numai de

variabilele de

intrare se numesc circuite combinationale

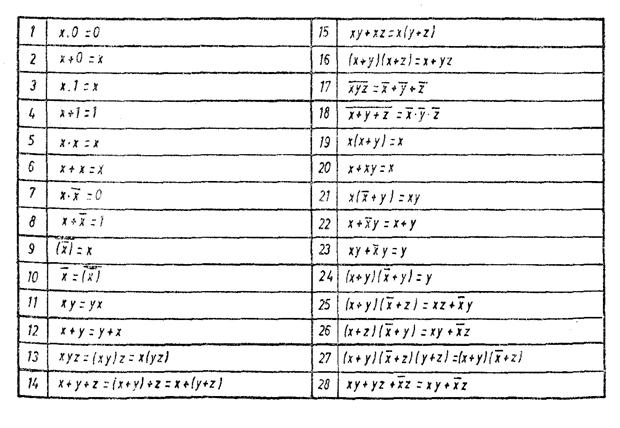

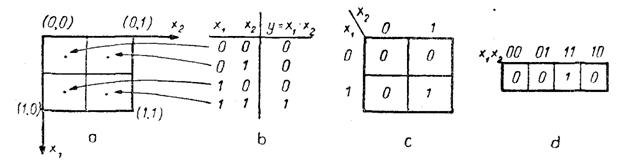

Pentru studiul acestui tip de functii logice se folosesc tabelele de adevar, care cuprind toate combinatiile posibile ale variabilelor componente. De exemplu, in figura 1.2 se da expresia unei functii logice, reprezentarea grafica si tabela de adevar.

Combinatiile de variabile in stare normala sau

negata care dau, in

tabela de adevar, valoarea 1 pentru functia logica se

numesc mintermeni.

Expresia functiei logice, sub forma

canonica disjunctiva, se obtine aplicand operatorul SAU acestor mintermeni. Pentru exemplul din figura 1.2

rezulta expresia functiei logice:

F=X![]() +

+![]() Z+X

Z+X![]() Z+

Z+![]() YZ+ZYZ

YZ+ZYZ

Teoremele algebrei Boole Tabelul 1.1

Trecerea de la aceasta expresie, la expresia mai

simpla din figura

2 se face prin simplificarea functiei.

In practica proiectarii circuitelor digitale

combinationale se porneste

de la tabela de adevar (dictata de

datele de proiectare), se deduce expresia

functiei logice, se simplifica aceasta expresie si se

organizeaza sub o

forma care permite implementarea cu

circuite integrate.

Fig. 1.2. Exemplu de reprezentare simbolica si cu tabela

de adevar pentru o functie

logica.

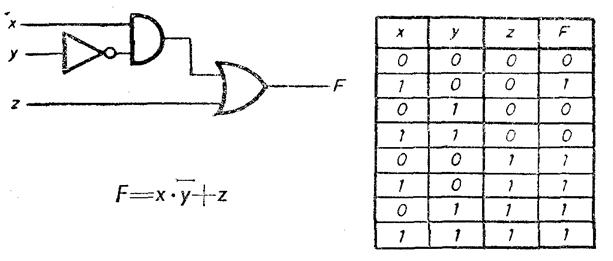

Simplificarea functiilor logice. Simplificarea functiilor logice se poate

face fie utilizand teoremele din tabelul 1,

fie utilizand diverse metode

grafice (diagramele Venn, Veitch, Karnaugh) sau metode special destinate (Quine-McClusky).

Pentru necesitati obisnuite (mai putin

de 5 variabile) cea mai adecvata metoda de simplificare este cea a

diagramelor Karnaugh, in care

se face uz de teorema 23 din tabelul 1.1:

XY+![]() Y=Y.

Y=Y.

Tocmai utilizarea acestei teoreme face necesara ordonarea casutelor in diagrame, astfel incat sa nu avem, la trecerea de la un rand la altul sau de la o coloana la alta decat o singura schimbare a uneia dintre variabile. Diagrama se obtine punand in fiecare casuta corespunzatoare 0 sau 1 in functie de continutul tabelei de adevar a functiei de minimizat.

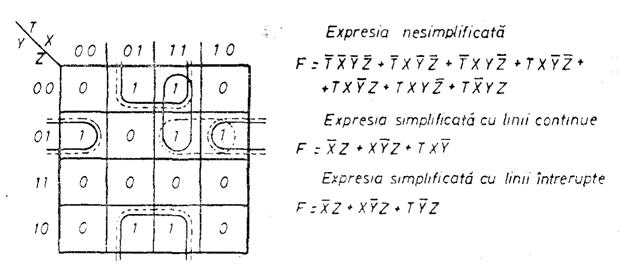

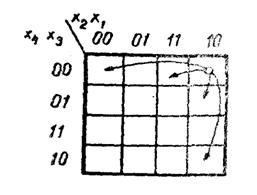

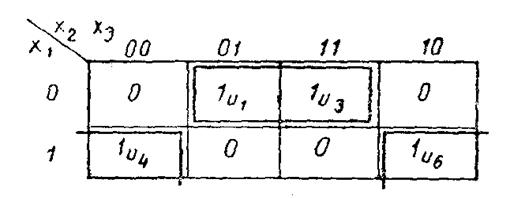

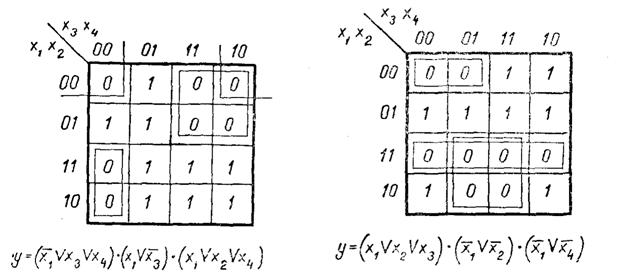

In figura 1.3 se da diagrama Karnaugh a functiei data de expresia (1).

Se observa incercuirea pozitiilor cu valoarea 1. Aceste incercuiri pot cuprinde un numar 2n (2, 4, 8 etc.),de casute adiacente ale diagramei, evidentiind eliminarea uneia sau mai multor variabile. Se constata ca o incercuire de doua casute elimina o variabila, de 4 casute doua variabile, avand ca regula: o incercuire de 2n casute elimina n variabile.

Fig. 1.3. Exemplu de diagrama Karnaugh pentru trei variabile.

Trebuie adaugat

ca in diagrama, casutele aflate la extremele randurilor sau

coloanelor se considera adiacente si pot

participa la o incercuire de eliminare,in figura 1.4 se da un exemplu de

minimizare a unei functii de patru variabile. De

remarcat ca simplificarea nu este unica, in practica alegand

expresia cea mai convenabila pentru

implementare.

In anume situatii practice nu intereseaza

valoarea functiei decat pentru o parte din

combinatiile variabilelor de intrare, unele combinatii neavand sens. in aceste cazuri valorile care se introduc in

diagrama sunt

indiferente (termeni redondanti), si

se noteaza cu X. Acesti termeni pot

fi considerati 1 si inclusi in incercuirile de eliminare, pentru a

mari suprafata incercuirii cat mai mult

si deci a elimina cat mai multe variabile.

In cazul lucrului ulterior cu diagrama Karnaugh se va putea urmari

aceasta facilitate.

Fig. 1.4. Exemplu de diagrama Karnaugh pentru patru variabile.

Pentru functii cu mai mult de cinci variabile

utilizarea diagramei

Karnaugh devine dificila si se

prefera metode de simplificare ce pot face

uz de calculator. O astfel de metoda este

metoda Quine-McClusky .

ELEMENTELE DE BAZA ALE CIRCUITELOR LOGICE

Realizarea practica a functiilor logice se

poate face in diverse tehnici: cu comutatoare

(relee), cu circuite pneumatice sau circuite electronice. Ultima posibilitate este cea de care ne vom ocupa avand in vedere

ca in radiocomunicatii constituie

singura modalitate uzitata.

PORTI LOGICE

Operatorii logici, ca si unele functii logice simple

capata dupa cum

am vazut (in figura 1.1) forme grafice

specifice si sunt tratate ca entitati

distincte in circuitele digitale. Aceste

entitati poarta numele de porti

logice

Pentru realizarea portilor logice se folosesc

circuite care lucreaza

atat la intrare cat si la iesire cu

doua nivele de tensiune. Alocarea acestor

nivele de tensiune starilor logice 0 sau 1, determina tipul de logica utilizata.

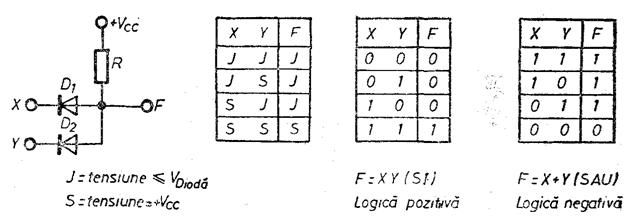

Astfel, daca nivelul superior (S) de tensiune se considera starea logica 1 se lucreaza in logica pozitiva, iar daca nivelul inferior (I) de tensiune se considera starea logica 1 se lucreaza in logica negativa. De exemplu, in fig. 1.5 se arata realizarea cu acelasi circuit a doua functii logice diferite in functie de tipul de logica adoptat.

Desi in general se lucreaza in logica

pozitiva producatorii de circuite

digitale specifica functionarea

acestora cu nivelele de tensiune (S si I) ramanand la latitudinea

utilizatorului sa aleaga tipul de logica folosit. In cele ce

urmeaza vom considera numai lucrul in logica pozitiva si se vor

utiliza numai simbolurile 0 si 1.

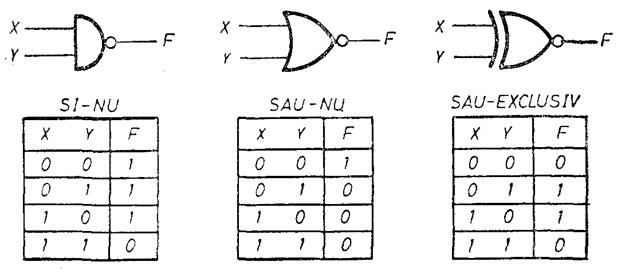

Pe langa portile logice din figura 1.1 mai se

utilizeaza si portile

logice ale caror simboluri grafice

si tabele de adevar se dau in figura 6.

Fig. 1.5. Poarta logica cu diode si tabelele de adevar in logica pozitiva

si negativa.

Fig. 1.6. Portile SI-NU, SAU-NU si SAU EXCLUSIV.

Reprezentare simbolica si tabele de adevar.

Cu ajutorul teoremelor 17 sau 18 din tabelul 1.1,

teoremele lui De Morgan, orice functie logica se poate implementa cu

ajutorul functiilor

SAU

- NU si SI - NU la care se adauga

inversoare (executa negarea).

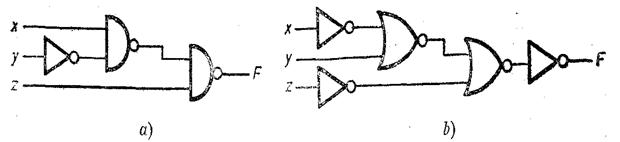

De exemplu functia logica din figura 1.2 se poate transforma astfel:

F=X![]() +Z=

+Z=![]() =

=![]()

![]()

F=X![]() +Z=

+Z=![]() +Z=

+Z=![]()

![]() +Z=

+Z=![]()

In figura 1.7a se

da implementarea functiei conforma cu (2) cu

porti logice SI-NU si

inversoare, iar in figura 1.7b cu

forma (3) cu porti logice SAU-NU si

inversoare.

Fig. 1.7. Exemplu de implementare a functiei logice F = ![]() +Z

+Z

cu porti SI-NU si cu porti SAU-NU.

Pe langa circuitele combinationale, realizate

cu porti logice, exista

circuitele logice secventiale, ale

caror stari, la un moment oarecare de

timp, depind atat de valoarea variabilelor de la intrare, cat si de starea

logica anterioara a circuitelor

(circuite cu memorie). Circuitele logice secventiale se realizeaza cu ajutorul circuitelor bistabile de

diverse tipuri.

DEFINIREA AXIOMATICA A ALGEBREI BOOLEENE

Axiomele algebrei booleene sunt urmatoarele:

Fie o

multime M compusa din elementele x1; x2,.. . xn

impreuna cu

operatiile . si +, ce vor fi definite ulterior.

Aceasta multime formeaza

o

algebra daca: .

Multimea M contine cel putin doua elemente distincte x1≠x2,

x1 ![]() M si x2

M si x2 ![]() M;

M;

Pentru orice x1 ![]() M si

x2

M si

x2 ![]() M

avem:

M

avem:

![]()

Operatiile . si

+ au urmatoarele proprietati:

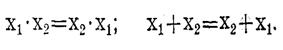

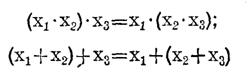

3.a) sunt comutative:

3.b) sunt asociative:

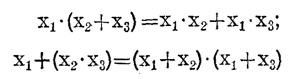

3.c) sunt distributive una fata de cealalta:

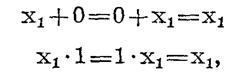

Ambele operatii admit cate un element neutru cu proprietatea:

unde 0 este elementul

nul al multimii iar 1 este elementul unitate al

multimii.

Daca multimea M nu contine decat

doua elemente, acestea trebuie

sa fie in mod obligatoriu elementul nul (0) si elementul unitate (1),

atunci pentru orice x![]() M va exista un

element unic notat cu

M va exista un

element unic notat cu ![]() cu proprietatile:

cu proprietatile:

![]()

proprietate cunoscuta si sub numele de principiul contradictiei;

![]()

proprietate

cunoscuta si sub numele de principiul tertului exclus.

Elementul ![]() este inversul

elementului x.

este inversul

elementului x.

In

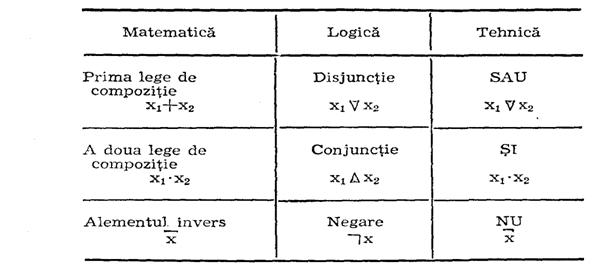

definitia axiomatica a algebrei s-au folosit doua legi de compozitie

notate cu simbolurile +, respectiv . , precum si notatia ![]() pentru

pentru

elementul invers. In logica, respectiv

tehnica, pentru aceste legi de compozitie se folosesc

denumiri si notatii specifice, asa cum rezulta din tabelul

2.1.

Tabelul

2.1

Denumirea operatiilor

2.1. Interpretarea operatiilor algebrei booleene

Semnificatia

legilor de compozitie poate fi ilustrata in mai multe

moduri:

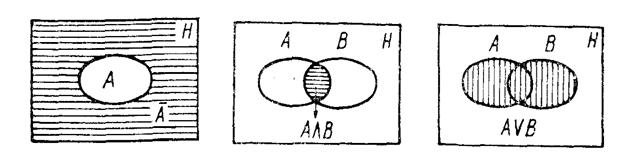

Prin diagrama Venn (fig. 2.1)

Fig. 2.1. Ilustrarea semnificatiei legilor de compozitie

prin diagrame Venn.

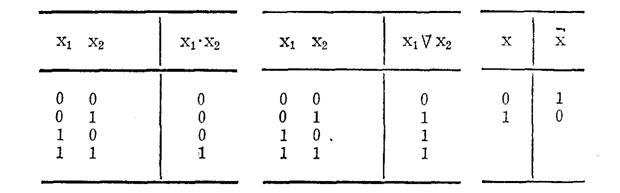

Cu ajutorul tabelelor de adevar.

Prin

tabelul de adevar se stabileste o corespondenta intre

valorile

de adevar ale variabilelor si valoarea de

adevar a functiei.

Tabelul

2.2

Tabelul

de adevar al operatiilor de baza

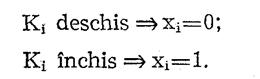

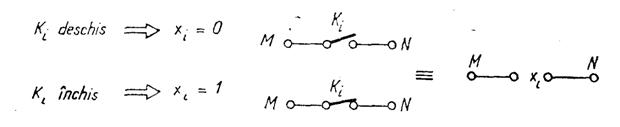

Pentru o

mai buna intelegere a sensului acestor operatii, ele vor fi

ilustrate si cu ajutorul unor scheme simple

realizate cu o baterie E, doua

intrerupatoare K1

K2 si un bec B. intrerupatorul Ki se

asociaza cu variabila xi astfel:

Becul B

va indica rezultatul operatiei astfel: daca rezultatul operatiei

este zero becul B ramine stins iar in caz contrar se aprinde. Cu aceste

precizari se poate urmari usor

functionarea circuitelor din fig. 2.2., ce

realizeaza operatiile SI, SAU, NU.

Fig 2.2. Ilustrarea semnificatiei legilor de compozitie

prin circuite simple:

a) circuit SI; b) circuit SAU; c) circuit NU.

In

cazul circuitului inversor din fig. 2.2. c intrerupatorul K este normal

inchis (becul B este aprins). La aplicarea semnalului de comanda x

intrerupatorul K se deschide si becul se stinge.

2.2. Reguli de calcul in algebra booleana

Plecand

de la axiome se deduc o serie de teoreme care vor forma

reguli de calcul in cadrul algebrei. Vom prezenta in

continuare principalele teoreme fara demonstratii:

Principiul dublei negatii:

![]()

Dubla negatie conduce la o afirmatie.

Legile de idempotenta

Legile de absorbtie

Legile elementelor neutre

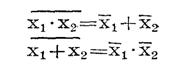

Formulele lui De Morgan

Cu

ajutorul acestor formule se poate transforma produsul logic in

suma logica si invers (prin trecerea

negatiei de la termeni la argumente

si

invers).

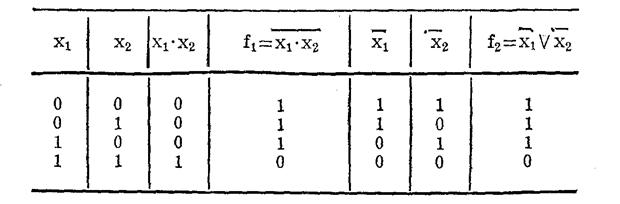

Verificarea

acestor teoreme se poate face foarte usor cu ajutorul

tabelelor de adevar si cu observatia

ca doua functii sunt egale daca iau

aceleasi

valori in toate punctele domeniului de definitie. Pentru exemplificare

sa verificam prima teorema a lui De Morgan. Notam: f1(x1,x2)=![]() si f2(x1,x2)=

si f2(x1,x2)=![]() . Vom scrie valorile de adevar ale celor doua

. Vom scrie valorile de adevar ale celor doua

functii in toate punctele

domeniului de definitie, asa cum este indicat

in tabelul 2.3.

Tabelul

2.3

Verificarea

egalitatii a doua functii

Din

tabelul 2.3 se observa ca functiile f1 si

f2 iau aceleasi

valori in

toate punctele domeniului de definitie deci sunt

egale.

2.3. FUNCTII BOOLEENE

2.3.1. Generalitati

O functie ![]() se numeste functie booleana.

se numeste functie booleana.

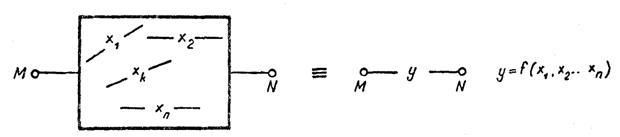

Cu alte cuvinte, o functie de n variabile y=f(x1 x2.. . xn) ce se va caracteriza prin faptul ca atat variabilele cat si functia nu pot lua decat doua valori distincte.

Functia va pune in corespondenta fiecarui element al produsului cartezian n dimensional valorile zero sau unu.

Asemenea

functii vor fi utile pentru caracterizarea functionarii unor

circuite construite cu elemente de circuit avand doua

stari, cum ar fi

de exemplu: un intrerupator inchis sau deschis, un

tranzistor blocat sau

in conductie etc. Functionarea unui astfel de element de circuit va

fi

descrisa

de o variabila booleana xi asa cum se indica in

fig. 1.3.

Fig. 2.3. Functionarea unui intrerupator simplu.

Daca consideram acum un ansamblu de intrerupatoare interconectate intre ele intr-un mod oarecare, unele inchise altele deschise, ele se reprezinta ca in Fig .1.4.

Fig. 2.4. Asocierea unei functii booleene cu o retea de intrerupatoare.

Existenta

sau inexistenta unei cai de curent intre bornele terminale

ale ansamblului va depinde de modul de interconectare al

acestora, precum si de starea fiecaruia in parte. Aceasta

dependenta se exprima din

punct de vedere matematic cu o functie booleana

de forma:

![]()

2.3.2. Reprezentarea functiilor booleene

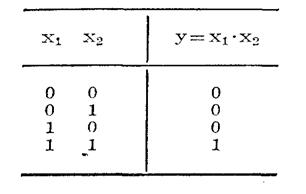

Pentru

reprezentarea functiilor booleene se folosesc in mod frecvent

doua modalitati:

a) tabela de adevar;

b) diagrama Karnaugh.

a) Reprezentarea cu tabela de adevar inseamna practic a marca intr-o tabela corespondenta intre valorile de adevar ale variabilelor de intrare si valoarea de adevar a functiei in fiecare punct al domeniului de definitie.

Tabelul 2.4

Tabelul de adevar al functiei SI

Exemplu: fie functia SI y=x1 ∙x2. Fiind o functie de doua variabile, domeniul de definitie este format din 22=4 puncte, corespunzator tuturor combinatiilor variabilelor de la intrare.

b)

Reprezentarea cu ajutorul diagramelor Karnaugh

consta in a marca punctele domeniului

de definitie intr-o diagrama plana si precizarea

valorilor functiei in fiecare din aceste puncte.

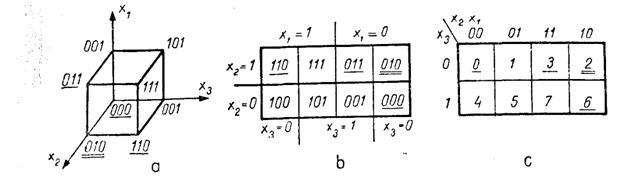

Exemplu. Pentru functia SI definita prin tabelul 2.4 domeniul de definitie il reprezinta varfurile unui patrat de latura unu, asa cum este indicat in fig. 2.5 a.

Diagrama Karnaugh, reprezentand functia SI este desenata in fig. 2.5 c. Diagrama Karnaugh din fig. 2.5 c se mai poate redesena si sub forma prezentata in fig. 2.5 d. In legatura cu aceasta din urma reprezentare, trebuie remarcat faptul ca succesiunea combinatiilor corespunzatoare variabilelor x1 si x2 trebuie scrisa in codul binar reflectat pentru a se pastra vecinatatile din diagrama originala.

Fig. 2.5. Reprezentarea unei functii de doua variabile:

a) domeniul de definitie; b) tabelul de adevar;

c) si d) diagrame Karnaugh.

In cazul unei functii de trei variabile y=f(x1, x2, x3), domeniul de definitie este format din 23=8 puncte si reprezinta varfurile unui cub cu latura unu (fig. 2.6 a). Pentru functii de trei variabile diagramele Karnaugh corespunzatoare pot fi prezentate fie sub forma din fig. 2.6 b, fie asa cum este indicat in fig. 2.6 c.

Fig. 2.6. Reprezentarea domeniului de definitie al unei functii de trei variabile: a) cub cu latura unu; b si c) diagrame Karnaugh.

In fig. 2.6

b coordonatele punctelor domeniului de definitie au fost inscrise

in binar, ceea ce ne va permite sa analizam mai usor

vecinatatile.

Daca

luam in considerare varful cubului caracterizat prin coordonatele 010

constatam, din reprezentarea din fig. 2.6 a, ca acest varf este vecin

cu urmatoarele varfuri: 000, 110 si 011. in

diagrama Karnaugh din fig. 2.6 b constatam ca varful

010 este vecin doar cu varfurile 011 si 000.

Pentru

ca diagrama din fig. 2.6 b sa fie echivalenta cu reprezentarea

din fig. 2.6 a, va trebui sa pastreze aceleasi

vecinatati, lucru ce devine

posibil doar daca ne imaginam ca latura din

stanga a diagramei Karnaugh

din fig. 2.6 b este identica cu cea din dreapta

si cea de sus cu cea

de jos.

In fig.

2.6 c combinatiile corespunzatoare variabilelor x2 x1 s-au scris

in cod binar reflectat, iar coordonatele varfurilor in

zecimal. Cu aceste

precizari cu privire la domeniul de definitie in

fig. 2.7 am dat un exemplu de functie de trei variabile

reprezentata in trei moduri diferite.

Fig. 2.7. Reprezentarea unei functii de trei variabile:

a) pe cubul cu latura unu; b) si c) prin diagrame Karnaugh.

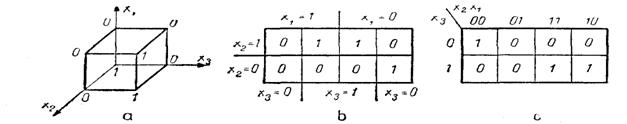

In fig.

2.8 este reprezentata diagrama Karnaugh pentru o functie

de patru variabile, unde prin sageti s-au

marcat vecinatatile punctului

de coordonate 0010.

Fig.

2.8. Diagrama Karnaugh corespunzatoare

unei functii de patru variabile.

2.3.3. Functii booleene elementare

Forma generala a unei functii booleene de n variabile este:

![]()

Domeniul de definitie al acestei functii este

format din m=2n puncte.

Cum in fiecare din aceste puncte functia poate lua numai valorile 0,1, rezulta ca numarul total al

functiilor booleene de n

variabile este N=![]() .

.

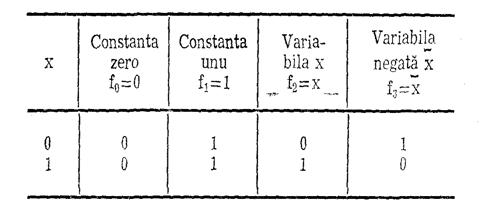

Se vor

considera in cele ce urmeaza functiile booleene elementare

de una si de doua variabile. Pentru n=1 functia

este de forma y=f(x) si numarul acestora este N=![]() =4, iar cele patru functii sunt trecute

=4, iar cele patru functii sunt trecute

in tabelul 2.5.

Tabelul

2.5

Functii

booleene de o variabila

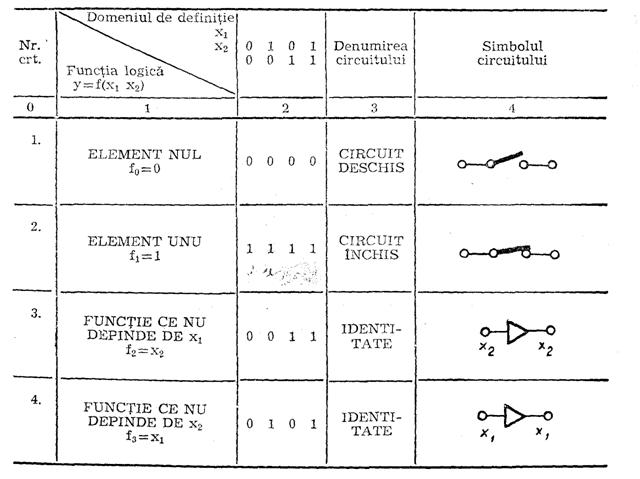

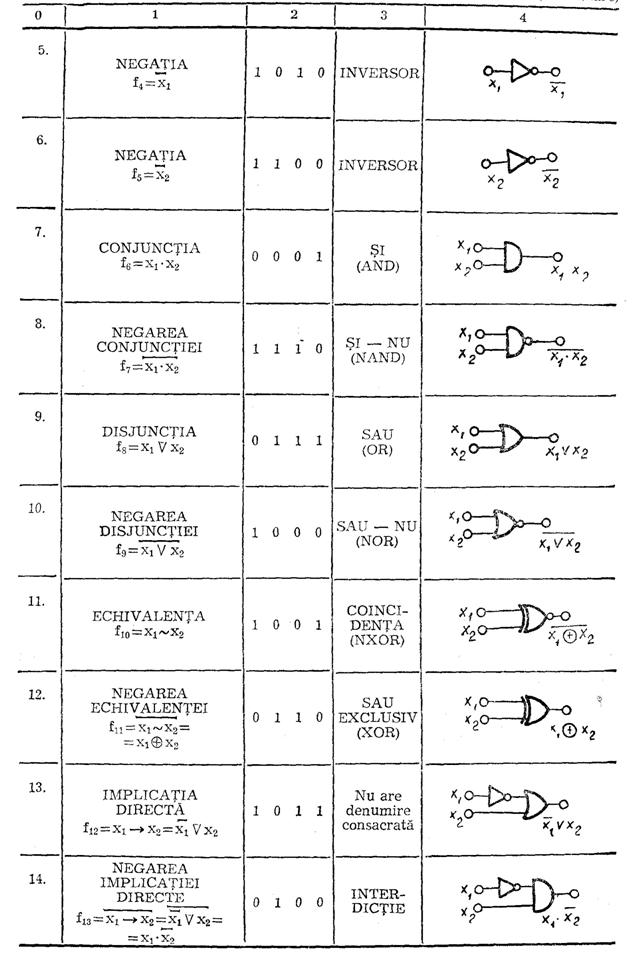

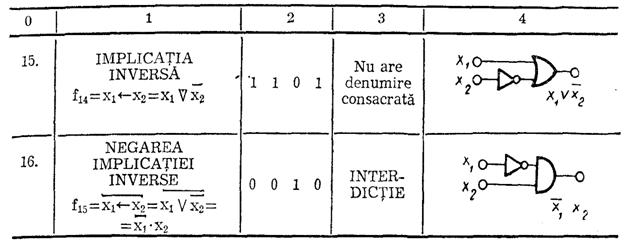

Pentru

n=2 rezulta N=![]() =16 functii de doua variabile, adica de

=16 functii de doua variabile, adica de

forma

y=f(x1, x2) reprezentate in tabelul 2.6.

Tabelul

2.6

Functii booleene de doua variabile

Din examinarea tabelului 2.6 observam ca:

f0 si f1 nu sunt functii, ci constante;

f2,f3,f4 si f5 nu sunt functii de doua variabile, ci doar de una singura;

functiile apar in perechi (functia si inversa ei).

Definitia

axiomatica a algebrei booleene prezentata apeleaza

la doua legi de compozitie notate cu . respectiv +. In cazul in care

multimea

M contine doar doua elemente, fiecarui element x i se

asociaza un

unic element ![]() numit inversul

elementului x. Acest lucru inseamna ca

numit inversul

elementului x. Acest lucru inseamna ca

in expresia oricarei functii booleene de n variabile vor aparea numai

aceste trei operatii elementare. Din punct de vedere practic acest

lucru

inseamna ca un sistem fizic al

carui functionare este descrisa de o functie

booleana se va putea realiza prin

interconectare unui numar de trei

tipuri de circuite elementare

si anume: circuitul SI (realizeaza operatia .),

circuitul SAU (realizeaza

operatia +) si circuitul INVERSOR (realizeaza

inversarea). Se demonstreaza /11/,

ca acelasi sistem fizic poate fi realizat practic utilizand un singur tip de circuit

elementar de exemplu circuitul

SI-NU (NAND) sau circuitul

SAU-NU (NOR).

Aceste

posibilitati de sinteza se bazeaza pe scrierea

functiilor booleene .

sub forma disjunctiva respectiv conjunctiva canonica .

Utilizarea

circuitelor NAND sau NOR la realizarea unui sistem sunt

echivalente din punct de vedere teoretic insa din

punct de vedere practic

alegerea este dictata de familia de circuite

integrate cu care se lucreaza. De exemplu in familia de

circuite integrate TTL Circuitul NAND se realizeaza usor motiv

pentru care se prefera sinteza cu astfel de circuite pe cand in familia de

circuite ECL circuitul NOR se realizeaza

mai usor si deci se va prefera sinteza cu acesta.

2.3.4. Forma canonica a functiilor booleene

In

numeroase aplicatii apare necesitatea reprezentarii analitice a func-

tiilor booleene. In acest scop se recurge la asa numitele formule

de dez-

voltare, in algebra booleana se folosesc

doua asemenea forme de dez-

voltare.

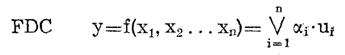

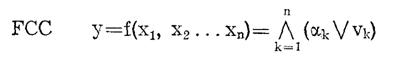

forma disjunctiva canonica (FDC), care presupune utilizarea unor

functii elementare numite

constituenti ai unitatii;

forma conjunctiva canonica (FCC), care presupune utilizarea unor

functii elementare numite

constituenti ai lui zero.

Pentru o tratare sistematica a problemei, se introduc urmatoarele notatii :

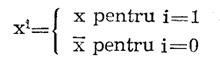

Definitia 1. Se numeste constituent al unitatii functia elementara uk, caracterizata prin aceea ca ia valoarea unu intr-un singur punct al domeniului de definitie. in cazul unei functii de n variabile, constituentul unitatii va fi produsul logic (conjunctia) tuturor variabilelor negate sau nenegate, dupa urmatoarea regula:

Pentru

ca acest produs sa fie unu intr-un anume punct al domeniului de

definitie, este necesar ca toti termenii produsului sa fie egali

cu unu. Pentru ca un termen de forma ![]() sa fie unu este

necesar ca ij=xj.

De aici rezulta urmatoarea regula de scriere

a functiei elementare uk:

sa fie unu este

necesar ca ij=xj.

De aici rezulta urmatoarea regula de scriere

a functiei elementare uk:

in conjunctia variabilelor, variabilele care iau in

respectivul punct al

domeniului

de definitie valoarea zero se vor lua negate iar celelalte nenegate.

Definitia

2. Se numeste constituent

al lui zero functia

elementara

v1 care ia valoarea zero intr-un singur punct

al domeniului de definitie,

in cazul unei functii de n variabile, expresia constituentului se va scrie

ca disjunctia tuturor variabilelor negate sau

nenegate.

Conditia

de constituent al lui zero impuNE ![]() =0 pentru orice j ceea ce implica iJ=

=0 pentru orice j ceea ce implica iJ=![]() . Rezulta ca in scrierea constituentului lui zero v1,

intr-un anume punct al domeniului de definitie, se vor lua negate

variabilele care iau valoarea unu in acel

punct si nenegate cele care iau valoarea zero.

. Rezulta ca in scrierea constituentului lui zero v1,

intr-un anume punct al domeniului de definitie, se vor lua negate

variabilele care iau valoarea unu in acel

punct si nenegate cele care iau valoarea zero.

Constituentii

unitatii uk se mai numesc si termeni minimali (minterm)

ai functiei, iar constituentii v1 ai lui zero se mai

numesc si termeni

maximali

(maxterm) ai functiei.

De

exemplu in tabelul 2.7 s-au indicat constituentii unitatii

si ai lui

zero in

fiecare punct al domeniului de definitie pentru o functie de trei

variabile.

Tabelul 2.7

Tabel cu constituentii lui zero si ai lui unu

pentru o functie de trei variabile

In coloana a doua a tabelului 2.7 am notat prin αi valorile nespecificate ale functiei booleene de trei variabile. In ultima coloana prin specificarea acestor valori am dat un exemplu de functie.

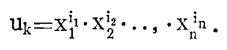

Formele

canonice ale unei functii booleene de trei variabile sunt

urmatoarele :

![]() (2.1)

(2.1)

![]() (2.2)

(2.2)

In

cazul general al unei functii de n variabile, forma disjunctiva

canonica reprezinta disjunctia tuturor

constituentilor unitatii pe care

ii are functia:

Forma conjunctiva canonica a unei functii de n variabile va reprezenta conjunctia tuturor constituentilor lui zero pe care ii are functia:

Daca

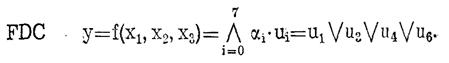

se revine la exemplul functiei de trei variabile prezentat in

ultima coloana a tabelului 2.7 vor rezulta

urmatoarele forme canonice:

sau

![]()

Se

observa ca din expresia generala data de relatia 2.1

dispar termenii pentru care ![]() =0 (deoarece 0∙ui=0 si 0 V uk=uk)

=0 (deoarece 0∙ui=0 si 0 V uk=uk)

sau

![]()

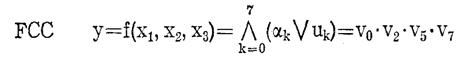

In cazul

FCC din expresia generala

data de relatia 2.2 dispar termenii pentru care ![]() =l (deoarece 1Vvk=l

si l∙v1=v1).

=l (deoarece 1Vvk=l

si l∙v1=v1).

2.3.5. Forma minima a functiilor booleene

Avand in

vedere faptul ca algebra booleana se va folosi la analiza

si sinteza circuitelor de comutatie, nu este

greu de anticipat ca intre

gradul de complexitate al circuitului si cel al

functiei pe care il descrie

exista o legatura directa. Acesta este

motivul pentru care in etapa de

sinteza a circuitelor de comutatie, dupa definirea acestora,

urmeaza in

mod obligatoriu etapa de minimizare a

functiei, avand drept scop obtinerea unei forme echivalente mai simple (forma minima). Realizarea practica a circuitului urmeaza a se face

pe baza acestei forme simple

Avand in vedere importanta practica a

minimizarii, in literatura de specialitate se gasesc

descrise numeroase metode /11/, /13/. Dintre acestea

se vor prezenta pe scurt numai doua, si anume:

metoda analitica; ,

metoda diagramelor Karnaugh.

Metoda analitica

Aceasta

metoda de obtinere a formei minime se bazeaza pe folosirea

teoremelor algebrei booleene. Principiul metodei se va

ilustra pe exemplul anterior al functiei de trei variabile. Se va pleca de

la forma disjunctiva canonica (2.5) a functiei:

![]()

Avand in vedere proprietatea de distributivitate care se aplica termenilor u1 si u3 respectiv u4 si u6 rezulta:

![]()

Tinand

seama si de proprietatea tertului exclus (xVx=l) si de

faptul ca 1 este elementul unitate (x∙l=x),

rezulta forma disjunctiva

minima a functiei:

FDM ![]()

Procedand similar se poate gasi si forma conjunctiva minima a functiei.

Metoda diagramelor Karnaugh

Aceasta

metoda nu reprezinta altceva decat transpunerea operatiilor

facute la metoda analitica pe reprezentarea

functiei prin diagrame

Karnaugh, rezultand astfel in final o metoda

expeditiva de minimizare.

O

diagrama Karnaugh poate fi privita, daca se ia in

consideratie

produsul logic al coordonatelor, ca o reprezentare a

functiei booleene

prin termeni minimali (constituenti ai

unitatii). Vom ilustra aceasta in

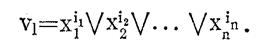

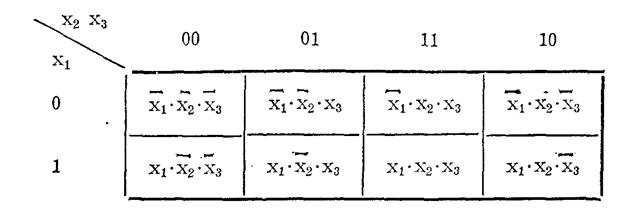

cazul unei functii de trei variabile cu tabelul 2.8.

Tabelul

2.8

Termenii

minimali pentru o functie de trei variabile

Fiecare

celula din diagrama Karnaugh reprezentata in tabelul 2.8

contine un termen minimal. Doua celule vecine

contin termeni minimali, care difera prin valoarea

unei singure variabile. Daca termenilor minimali

din doua celule vecine li se aplica proprietatea de distributivitate

si cea a tertului exclus, se elimina

variabila care isi schimba valoarea.

Pe diagrama Karnaugh acest lucru revine la a scrie

coordonatele comune

ale ansamblului celor doua celule vecine. Acest

proces poate fi urmarit

pe exemplul prezentat in 2.3.5.1, ilustrat in tabelul

2.9.

Tabelul

2.9

Exemple de minimizare

De

exemplu: gruparea celulelor vecine care contin

constituentii u1 si

u3 ne conduce la expresia ![]() x3, iar gruparea celulelor vecine care contin

x3, iar gruparea celulelor vecine care contin

constituentii u4 si u6 conduce la expresia x1∙![]() . Forma disjunctiva minima

. Forma disjunctiva minima

a functiei rezulta prin scrierea

disjunctiei grupurilor de coordonate

comune ale gruparilor formate astfel:

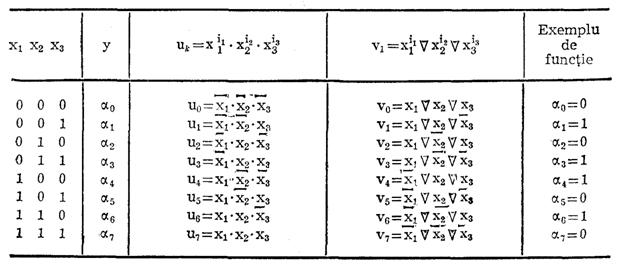

Metoda poate fi generalizata astfel:

1.

Daca grupul initial de doua celule vecine este vecin la randul

sau

cu un alt grup de doua celule vecine, acestea se pot contopi intr-un singur

grup de 4 celule vecine, ceea ce va permite eliminarea a doua variabile.

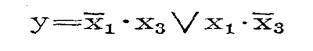

Fig. 2.9. Exemple de minimizari pentru functie de

trei si

patru variabile (forma disjunctiva

minima).

Un grup de 2m celule vecine ocupate de unitati permite eliminarea a m variabile.

Fiecare

celula ocupata de unitati trebuie sa faca parte

cel putin

dintr-o grupare, dar poate fi

inclusa in mai multe.

Cel

mai avansat grad de simplificare se obtine daca unitatile

dintr-o diagrama Karnaugh sunt

grupate intr-un numar minim de grupuri

fiecare grup la randul sau continand un numar maxim de

unitati.

Observatie.

Pentru a putea aplica in mod succesiv proprietatea de

distributivitate si teorema tertului exclus

numarul unitatilor din gruparile formate

trebuie sa fie o putere intreaga a lui 2.

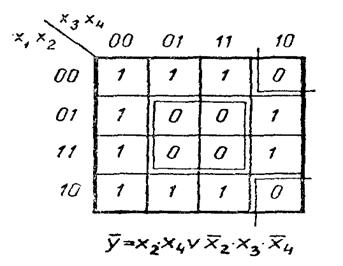

In fig.

2.9 sunt date cateva exemple de minimizari ale unor functii

booleene de trei si patru variabile.

Reguli

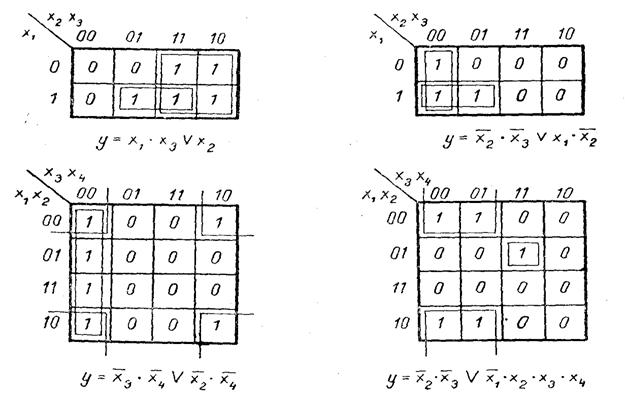

similare pot fi deduse si pentru obtinerea formei conjunctive

minime. in

acest caz, in diagrama Karnaugh se vor grupa zerourile.

Se va

scrie disjunctia coordonatelor grupului de zerouri vecine, iar

forma minima va fi conjunctia acestor grupuri

de coordonate.

La

scrierea coordonatelor grupurile de zerouri se va avea in vedere

faptul ca acestea reprezinta termeni maximali.

In fig.

2.10 se dau doua exemple de minimizare pentru obtinerea

formei conjunctive minime.

Fig. 2.10.

Exemple de minimizari pentru

functii de patru

variabile (forma conjunctiva minima).

Fig. 2.11. Exemplu de minimizare pentru obtinerea

formei disjunctive minime a functiei negate.

In

matricea Karnaugh se pot grupa zerourile ca si cand ar fi

unitati,

obtinandu-se FDM

a functiei negate ![]() (valabil si

invers). Un astfel de

(valabil si

invers). Un astfel de

exemplu este dat in fig. 2.11.

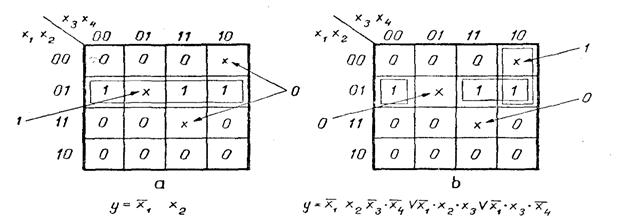

2.3.5.3. Minimizarea functiilor incomplet definite

Se spune

despre o functie ca este incomplet definita daca in anumite

puncte ale domeniului poate lua valoarea unu sau zero.

Aceste puncte

in diagrama Karnaugh vor fi notate cu simbolul x. Atunci cand

vom

minimiza functia vom lua in considerare valoarea unu

sau zero a functiei

booleene din aceste puncte astfel ca aceasta alegere

sa ne conduca la o

forma minima mai simpla.

Fig. 2.12. Exemple de minimizari pe functii incomplet definite:

a) atribuire optima a valorilor functiei; 6) atribuire neoptimala

a valorilor functiei.

De

exemplu, atribuirea facuta in fig.2.12 a ne conduce la forma

minima cea mai simpla a functiei, pe cand cea facuta

in fig. 2.12 b ne va conduce la o expresie mai

complicata a formei minime

corespunzatoare functiei booleene respective.

/21/, /11/.

3.CIRCUITE LOGICE ECL

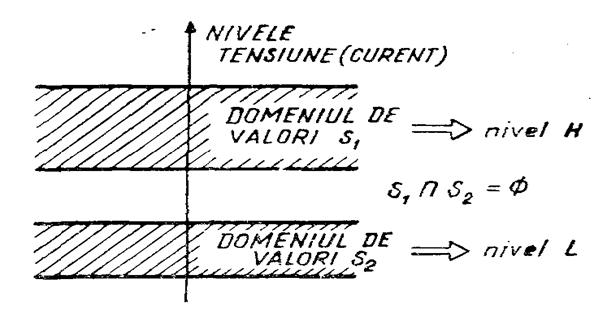

3.1. REPREZENTAREA FIZICA A VARIABILELOR BOOLEENE

Pentru

realizarea cu circuite electronice a functiilor booleene este

necesara

atribuirea valorilor unei marimi fizice electrice (tensiune sau

curent) multimii de doua elemente

*, care reprezinta valorile variabilelor

booleene. Cele doua valori 0 si 1 sunt puse in

corespondenta cu

doua domenii disjuncte ale marimii fizice alese

(v. fig. 3.1).

Fig. 3.1. Reprezentarea variabilelor booleene prin tensiuni.

Stabilirea

unor valori precise pentru cele doua nivele logice nu este

convenabila intrucat circuitul care trebuie sa

realizeze acest lucru devine

mai complicat. Este absolut necesara

conditia disjunctiei celor doua

domenii de valori (S1∩S2=)

intrucat elementele comune ar crea confuzii de interpretare in

domeniul valorilor functiilor booleene.

Reprezentarea

valorilor functiilor booleene prin nivele de tensiune

este mai raspandita si in cele ce

urmeaza ne vom referi la aceasta reprezentare.

Nivelele

de tensiune din cele doua domenii de valori Sx si S2

respecta relatia:

pentru

orice v1![]() S1 si v2

S1 si v2 ![]() S2, avem v1>v2.

S2, avem v1>v2.

Datorita acestui fapt tensiunile din intervalul S1 se mai numesc nivele H (High) iar cele din intervalul S2 se numesc nivele L (Low). Deoarece intre multimea valorilor functiilor booleene si multimea domeniilor de tensiune se pot stabili corespondentele din fig. 3.2 si 3.3 este necesara stabilirea unei conventii de asociere pentru a defini functia logica realizata de un anumit circuit.

Situatia

in care valorile maxime de tensiune corespund la 1 logic iar

cele minime la 0 logic defineste ceea ce se

numeste logica pozitiva (fig.3.2 a), iar

situatia in care valorile maxime de tensiune corespund la 0 logic iar cele minime la 1 logic defineste logica

negativa (fig. 3.2 b).

Fig. 3.2. Nivele logice si tensiuni:

a) logica pozitiva); b) logica negativa.

In

practica se intalnesc ambele tipuri de corespondente. Trebuie

observat ca schimbarea conventiei este echivalenta

cu o negatie a variabilei booleene.

Stabilirea

nivelelor de tensiune corespunzatoare domeniilor S1 si

S2

depinde de modul de realizare al circuitului, de felul transistoarelor

folosite, de tehnologia utilizata in cazul circuitelor

integrate, de tensiunile

de alimentare intrebuintate.

Evolutia

circuitelor logice a dus in timp la dezvoltarea unor familii

de circuite in care se incearca realizarea unui

compromis optim intre

diversele performante si cost.

3.2. PARAMETRII CIRCUITELOR LOGICE

Parametrii

circuitelor logice se pot impartii in doua categorii: carac-

teristici electrice statice si caracteristici

electrice dinamice.

Caracteristicile electrice statice descriu comportarea circuitelor logice in curent continuu sau la variatii lente in timp ale tensiunilor si curentilor prin circuit.

Caracteristicile electrice dinamice descriu comportarea circuitelor logice la tranzitii rapide ale semnalelor.

Vom

prezenta in continuare principalii parametrii statici si dinamici

ai circuitelor logice fara a particulariza

pentru circuitele logice ECL.

Particularizarea pentru circuitele ECL este data in paragraful 3.7.

Caracteristici electrice statice

Nivelele logice de intrare reprezinta

intervalele de tensiune pen-

tru care se atribuie nivel logic 0 si nivel logic 1

la intrarea unui circuit.

Nivelele logice de iesire

reprezinta intervalele de tensiuni pentru

care se atribuie nivel logic 0 si nivel logic 1 la

iesirea unui circuit.

Nivelele

logice de intrare si iesire sunt in general diferite dar pen-

tru a exista intotdeauna posibilitatea de cuplare a unei iesiri de

circuit

cu o intrare trebuie ca

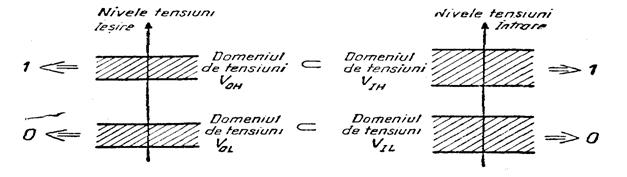

urmatoarele relatii de incluziune sa fie adevarate:

domeniul de tensiuni de intrare VIH![]() domeniul de tensiuni de iesire VOH

domeniul de tensiuni de iesire VOH

domeniul de tensiuni de intrare VIL![]() domeniul de tensiuni de iesire VOL.

domeniul de tensiuni de iesire VOL.

Aceste relatii sunt reprezentate si in fig. 3.3.

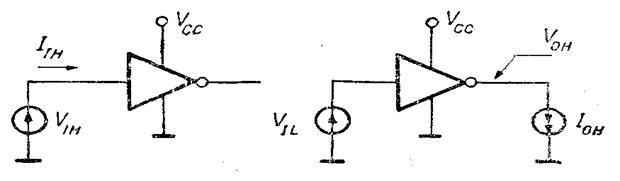

. Curentii de intrare reprezinta

curentii care se pot inchide prin intrarea circuitului logic

(intra sau ies din circuit) pentru nivelele logice

de intrare VIL si V1H. Curentii corespunzatori nivelelor V1L si

V1H, notati I1L si I1H sunt

in general diferiti, putand avea si sensuri diferite,

depinzand de structura circuitului logic.

Fig.

3.3. Nivele de tensiuni pentru intrare si iesire asociate

variabilelor booleene.

. Curentii de iesire reprezinta curentii care se pot inchide

prin

iesirea circuitului logic

(intra sau ies din circuit) pentru nivelele logice

de iesire VOL si VOH.

Un

exemplu este dat in fig. 3.4, unde s-a reprezentat curentul de

intrare IIH si curentul de iesire IOH

Fig. 3.4. Curentii de intrare si iesire.

. Capacitatea de intrare

este un parametru care caracterizeaza in-

trarile in circuite logice cu transistoare MOS

si reprezinta capacitatea

masurata intre intrarea circuitului si

borna comuna (masa).

Caracteristici electrice dinamice

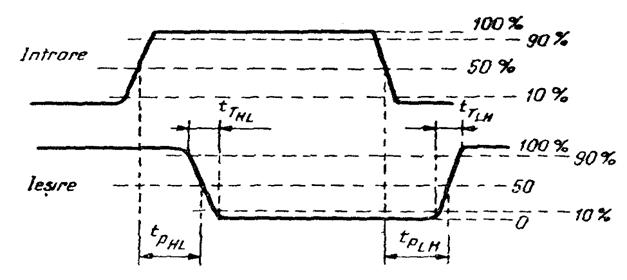

Timpul de propagare reprezinta

intervalul de timp scurs intre

aplicarea semnalului la intrare si obtinerea raspunsului la

iesirea circui-

tului logic. Timpul de propagare pentru tranzitiile

de la nivel L la nivel

H difera in general de cel pentru tranzitiile

de la nivel H la nivel L.

in fig. 3.5 sunt reprezentati timpii tpHL si

tpLH pentru un inversor logic.

Timpul de tranzitie al

semnalului de la iesire pentru tranzitii de

la nivel logic L la nivel H si invers. In fig. 3.5 sunt

reprezentati timpii

de tranzitie pentru tranzitii H-L (tTLH) si pentru tranzitii L-H (tTLH).

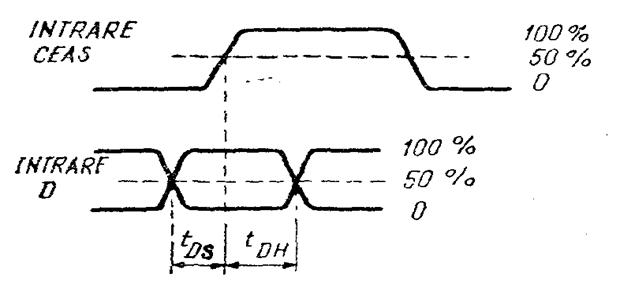

Timpul de pregatire (setup

time) reprezinta intervalul de timp

cu care trebuie sa preceada semnalul de pe o

intrare a unui circuit logic, semnalul prezent pe o alta intrare, considerata ca referinta de timp,

astfel ca functionarea circuitului sa fie

corecta.

Timpul de

mentinere (hold time) reprezinta intervalul de timp

cat trebuie mentinut neschimbat

semnalul pe o intrare a unui circuit logic

in comparatie cu o alta intrare considerata ca

referinta de timp, astfel incat

functionarea circuitului sa fie corecta.

Fig. 3.5. Timpii de propagare si tranzitie.

In fig.

3.6 este dat un exemplu pentru un circuit basculant bistabil

de tip D declansat pe front, timpii de

pregatire tos si mentinere tDH referindu-se

la intrarea de date a bistabilului in comparatie cu intrarea

de ceas.

Fig. 3.6. Timpii de pregatire si mentinere.

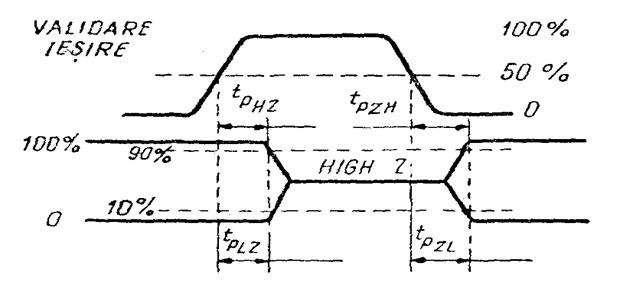

Timpii de

comutare din regim de mare

impedanta in regim activ

la iesire si din regim

activ in regim de mare impedanta, pentru circuitele

logice cu iesiri trei stari (vezi 3.6.2).

In fig.

3.7 sunt reprezentati timpii de comutare din regim de mare

impedanta in nivele logice L(tpZL) si

H(tpZH) la iesire si timpii de comutare

din nivele logice L(tpLZ) si H(tpHZ) in regim de

mare impedanta la iesire.

Fig. 3.7. Timpii de comutare in sta rea de mare impedanta.

In general acesti timpi difera intre ei.

Toti

acesti parametrii se determina in anumite conditii de

masura,

specificate in cataloage odata cu valorile lor.

Cunoasterea acestor

marimi este necesara, intru-cat pe baza lor se

poate stabili daca un circuit satisface conditiile

impuse de o anumita aplicatie.

3.3. FAMILIA DE CIRCUITE LOGICE ECL STANDARD

Pentru

intelegerea modului de functionare a circuitelor logice este

necesara o buna cunoastere atat a regimurilor de

functionare ale dispozitivelor semiconductoare (diode, transistoare

bipolare, si transistoare MOS)

cat si a polarizarilor necesare a fi aplicate

acestora pentru a obtine

functiunile dorite.

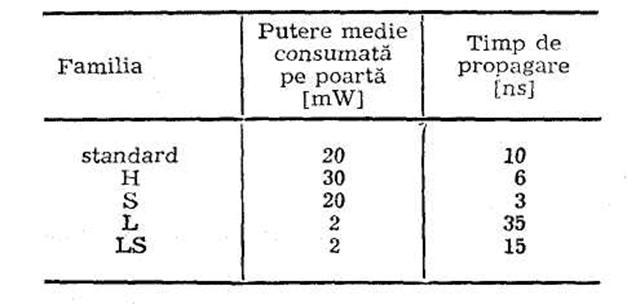

Familia

de circuite logice ECL standard impreuna cu variantele

H (High speed)), S (Shottky), L (Low Power - mica

putere) si LS (Low

Power Shottky) reprezinta o categorie foarte raspandita de

circuite logice

integrate pe scara mica si medie.

Performantele acestor circuite realizeaza un compromis

intre viteza de lucru si puterea consumata dupa

cum se vede in tabelul 3.1.

Tabelul

3.1

Comparatie

intre circuitele ECL

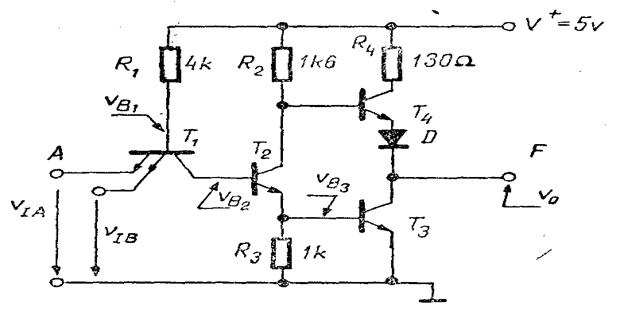

3.3.1. Poarta elementara Sl-NU

Schema unei porti logice SI-NU este data in fig. 3.8.

Fig. 3.3. Schema unei porti ECL Sl-NU.

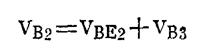

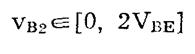

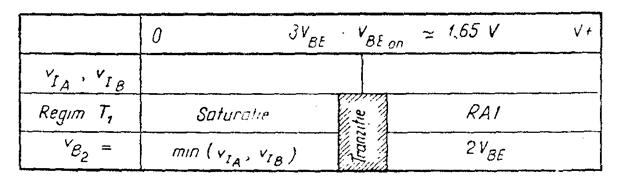

Pentru a explica functionarea circuitului sa analizam pentru inceput gamele de variatie ale tensiunilor vBl, vB2 si vB3 (notatia folosita inseamna tensiunea intre punctul respectiv si referinta).

Datorita

alimentarii cu tensiune pozitiva (V+>0), toate

tensiunile

din circuit sunt pozitive fata de masa.

Tensiunea vBS fiind de fapt tensiunea pe

jonctiunea BE a tranzistorului T3 va putea avea valori cuprinse

intre 0 si tensiunea de conductie a unei diode, respectiv vB3![]() [0, VBE]

[0, VBE]

unde VBE

![]() 0,6 V0,7 V. Pentru tensiunea vB2 putem

scrie:

0,6 V0,7 V. Pentru tensiunea vB2 putem

scrie:

Ca urmare gama de variatie pentru vB2 va fi:

Baza

tranzistorului T1 este legata prin rezistenta R1

la V+ cel mai

pozitiv potential din circuit. Tranzistorul fiind de

tipul npn rezulta posibilitatea ca jonctiunile BE si BC sa fie polarizate direct. Din circuit putem

scrie:

![]()

Considerand jonctiunea BC polarizata direct rezulta valoarea maxima a tensiunii Vb1

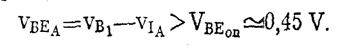

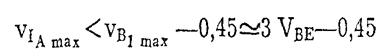

Starea jonctiunilor BE ale tranzistorului T1 depinde de tensiunile aplicate pe intrarile circuitului. Vom presupune ca v1A si v1B au valori cuprinse in domeniul [0, V+]. Pentru polarizarea directa a unei jonctiuni BE (de ex. jonctiunea BEA) trebuie ca:

Rezulta deci:

![]()

respectiv

Deci

pentru tensiuni![]() jonctiunea

BEA este blocata iar pentru vlA<l,65V

jonctiunea BEA intra in conductie. Similar

jonctiunea

BEA este blocata iar pentru vlA<l,65V

jonctiunea BEA intra in conductie. Similar

putem scrie si pentru jonctiunea BEB.

Daca ambele jonctiuni BEA si BEB

sunt blocate atunci tensiunea vBl va avea

valoarea maxima jonctiunile

BC1 BE2,

si BE3 formand un lant de diode polarizate direct prin

rezistenta

R1 de la sursa de alimentare V+.

Tranzistorul T1 lucreaza in acest caz

in regiunea activa inversa (RAI).

Daca

una din jonctiunile BEA sau BEB este deschisa

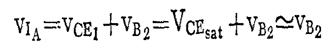

atunci tranzistorul este saturat avand vCE1 ![]() Vcesat

Vcesat ![]() si

potentialul bazei tranzistorului

si

potentialul bazei tranzistorului

T2 urmareste variatiile

tensiunii de intrare. De exemplu, daca jonctiunea

BEA este deschisa:

In

rezumat putem corela valorile tensiunilor de intrare cu regimul

de functionare al tranzistorului Tt

si tensiunea vBl ca in

tabelul 3.2.

Tabelul

3.2

Regimul

de conductie al tranzistorului T1

Pentru

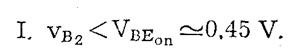

a analiza in continuare functionarea, sa consideram partea

de

circuit formata de transistoarele T2, T3 si T4.

In functie de valorile

tensiunii Vb2

se pot distinge urmatoarele situatii:

Fig. 3.9. Circuite echivalente pentru analiza portii ECL.

In

acest caz T2 este blocat, curentii de colector si emitor sunt

zero.

Ca urmare T3 este blocat, neavand polarizare

in baza.

Din schema simplificata corespunzatoare, din fig. 3.9..a rezulta:

![]()

unde

![]()

este tensiunea pe o dioda in conductie si

Daca se neglijeaza termenul

rezulta:

![]()

Tensiunea

de iesire este deci practic constanta pentru orice

valoare

vB2 din intervalul

considerat.

![]()

In

aceasta situatie T, este deschis, functionand in regiunea

activa

normala

(RAN), in timp ce T3 ramine in continuare blocat. T4

va fi in

conductie (RAN). Schema

simplificata corespunzatoare acestei situatii

este data in fig. 3.9. b. Se pot scrie relatiile:

Expresia tensiunii de iesire este:

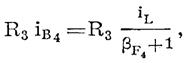

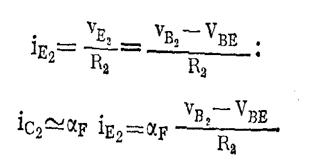

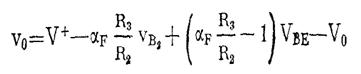

![]()

relatie in care s-a neglijat ca si in cazul precedent termenul R3 iB4.

Rezulta deci dependenta:

Tensiunea de iesire scade liniar odata cu cresterea tensiunii vB2.

In

aceasta situatie jonctiunea BE a tranzistorului T3 se

deschide si

cele doua tensiuni VBe2 si Vbe3 se limiteaza la valoarea de

0,6 V. Tensiunea vB2 practic nu mai poate creste

peste aceasta valoare. Rezistenta R2,

din emitorul lui T2, nu mai are efectul de limitare a curentului lui

T2, conductia curentului fiind preluata de jonctiunea

BE2. Curentii de colector ai lui T2 si T3

variaza exponential cu tensiunile baza - emitor respective ceea ce face ca pentru un interval

foarte mic de variatie a lui vB2

(zeci de mV), curentii de colector ai lui T2 si T3

sa creasca brusc aducand in

saturatie cele doua transistoare. Tensiunea de iesire va

fi in acest caz tensiunea de saturatie a lui T3

Observatie:

In situatia

in care T3 conduce la saturatie este necesar ca

tranzistorul T4 sa fie blocat. In

caz contrar un curent de valoare mare

se poate inchide de la sursa de alimentare prin calea de

curent formata

de T3 si T4. Blocarea lui T4

este realizata de partea de circuit reprezentata

in fig. 3.9. c. Pentru ochiul de circuit format

se poate scrie relatia:

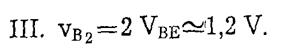

![]()

(jonctiunea BC3 polarizata direct - T3 saturat;

![]() (dioda deschisa);

(dioda deschisa);

Dar avem:

![]()

Rezulta

deci ca vBE4 ![]() VCEsat, tensiune insuficienta pentru a

deschide

VCEsat, tensiune insuficienta pentru a

deschide

tranzistorul T4. Din aceasta relatie

se observa si motivul pentru care a

fost introdusa dioda - blocarea lui T4.

In timpul procesului de comutare, cand tranzistorul T2 nu este saturat si VCE2>VCEsat este posibila conductia simultana a transistoarelor T3 si T4. Tranzitiile fiind rapide, pulsuri de curent de scurta durata (zeci ns) se vor inchide de la sursa de alimentare prin calea de curent formata de T3 si T4.

Din

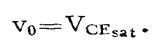

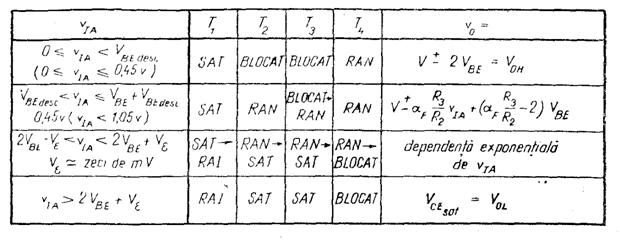

cele expuse se poate deduce caracteristica de transfer a unei

porti ECL reprezentata de

dependenta vo(vIA) | Vib =

Vjh sau v0(vIB) |vIA=viH

Aceasta

dependenta, cat si regimurile de lucru ale transistoarelor sunt

date in tabelul 3.3. in fig, 3.10 este

reprezentata caracteristica de transfer. Zonele hasurate (ale caror limite sunt precizate in axele

de coordonate) reprezinta

portiuni interzise pentru caracteristica de transfer a unui circuit cu o functionare corecta.

Functia logica

realizata de circuit este F=![]() .

.

Tabelul 3.3

Fig. 3.10. Caracteristica de transfer a portii ECL..

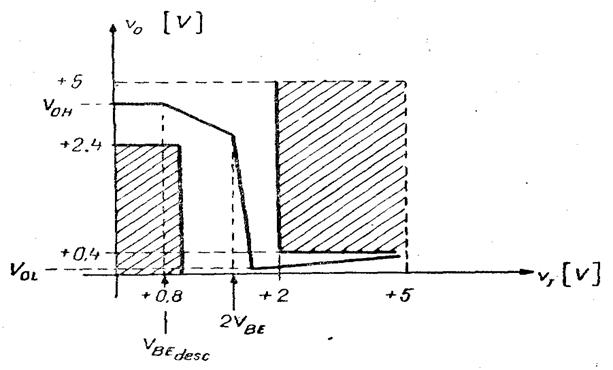

3.3.2. Poarta SAU-NU

Schema portii este

data in fig. 3.11. Functionarea circuitului este

asemanatoare cu aceea a portii

SI-NU.

Fig. 3.11. Schema unei porti ECL SAU-NU.

Grupurile

de transistoare T1T2 si ![]()

![]() constituie doua

etaje de intrare conectate in paralel pe rezistentele

R2 si R3. Daca unul din transistoarele T2

sau

constituie doua

etaje de intrare conectate in paralel pe rezistentele

R2 si R3. Daca unul din transistoarele T2

sau ![]() este saturat

atunci nivelul logic de iesire va fi 0. Rezulta ca

pentru a avea nivel logic 1 la iesire trebuie ca ambele transistoare

T2 si T'2 sa fie blocate, ceea ce inseamna

ca via=ViB=ViL.

este saturat

atunci nivelul logic de iesire va fi 0. Rezulta ca

pentru a avea nivel logic 1 la iesire trebuie ca ambele transistoare

T2 si T'2 sa fie blocate, ceea ce inseamna

ca via=ViB=ViL.

Functia

logica realizata va fi deci: F=![]() .

.

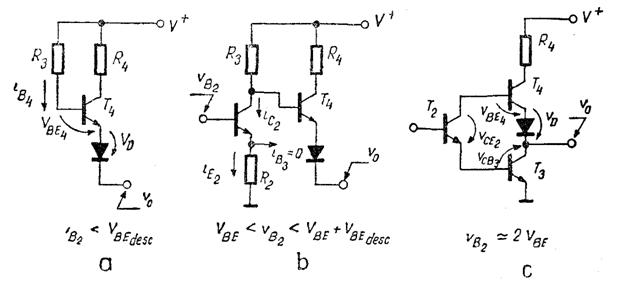

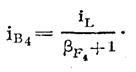

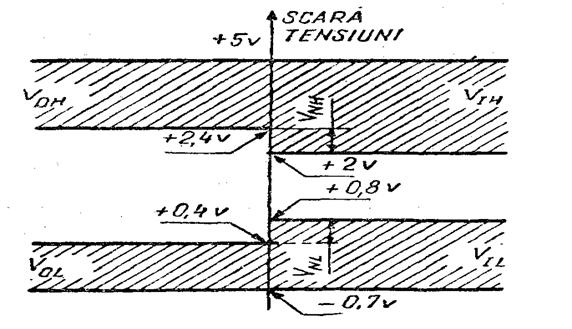

3.4. PARAMETRII CIRCUITELOR LOGICE ECL STANDARD

Printre

principalii parametri ai portilor ECL se pot cita: nivelele

logice ECL,

curentii de intrare si iesire, posibilitati de

intercuplare intre

diferite porti, timpii de propagare a

semnalelor logice .

Fig. 3.16. Nivele logice ECL.

. Nivele logice

Nivelele

logice corespunzatoare circuitelor ECL sunt precizate in

fig. 3.16. Limitele domeniilor de tensiune

corespunzatoare iesirilor din

circuit

(VOH si VOL) si intrarilor

din circuit (VIH si Vil)

sunt astfel alese incat sa fie

posibila intotdeauna cuplarea a doua circuite cu o rezerva de

tensiune numita margine de

zgomot.

Marginile de zgomot la nivel H si L sunt egale in acest caz si VNH=Vnl=0,4 V. Aceasta inseamna ca la un nivel logic de iesire L care are valoarea maxima de +0,4 V, chiar daca se suprapune un impuls parazit de inca + 0,4 V, intrarea va fi considerata tot nivel logic L de circuitul urmator pentru care VILmax=0,8 V.

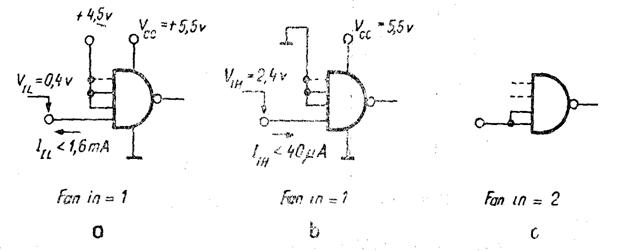

Curenti de intrare

Curentul

de intrare in poarta depinde de nivelul logic aplicat la in-

trare, in fig. 3.17 a, b sunt prezentati curentii de intrare

cu sensurile si

valorile lor pentru o intrare definita ca fiind unitate (standard). Se de-

fineste ca fiind "fan in'-ul unei intrari numarul N(N^1)

de intrari

standard cu care este echivalenta intrarea

respectiva. Exista intrari in

circuite

logice (ex. intrarile R, S la bistabile J-K) unde fan in-ul este 2,

echivalent cu conectarea a doua

intrari standard (fig. 3.17 c).

Fig. 3.17. Masurarea curentilor de intrare:

a) nivel logic L; b) nivel logic H; c) calcul fan out.

Dupa

cum se vede curentul de intrare are sensuri diferite pentru

nivel logic L si H. Acesti curenti sunt

asigurati de orice iesire capabila

sa comande o intrare ECL.

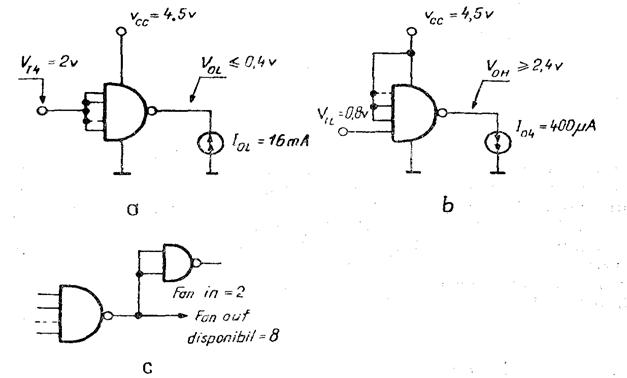

Curenti de iesire

La

poarta ECL standard orice iesire trebuie sa poata comanda pana

la 10 intrari ECL. Numarul de intrari ECL

standard ce poate fi comandat de o iesire se

numeste 'fan out'. Deci, pentru o poarta

standard fan

out-ul este 10. in fig. 3.18 sunt prezentate nivelele de

tensiune si con-

ditiile in care sunt masurate pentru cele doua valori logice L

si H.

Fig. 3.18. Masurarea curentilor de iesire:

a) nivel logic L; b) nivel logic H; c) calcul fan out.

In fig.

3.18 a se precizeaza nivelul maxim al tensiunii de iesire in

starea logica L la iesire pentru un curent de iesire

corespunzator unui

fan out de 10, iar in fig. 3.18 b se

precizeaza nivelul minim al tensiunii

de iesire in starea logica H pentru un curent

de iesire corespunzator unui

fan out de 10. in fig. 3.18 c se poate observa modul de calcul al cuplarii

intre o iesire si mai multe intrari ECL.

Pentru o cuplare corecta trebuie ca:

![]()

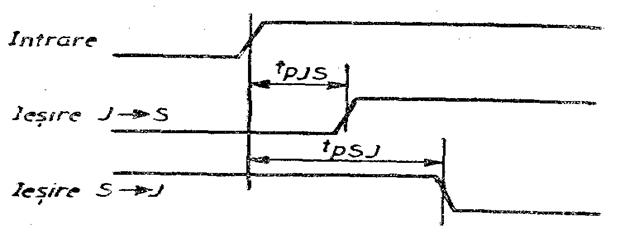

Timpul de propagare

Timpii

de propagare reprezinta decalajele de timp ce apar intre in-

trare si iesire masurate la nivelul de

1,5 V (in general la 50% din amplitudinea semnalului). Timpii

de propagare difera in general pentru tranzitii

HL sau LH la iesire. Conditiile de masura pentru

acesti timpi sunt precizate in cataloage atat referitor la

generatorul folosit pentru comanda circuitului cit si la

sarcina ce trebuie conectata la iesire.

Cunoasterea

timpilor de propagare este necesara la determinarea

intirzierii totale ce apare la propagarea unui semnal

printr-un lant de

circuite logice. Timpul total se obtine prin

cumularea timpilor de propagare individuali ai

fiecarui circuit din lantul respectiv.

CARACTERISTICI DE TIMP

Aceste

caracteristici se refera la capacitatea circuitelor digitale de a

raspunde unor schimbari ale intrarilor sau

ale impulsului de tact.

In

cazul portilor se poate vorbi numai despre asa-numitul timp de

propagare intre schimbarea unei intrari si

aparitia schimbarii corespunzatoare la iesire. Acesti

timpi pot fi diferiti la trecerea iesirii din starea "Jos'

in starea "Sus' si invers. Dupa cum se vede in figura 3.19.

Fig. 3.19. Reprezentarea timpilor de propagare pentru porti logice.

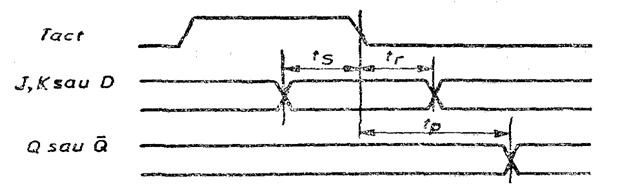

Pentru bistabili se definesc mai multe marimi temporale caracteristice:

- timpii de propagare (tp) (intre frontul activ al tactului si iesiri)

timpii de stabilire (ts) (intre momentul stabilirii intrarilor si frontul activ al tactului)

timpii de retinere (tr) (intre frontul activ al tactului si momentul in care se accepta schimbarea intrarilor).

Acesti timpi sunt ilustrati in figura 3.20.

Fig. 25.14. Reprezentarea timpilor de propagare,

de stabilire si retinere pentru bistabili.

Pe langa

acesti timpi se mai definesc frecventa maxima si durata

minima a impulsurilor de tact.

Producatorii

de circuite integrate digitale furnizeaza date despre

toti

acesti timpi in gama temperaturilor de functionare.

FAMILIILE DE CIRCUITE LOGICE INTEGRATE

In

prezent datorita versatilitatii, a fiabilitatii

ridicate si a consumu-

lui redus de putere, circuitele digitale se

utilizeaza practic numai sub

forma circuitelor integrate. in decursul timpului, pe

masura dezvoltarii

tehnologiei

si in functie de necesitatile de viteza si consum

de putere, au

fost elaborate mai multe familii de circuite

digitale integrate. Se pot

enumera familiile RTL

(resistor-transistor-logic), RCTL (resistor-capaci-

tor-transistor-logic), DTL (diode-transistor-logic), TTL (transistor-transis-

tor-logic), ECL (emiter-coupled-logic), pMOS (MOS cu canal p), nMOS

(MOS cu canal n) si CMOS

(complementary MOS).

In

momentul de fata, interes practic pentru circuitele digitale utili-

zate in radiocomunicatii,' prezinta familiile

TTL, ECL si CMOS. Familia

nMOS avand

o utilizare restransa la familiile de microprocesoare si me-

morii, dar iesiri si intrari

compatibile TTL, nu ne vom ocupa de ea se-

parat.

FAMILIA LOGICA TTL

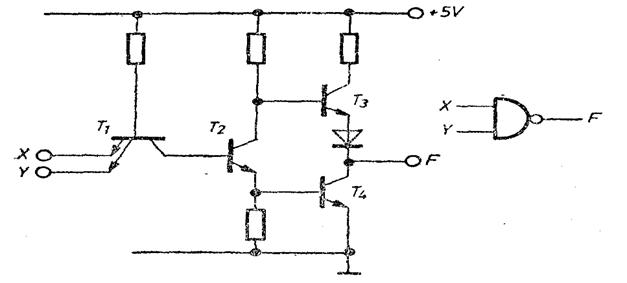

Schema electrica a unei porti SI-NU cu doua intrari este data in fig. 4.1.

Fig. 4.1. Poarta logica SI-NU TTL, schema si simbol.

Daca

una din intrarile X sau Y este pusa la un

potential apropiat

de masa, T1

va conduce curent prin jonctiunea BE determinand blocarea lui

T2, care antreneaza saturarea lui T3 si

blocarea lui T4. Daca ambele

intrari X si Y sunt la un

potential superior lui 2 V, tranzistorul Tl functioneaza

invers, (EC) determinand conductia lui T2 si a lui T4,

T3, fiind

blocat.

O

importanta deficienta a acestei familii o constituie viteza

relativ

redusa, datorita intrarii puternice in

saturatie a tranzistorilor T2, T3 sau

T4. Pentru a evita aceasta, in paralel pe jonctiunea

colector-baza a tuturor tranzistorilor a fost pusa o dioda

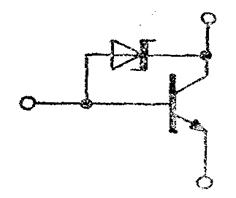

Schottky, ca in figura 4.2.

Fig. 4.2.Montarea diodei Schottky in STTL si LSTTL.

Datorita tensiunii de deschidere redusa (0,4 V) si a functionarii cu purtatori majoritari, dioda Schottky preintampina intrarea in saturatie a transistoarelor, fapt ce determina reducerea de aproximativ doua ori a timpilor de propagare.

Utilizarea

diodelor Schottky a facut ca pe langa familia logica TTL,

sa apara familiile derivate STTL si LSTTL.

Familia LSTTL (low-power

Schottky) are un consum similar cu familia TTL la

performante de viteza superioara, iar familia STTL

(Schottky) la un consum superior fata

de familia TTL, are si o viteza mult mai mare.

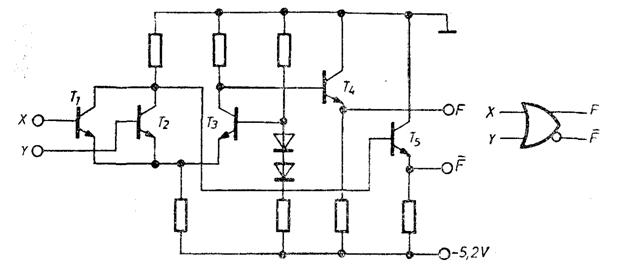

FAMILIA LOGICA ECL

Pentru a

elimina total efectele negative ale logicii saturate (TTL)

se utilizeaza familia ECL, in figura 4.3, dandu-se

schema unei porti

SAU/SAU-NU. Transistoarele T1 T2 si

T3 formeaza un amplificator diferential.

Cand una

din intrarile X sau Y este la un nivel superior bazei lui

T3 (aflata la un potential fix),

tranzistorul corespunzator T1 sau T2, va

conduce determinand o conductie slaba a lui T5,

iar T3 fiind blocat T4 va

conduce puternic. Astfel, pe iesirea F se

obtine nivelul superior de ten-

siune iar pe iesirea F nivelul inferior.

Fig. 4.3. Poarta logica SAU/SAU-NU ECL, schema si simbol.

Daca

ambele intrari X si Y se afla la un potential

inferior fata de

cel al bazei lui T3, aceasta va conduce iar T1 si T2 vor fi blocate, determinand

conductia slaba a lui T4 si conductia

puternica a lui T5. In aceste

conditii iesirea F va fi la nivelul inferior de

tensiune iar F la nivelul

superior.

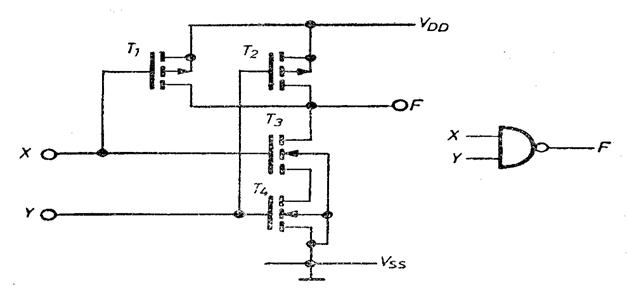

FAMILIA LOGICA CMOS.

Aceasta

familie a fost introdusa in scopul reducerii consumului de

putere, pentru aplicatii care nu necesita

viteza mare de lucru. Schema

unei porti SI-NU, de tip CMOS, este data in figura 4.4.

Fig. 4.4. Poarta logica SI-NU CMOS, schema si simbol.

Se

utilizeaza transistoare MOSFET cu imbogatire. Daca una din

intrari, X

sau Y, este la un nivel inferior de tensiune astfel incat se depaseste

tensiunea de prag pentru T1 sau T2 (MOSFET cu canal p)

si nu depaseste tensiunea de prag pentru T3

si T4 (MOSFET cu canal n) iesirea

F va fi la un nivel de tensiune practic VDD, pentru

ca Tt sau T2 va conduce

iar T3 si T4 vor fi blocate. Daca

ambele intrari, X si Y, vor fi lao

tensiune suficient de mare, incat se depaseste tensiunea de prag

pentru T3, si T4 si nu se

depaseste tensiunea de prag pentru Tt si T2,

nivelul de tensiune pe iesirea F va fi practic Vss,

T3 si T4 fiind in conductie iar T1

si T2 blocate.

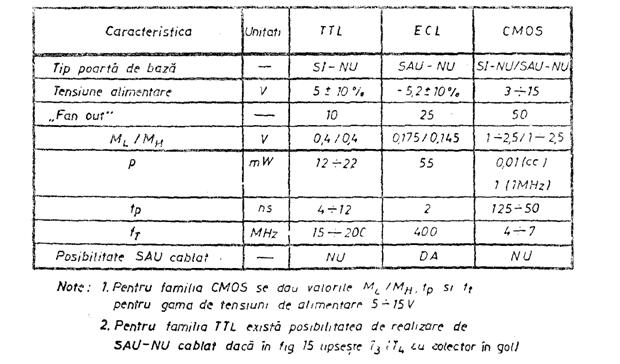

COMPARATIA FAMILIILOR LOGICE INTEGRATE

Pentru a putea face o comparatie intre familiile logice de mai sus, este necesar sa definim cativa parametrii importanti:

ViLmax - tensiunea de intrare maxima admisa pentru starea "jos'

ViHmax - tensiunea de intrare minima admisa in starea "sus'

VoLmax/IoL - tensiunea de iesire maxim admisa in starea "jos'/la

un curent de iesire dat

VoHmin/IoH![]() - tensiunea de iesire

minima admisa in starea "sus'/la un

curent de iesire dat

- tensiunea de iesire

minima admisa in starea "sus'/la un

curent de iesire dat

MH - marginea de zgomot superioara

(MH = VoHmax -ViHmax)

ML - marginea de zgomot inferioara

(ML =VoLmax-ViLma.)

"Fan-out' - nr. de intrari standard din aceeasi familie pe care le poate ataca o iesire mentinandu-se in parametri

tp - timpul de propagare a semnalului printr-o poarta

fT - frecventa maxima de tact pentru bistabili

P - puterea disipata de o poarta.

Comparatie intre familiile logice TTL, ECL si CMOS

Tabelul 4.1

Fig. 4.5. Interfatarea intre familiile logice.

Odata

definiti, acesti parametri se poate face o comparatie sintetica

a celor trei familii logice prezentate. Aceasta comparatie se face in

tabelul 4.1. In acest tabel se analizeaza si posibilitatea de

realizare pentru SAU cablat, prin punerea in paralel a mai

multor iesiri. Aceasta posibilitate tipica

pentru familia ECL este foarte utila mai ales cand e necesara

realizarea unor porti SAU cu multe intrari.

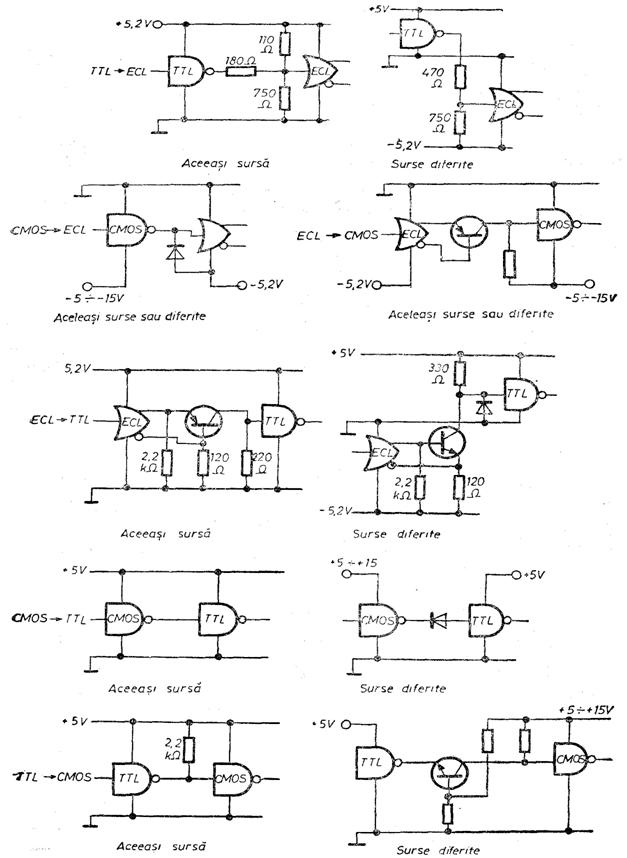

Circuitele

logice integrate sunt in prezent un domeniu in plina expansiune,

iar imbunatatirile tehnologice sunt la baza sporirii continue a

performantelor electrice.

In

echipamentele de radiocomunicatii este deseori necesara, utilizarea

mai multor familii logice, care se interconecteaza intre ele fie prin

intermediul unor circuite integrate speciale, fie prin

intermediul unor

circuite simple de tipul celor din figura 4.5.

BIBLIOGRAFIE

1.De la poarta TTL la MICROPROCESOR I.Sztojanov,E.Borcoci,s.a.

2.Manualul Inginerului Electronist vol.III Edmon Nicolau,s.a.

3.Numaratoare Electronice R.M.M.Oberman prof.Universitatea

Tehnica Delf

4.Componente si Circuite Electronice-manual ptr. Cls.a XI-a si a XII-a Theodor Danila, Monica Ionescu-Vaida

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 10361

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2026 . All rights reserved