| CATEGORII DOCUMENTE |

| Bulgara | Ceha slovaca | Croata | Engleza | Estona | Finlandeza | Franceza |

| Germana | Italiana | Letona | Lituaniana | Maghiara | Olandeza | Poloneza |

| Sarba | Slovena | Spaniola | Suedeza | Turca | Ucraineana |

DOCUMENTE SIMILARE |

|

DAŽNIO, SUKIMOSI KAMPO SKAITMENINIAI KEITIKLIAI

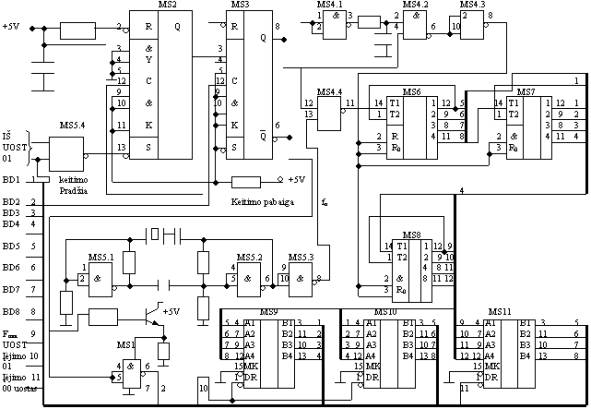

Panagrinëkime skaitmeninio dažnio Fmat matavimo interfeiso schemos veikimą. Šis interfeisas paremtas stabilizuoto dažnio fst=I/Tst periodř Tst, užpildančiř matuojamą laiko intervalą Tmat =I/Fmat, skaičiaus matavimu. Já sudaro žemo ir vidutinio integracijos laipsnio mikroschemos: IR – NE grandinëlës MS1, MS4, MS5 (KP155LA3), J-K trigeriai MS2, MS3 (KP155TM2), 4 skilčiř dvejetainiai skaitikliai MS9 – MS11 (KP589AP16), tranzistorius T, kvarco kristalas Z, keletas rezistoriř ir kondensatoriř. Trigeriai MS2 ir MS3 realizuoja dažnio Fmat paduodamo á MS3 C áëjimą, kontrolinio signalo formatuką. Padavus á MS2 S áëjimą loginio Æ signalą, kurá suformuoja MS5.4 iš DÆ bito ir iš išëjimo uosto OIH išrinkimo signalo, trigerio MS2 išëjime O atsiranda loginis I. Trigerio MS3 išëjime Q loginis 1 atsiranda, atsiranda tik atëjus Fmat signalo priekiniam frontui á MS3 áëjimą C. Dël to paleidžiamas laukiantis multivibratorius MS4.1 – MS4.3, generuojantis trumpalaiká impulsą, išvalantá skaitiklius MS6 – MS8. Be to, loginis 1 trigerio MS3 išëjime atidaro grandinëlę MS4.4, per kurią iš MS5.3 išëjimo pasiduoda stabilizuoto dažnio fst signalas á MS6 T áëjimą. Čia dažnio fst generatorius sudarytas iš MS5.1 – MS5.3, o 12 skilčiř skaitiklis – iš MS6 – MS8. Keitimo pabaigos signalas suformuotas MS3 Q išëjime ir paduodamas á vienos skilties áëjimo uostą MS1 adresu ÆÆH. Šis uostas gauna maitinimą per tranzistoriř T tik tada, kai á tranzistoriaus bazę ateina uosto išrinkimo signalas ÆÆH (iš adreso ÆÆ ir BB4T signalř, ávykdžius IN ÆÆH komandą). Tuomet iš uosto ÆÆH á davikliř magistralës liniją BD1 nuskaitomas keitimo pabaigos signalas. Atëjus sekančiam Fmat signalo priekiniam frontui, trigeris MS3 pereina á kitą stabilią bűseną. Dël to jo išëjime Q atsiranda loginis Æ, o Q – loginis 1 (keitimo pabaiga), MS4.4 užsidaro, o skaitikliai sustoja, išsaugodami skaitmeniná kodą, atitinkantá išmatuotą dažná Fmat, šis kodas nuskaitomas á MKK daviniř magistralę per formuotuvus MS9 – MS11 dviem ciklais. Pirmuoju ciklu adresu 01H išrenkamos mikroschemos MS9 ir MS10 ir nuskaitomas skaitikliř MS6, MS7 turinys. Antru ciklu adresu ÆÆH išrenkamas áëjimo uostas MS11, per linijas D4 – D7 nuskaitantis likusią informaciją: MS8 išëjimř turiná. Aktyvűs, esant loginiam nuliui, uostř išrinkimo signalai čia ir kitais atvejais formuojami ARBA grandinële: áëjimo uostui iš signalř BB4T ir “Uosto adresas”; išëjimo uostui – iš signalř BB3P ir “Uosto adresas”. “Uosto adresas” formuojamas dešifratoriumi o BB3P ir BB4T – tai standartiniai MKK valdymo magistralës signalai.

Dažnio keitiklis DK-3 tai árenginys, skirtas kintamos átampos trifaziř asinchroniniř elektros varikliř valdymui ir sűkiř reguliavimui. Jis sukuria keičiamo dažnio ir átampos trifazá elektros tinklą. Variklio sukimo momentas gali bűti išlaikomas nepriklausomu nuo sűkiř arba mažëti jiems mažëjant. Keitiklis leidžia keisti dažná nuo 0 iki 60 Hz ir valdyti variklius, kuriř galia iki 15 kW. DK-3 veikia impulsř pločio moduliavimo principu, kas garantuoja sinusinę variklio apvijř srovës formą. Dažnis gali bűti keičiamas: rankiniu bűdu keitiklio valdymo skydelyje arba distancinio valdymo pultelyje esančia rankenële; analoginiais (0-5) mA, (0-20) mA, (4-20) mA, (0-10) V signalais iš kitř árenginiř; automatiškai specialios elektroninës schemos pagalba tokiu bűdu, kad bűtř palaikoma pastovi užduota valdomos sistemos parametro (slëgio, temperatűros, srauto ir kt.) reikšmë. Keitiklis turi apsaugas: nuo išëjimo srovës padidëjimo (perkrautas variklis); per aukštos arba per žemos tinklo átampos; tinklo fazës dingimo; per aukštos keitiklio išëjimo elementř temperatűros; keitiklio išëjime užtrumpinimo á 'žemę' arba á tinklo fazę. Suveikus apsaugai ir išnykus priežasčiai dël kurios ji suveikë, keitiklis gali vël automatiškai ájungti variklá. Perdegus variklio apvijoms arba keitiklio išëjimo elementams keitiklis gali ájungti rezerviná árenginá.

Sinchronizacijos mazgř formavimas. Panagrinëkime galios keitikliř skaitmeninës sinchronizacijos su tinklu mazgř sudarymo principus. Apsiribokime trifazio lygintuvo, skaitmeninës sinchronizacijos mazgo sukűrimu. Keitiklio tiristoriai turi bűti komutuojami pagal átampř vektorinę diagramą kas 1/6 periodo. Praktiškai buvo ásitikinta, kad sinchronizacijos su tinklo átampa momentais patogiausia laikyti faziniř átampř teigiamř pusperiodžiř perëjimo per nulius momentus. Tuo principu sukonstruota skaitmeninës sinchronizacijos schema. Ši schema leidžia suformuoti trumpalaikius impulsus UA, UB, UC, U’A, U’B, U’C, atsirandančius faziniř átampř UA, UB, UC, U’A, U’B, U’C teigiamř pusperiodžiř pradžiose. Ši schema patikimai generuoja sinchroimpulsus ir tuo atveju, kai tinklo átampos nëra sinusinës. Schemą sudaro 6 identiški kanalai, kuriuose yra stiprintuvai – ribotuvai 1, 4, 7, 10, 13, loginës IR – NE grandinëlës su 3 áëjimais 2, 5, 8, 11, 14 ir 17, sinchronizacijos impulsř formatuvai 3, 6, 9, 12, 15 ir 18. Stiprintuvř – ribotuvř, surinktř operaciniř stiprintuvř, fiksuojančiř nulinę átampą, pagrindu išëjimai pajungiami prie IR – NE grandinëliř viršutiniř áëjimř. Kiekvienos IR – NE grandinëlës išëjimas pajungiamas prie kanalo impulsř formuotuvo áëjimo ir prie viduriniř kitř dviejř kanalř IR – NE grandinëliř áëjimř. Visi stiprintuvai formuoja stačiakampës formos átampas U1 – U6 tuo metu, kai jř áëjimuose yra átampř UA, UB, UC, U’A, U’B, U’C, neigiami pusperiodžiai, o teigiamř pusperiodžiř metu jř išëjimuose atsiranda Æ (ir tik tuomet išëjime bus loginis 1) intervaluose 2400<V<3600. Tuo bűdu loginis 1 IR – NE grandinëlës išëjime atsiranda sinchronizuojamos fazës átampai pereinant 0, t.y., esant V=3600. Šiuo momentu ir paleidžiamas trumpo sinchroimpulso formavimo árenginiai, generuojantis átampas UA, UB, UC, U’A, U’B, U’C. Šis bűdas naudingas, apsaugant sistemą nuo vienos fazës prapuolimo. Tuomet šios fazës stiprintuve – ribotuve sukuriamas loginis 1 ir visa sistema nutraukia sinchroimpulsř generaciją.

Greitaveikë skaitmeninë fazës impulsř moduliacija ir interfeisas. Valdomř galios keitikliř impulsinio fazinio valdymo sistemos (IFVS) dažniausiai realizuojamos, panaudojant dviejř tolydiniř (analoginiř) átampř vertikalaus palyginimo principą. Viena šiř átampř bűna valdančioji, o kita – pjűklo formos átampa, generuojama kiekvienos fazës teigiamo pusperiodžio pradžioje ir besitęsianti visą šá pusperiodá. Pasinaudodami schema panagrinëkime IFVS sukűrimo dvifaziniam valdomam lygintuvui principą. Šio lygintuvo vidutinë išlyginta átampa Uvid=1/2*Uvid0*(1+cosa), čia Uvid0=2Uf/p*m, priklauso nuo ventiliř ájungimo kampo a, atskaitomo nuo teigiamo fazinës átampos pusperiodžio pradžios (átampos A ir A’). Realizuojant tolydinę (analoginę) átampą IFVS, valdanti átampa UVA sulyginama su pjűklo formos átampa UPA (diagrama UVSA). Dažniausiai átampa UVA yra uždaranti tam tikrą palyginimo elementą (pvz., stiprintuvą) átampa, o UPA - atidaranti šá elementą átampa. Kai átampa UPA pasiekia valdančios átampos reikšmę UVA, palyginimo elementas atsidaro ir suformuojamas impulsas Ua (Ua átampř diagrama), atidarantis atitinkamą ventilá kampu a. Jei UVA=UVA1 yra didesnë, tai atidarymo kampas a a taip pat turi didesnę reikšmę. Kai valdymo átampa šuoliu sumažëja nuo UVA1 iki UVA2 vertës, gaunamas tarpinis kampas a , atsirandantis valdančiosios átampos pokyčio metu. Naują valdančios átampos reikšmę UVA2 atitinkantis kampas a atsiranda sekančiame pusperiodyje. Tokiu bűdu, tolydinë vertikalaus palyginimo IFVS patikimai generuoja valdymo impulsus, esant bet kokiems valdančios átampos pokyčiams ir turi didžiausią greitaveiksmiškumą impulsiniř keitikliř valdymo sistemř tarpe.

Schemoje parodyta vieno kanalo didžiausio greitaveiksmiškumo skaitmeninë IFVS, veikianti vertikalaus palyginimo principu ir turinti žymiai didesná tikslumą už tolydinę sistemą. Ją sudaro: n skilčiř valdantá kodą UVS invertuojantis blokas 1, takto impulsř generatorius 2, nulio fiksavimo organas 3, takto skaitiklis 4, sumatorius 5 ir išëjimo impulsř formuotuvas 6. Á bloką 1 paduodamas valdantis kodas UVS, atitinkantis duotą valdymo kampą a. Iš bloko 1 invertuotas kodas U’VS paduodamas á n skilčiř sumatoriaus A áëjimus. Á šio sumatoriaus B áëjimus pajungti dvejetainio skaitiklio n išëjimai. Á sumatoriaus áëjimą P1 paduotas loginio 1 lygis U1. Sumatoriaus išëjimas “Perpildymas P” pajungtas prie impulsř formavimo bloko 6, generuojančio kanalo tiristoriaus paleidimo impulsus. Schema veikia taip. Nulio fiksavimo organas, kuris gali bűti vienas iš schemos kanalř, formuoja trumpus sinchroimpulsus Usinchr (diagrama Usinchr), laiko momentais, kai fazinës átampos eina per 0. Veikiant šiems impulsams, takto impulsř skaitiklis periodiškai išvalomas ir pradeda skaičiuoti takto impulsř generatoriaus 2 impulsus (diagrama Utakt). Skaitmeninis kodas UPS, sukauptas skaitiklyje, auga proporcingai laikotarpiui, atskaitomas nuo paskutinio sinchroimpulso Usinchr pasirodymo momento, kuriame a.=0. Šis kodas parodytas diagramoje USVS laiptuotos kreivës pavidalu. Jis atitinka faziniam kampui V w*t, besikeičiančiam nuo 0 iki p. Kadangi á sumatoriaus A áëjimą paduodamas U’VS, o á P1 áëjimą – loginis 1, tai U’VS +1= papildomam kodui nuo to kodo UVS, kuris atitinka duotą kampą a. Á B áëjimus kaip tik ir paduodamas šis kodas. Yra žinoma, kad tiesioginio bei papildomo kodř suma visada lygi 0, atsirandant pernešimo bitui. Be to, jei á B áëjimus bus paduotas didesnis kodas, tai pernešimo bitas taip pat atsiranda. Tik tuo atveju suma nebus lygi nuliui.

Pateikti pavyzdžiai patvirtina faktą, kad tiesioginio ir atvirkštinio kodř suma duoda 0 ir pernešimo bitą P. Be to, jei ávyko staigus a kodo sumažëjimas, o tuo metu kodas B áëjimuose pasidaro didesnis už sumažëjusá a kodą, P pernešimo išëjime tuoj pat atsiranda loginis 1, kuris panaudojamas kanalo tiristoriaus paleidimo impulsui formuoti. Skaitmeninës IFVS realizavimo tikslumas priklauso nuo skilčiř n skaičiaus, apsprendžiančio laiptelio aukštá ULSB=Uat/2n-1, čia Uat – atraminë átampa, atitinkanti kampą a p. Nuo n taip pat priklauso ir takto impulsř dažnis

ftakt=2n+1/Ttinklo

Jei ftinklo=1/Ttinklo=50 Hz, tai

ftakt=100*2n Hz

Tuomet, esant n=8,

ftakt=100*28=25,6 kHz,

esant n=12,

ftakt=100*212=409,6 kHz.

Panagrinëkime tokios sistemos ir MKK interfeisą 6 faziř tiristorinio keitiklio atveju. Loginë tokio interfeiso struktűra parodyta schemoje. Schema sudaryta 12 bitř a kodo atvejui. Ją sudaro: blokas 1 – vyresnio a kodo baito ávedimo uostas, blokas 2 – jaunesnio a kodo baito ávedimo uostas, takto impulsř generatorius 3, nulá fiksuojantys organai 4 – 9, 12 bitř dvejetainiai skaitikliai 10 – 15, 12 bitř sumatoriai 16 – 21, kanalř tiristoriř paleidimo impulsř formuotuvai 22 – 27. Jei tinklo dažnis ftinklo=50 Hz, tai takto impulsř dažnis turi bűti ftakt=409,6 kHz. Kadangi nulio organai fiksuoja faziniř átampř perëjimo per 0 momentus, o linijiniř átampř natűralios komutacijos momentai nuo jř atsilieka 300 tai a kodas, kurá perduos MKK per savo daviniř magistralę DÆ - D7, išëjimo uostus 1 ir 2 á sumatoriř áëjimo magistralę BÆ - B11, turi bűti ne mažesnis už 300. Tai turi bűti dël to, kad tiristoriř paleidimo impulsai neateitř anksčiau už linijiniř átampř natűralios komutacijos momentus.

Mažo galingumo puslaidininkiniř pavarř

mikroprocesorinio valdymo interfeisas. Puslaidininkinës nuolatinës

srovës pavaros, kuriose realizuojamas impulsř trukmës

moduliacijos (ITM) principas, neretai konstruojamas pagal schemą. Šioje schemoje reversiná keitiklá sudaro

tranzistoriai V18 – V21, šuntuoti atbuliniais diodais V22 – V25. Kai

ájungti tranzistoriai V18 ir V21, variklis EV sukasi á vieną pusę, o

kai ájungti tranzistoriai V20 ir V19, EV sukasi á kitą pusę. Kad

reverso metu išvengti trumpo jungimo sroviř, ájungti droseliai

“Droselis

Loginë ITM keitiklio ir MKK interfeiso struktűra. Ją sudaro: ITM keitiklis V1 – V4, impulsinis greičio daviklis IGD, adresř dešifratorius AD, skaitmeninis l keitiklis SlK, moduliacijos režimo nustatymo blokas MRB, impulsř skaitiklis IS, impulsř sekos tikrinimo blokas ISTB, galvalinio atrišimo mazgai GAM, impulsiniř stiprintuvř blokas ISB, kampo skaitmeninis keitiklis KSK, analoginis skaitmeninis keitiklis ASK, srovës ribotuvas SR, áëjimo uostai 40, 50 ir 54, išëjimo uostai 44, 48 ir 50. Blokas MRB per išvedimo uostą 40 nustato atitinkamř EV sukimosi kryptá, o per išvedimo uostą 50 – reikiamą moduliacijos dësná. Duota impulsř trukmës l kodo reikšmë daviniř magistrale per išvedimo uostą 54 užrašoma á SlK buferiná registrą. Iš uosto 40 atëjus signalui “Paleidimas”, paleidžiamas ITM takto impulsř generatorius (ftakto=1 kHz). Kiekvieno šio impulso priekinio fronto momentu ávyksta daviniř iš SlK buferio perrašymas á žemyn skaičiuojantá skaitiklá ir generuojama galios ventiliř atidarymo impulsř pradžia. Buferio kodo nuskaitymas vyksta MKK takto impulsř dažniu (2MHz) iki skaitiklis užpildomas nuliais. Tada atsiranda galios ventiliř uždarymo impulsas (l pabaigos momentas). Schemoje realizuojamas neigiamas grážtamas ryšys pagal srovę grandine: Rš GAM ASK, ávedimo uostą 56 ir magistralę DÆ - D7. Srovës I signalas, sukuriamas SlK bloke, yra programiškai filtruojamas, 4 kartus matuojant srovës reikšmę ir skaičiuojant vidutinę matavimř vertę. Neigiamo ryšio pagal greitá signalas realizuojamas KSK ir IGD blokuose. KSK blokas veikia, palaipsniui užpildant IGD impulsř intervalus žinomo pastovaus dažnio impulsais. Kad padidinti bloko tikslumą, jo skilčiř skaičius pasirinktas 12. KSK informacija nuskaitoma dviem žingsniais. Pirmu žingsniu per áëjimo uostą 48 nuskaitomos jaunesnës informacijos skiltys BÆ - B7, o antru – per áëjimo uostą 44 – vyresnës B8 - B11. Kad nenuskaityti informaciją jos keitimosi metu, KSK sinchronizuojamas per áëjimo uostą 44. Galios keitikliř trumpř jungimř srovëms išvengti naudojamas ISTB, draudžiantis vienu metu atidaryti ventilius V1 bei V4 arba V3 ir V2. Schemos valdymo algoritmą galima lanksčiai keisti, pasirenkant norimą programą.

1).Prof. A. A. Bielskio kompiuterio elektronikos paskaitř konspektai.

2).www.pfi.lt/news_prietaisai.html#DK-3

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2346

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved