| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

Modelarea mixta-Multiplicator pe 8 biti

1 Specificatii

Scopul prezentei lucrari de laborator este acela de a prezenta in limbaj VHDL stilul de modelare mixt aplicat unui multiplicator pe 8 biti.

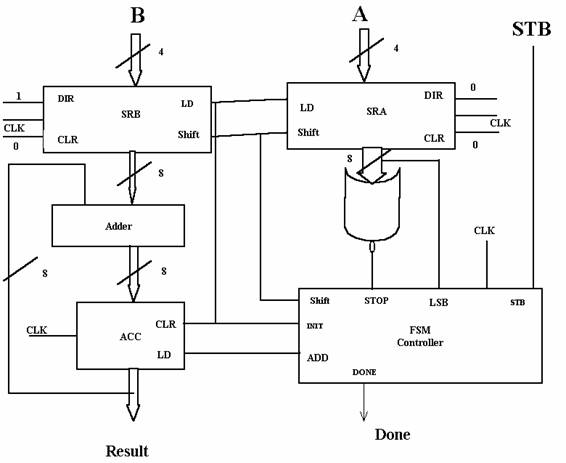

Schema bloc a multiplicatorului este prezentata in figura 1 :

Fig.1 Schema bloc a multiplicatorului pe 8 biti

Semnalele de intrare sint: clock, strobe - pentru startarea masinii si cei doi vectori de multiplicat A si B pe 4 biti.

Semnalele de iesire sint: "Result" pe 8 biti care indica rezultatul si "Done" care indica valabilitatea rezultatului.

Cind semnalul STB este primit, controlerul este resetat si genereaza un impuls INIT care initializeaza acumulatorul si incarca valorile intrarilor A si B in cei doi registri: SRA si SRB, care implementeaza A:=A div 2, respectiv B:=2*B. Controlerul utilizat este chiar cel descris in lucrarea de laborator numarul 4.

Cind semnalul ADD este receptionat continutul curent al acumulatorului este adunat la cel al registrului SRB noul rezultat fiind apoi memorat in acumulator.

Aceste semnale sint generate ca raspuns la bitul LSB preluat direct din cel mai putin semnificativ bit al SRA si la bitul STOP, care este functia logica NOR a celor 8 biti din iesirea registrului SRA.

2 Implementare

Declaratia de entitate a multiplicatorului este:

(fisier Multiplier8.vhd)

3 entity Mult8 is

4 port ( A, B : in Bit_Vector ( 3 downto 0);

5 STB : in Bit;

6 CLK: in Bit;

7 Reset : in Bit;

8 Result : out Bit_Vector ( 7 downto 0);

9 Done : out Bit );

10 end Mult8;

14 architecture IterativeAdd of Mult8 is

16 use work.Components .all;

18 signal SRAout, SRBout : Bit_Vector ( 7 downto 0);

19 signal ADDout, ACCout : Bit_Vector ( 7 downto 0);

20 signal Init, Shift, Add, Stop : Bit := '0' ;

22 signal High : Bit := '1';

23 signal Low : Bit := '0';

24 signal OFL : Bit;

26 signal ACCclk, ACCclr : Bit;

28 begin

30 ACCclr <= not (Init or Reset);

31 ACCclk <= CLK and Add;

32 Result <= ACCout;

34 SRA: ShiftN port map

35 ( CLK => CLK,

36 CLR => Low,

37 LD => Init,

38 SH => Shift,

39 DIR =>Low,

40 D => A,

41 Q => SRAout );

43 SRB: ShiftN port map

44 ( CLK => CLK,

45 CLR => Low,

46 LD => Init,

47 SH => Shift,

48 DIR =>High,

49 D => B,

50 Q => SRBout );

52 ALU: Adder8 port map

53 ( ACCout, SRBout, Cin => Low, Cout => OFL, Sum => ADDout);

55 ACC: Latch8 port map

56 ( ADDout, Q=> ACCout, Pre => High, Clk => ACCclk, Clr => ACCclr);

58 CHK: Stop <= not ( SRAout(7) or SRAout (6) or SRAout(5) or SRAout (4) or 59 SRAout(3) or SRAout (2) or SRAout(1) or SRAout (0) );

61 FSM: Controller port map

62 ( STB, CLK, SRAout(0), Stop, Init, Shift, Add, Done);

64 end;

Semnalul "Result" este declarat la linia 8 ca fiind port de iesire. Semnalul intern "ACCout" declarat la linia 19 va comanda portul de iesire "Result" (linia 32) .

Corpul arhitecturii utilizeaza specificatii de atribuire pentru semnale (liniile 30,31,32 si 58-59) pentru a descrie o parte a circuitului si specificatii pentru instantieri de componente. Posibilitatea de a utiliza stiluri de descriere diferite in aceeasi arhitectura reprezinta unul din avantajele utilizarii limbajului VHDL.

Declaratiile de componente pentru instantieri sint in pachetul "Components" iar clauza "use" de la linia 16 face posibila utilizarea lor in corpul arhitecturii.

Instantierile de componente introduc una din capabilitatile VHDL. Instantierea controlerului (liniile 61-62) asociaza semnalele cu componentele porturilor utilizind asocierea pozitionala (positional association).

In asocierea pozitionala, primul semnal din lista de porturi corespunde primului port al componentei, al doilea semnal cu al doilea port, s.a.m.d .

Pentru controler putem construi urmatorul tabel cu asocieri porturi-semnale:

|

Porturi controler |

STB |

CLK |

LSB |

Stop |

Init |

Shift |

Add |

Done |

|

Semnale multiplicator |

STB |

CLK |

SRAout(0) |

Stop |

Init |

Shift |

Add |

Done |

Aceste asocieri mai pot fi facute explicit utilizind asocierea numelor (named association). De exemplu, la instantierea registrului de deplasare (liniile 34-41) fiecare asociere in lista portului este de forma " componenta port => semnal multiplicator ".

Este posibila combinarea dintre asocierea formala si cea a numelor in aceeasi lista de asocieri (liniile 52 si 53).

Toate asocierile pozitionale, daca exista, trebuie sa preceada asocierea numelor. In caz contrar, compilatorul VHDL nu poate stabili corect asocierea dintre valorile actuale si cele formale.

3 Testare

In fisierul Test_Multiplier8.vhd este prezentat un program de test pentru multiplicator.

(fisier Test_Multiplier8.vhd)

69 entity Test_Mult8 is end;

73 architecture Driver of Test_Mult8 is

75 component Mult8

76 port ( A,B : in Bit_Vector ( 3 downto 0);

77 STB : in Bit;

78 CLK : in Bit;

79 Reset : in Bit;

80 Result : out Bit_Vector ( 7 downto 0);

81 Done: out Bit );0

82 end component;

84 signal A,B : Bit_Vector ( 3 downto 0);

85 signal STB,DOne : Bit := '0' ;

86 signal CLK : Bit ;

87 signal Reset : Bit;

88 signal Result : Bit_Vector ( 7 downto 0);

90 signal DisplayA, DisplayB, DisplayResult : Natural ;

92 use work.Utils.all;

94 begin

96 C :Clock (CLK, 10ns, 10 ns);

98 UUT: Mult8 port map (A,B,STB,CLK,Reset,Result, Done);

100 Reset <= '1' ,'0' after 1ns;

102 Stimulus:

103 process

104 begin

105 for i in 1 to 3 loop

106 for j in 4 to 7 loop

107 DisplayA <= i;

108 DisplayB <= j;

109 A <= Convert ( i, A'Length );

110 B <= Convert ( j, B'length);

111 wait until CLK'Event and CLK='1';

112 STB <='1', '0' after 20ns;

113 wait until Done ='1';

114 DisplayResult <= Convert(Result);

115 wait until CLK'Event and CLK = '1' ;

116 end loop;

117 end loop;

118 wait;

119 end process;

121 end;

Procedura "Clock" din pachetul "utilities" este folosita aici ca procedura cu apel concurent (apare in corpul arhitecturii, si nu in corpul unui proces) la generarea semnalului de tact pentru multiplicator si testbench.

Generatorul de stimuli (102-119) utilizeaza doua bucle imbricate pentru a testa multiplicatorul cu valorile si pentru porturile de intrare A, respectiv B .

In interiorul buclei valorile de multiplicat sint aplicate mai intii semnalelor "DisplayA" si "DisplayB" pentru a putea fi afisate ca intregi ( liniile 107,108), apoi sint convertite in tipuri Bit_Vector. Specificatiile de la liniile (109,110) apeleaza secvential

(in corpul procesului) functiile Convert corespunzatoare din pachetul utilities si atribuie rezultatele conversiilor intrarilor multiplicatorului.

Specificatia wait de la linia 111 semnalizeaza aparitia unui front crescator al semnalului de tact. Conditia until este cea mai generala forma de expresie sensitiva la un eveniment.

Semnalul STB este apoi validat pentru a permite initializarea multiplicatorului (linia 112).

Urmatoarea specificatie wait (linia 113) produce suspendarea procesului pentru ca multiplicatorul sa indice valabilitatea rezultatului.

Rezultatul inmultirii este apoi convertit la un tip intreg si atribuit semnalului "DisplayResult" .

Specificatia wait de la linia 115 suspenda procesul pina la urmatorul front al semnalului de ceas pentru a permite vizualizarea rezultatului.

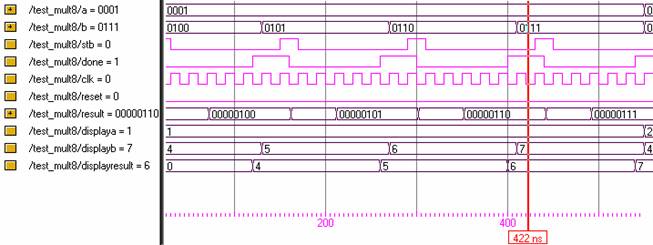

4 Rezultatele simularii

Rezultatele simularii entitatii Mult8 cu arhitectura IterativeAdd prezentate in figura 2, sint preluate din fereastra Wave a programului Modelsim.

Comparati rezultatele obtinute de propria simulare a circutului de test cu cele de mai jos. Daca rezultatele nu coincid atrageti atentia conducatorului lucrarii de laborator!

Fig.2 Rezultatele obtinute cu arhitectura Driver a entitatii Test_Mult8

TEMA

Imaginati si descrieti un alt program de test pentru entitatea Mult8, utilizind de exemplu, metoda de citire a vectorilor de test dintr-un tablou ( laboratorul 1).

In cazul incheierii cu succes a cerintei de la punctul 1, comparati rezultatele proprii cu cele de la laborator si semnalizati eventualele neconcordante conducatorului lucrarii de laborator.

Proiectati sumatorul pe 8 biti, "Adder8", si latch-ul pe 8 biti, "Latch8" in care toate porturile si semnalele sint de tip std_logic.

In package-ul "Utils" prezentat la laborator, proiectati si includeti functiile de conversie "Convert" cu tip returnat, respectiv, argument de tip std_logic.

Proiectati arhitectura "IterativeADD_standardlogic" a entitatii "Mult8" in care toate porturile si semnalele sint de tip std_logic.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1677

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved