| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

Registrul PISO

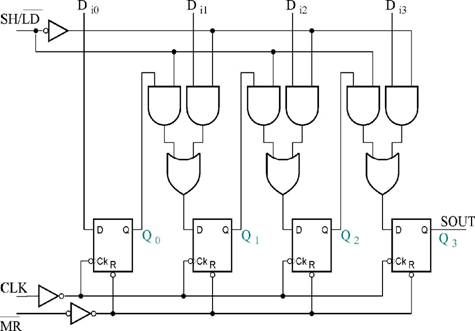

Acest registru permite inscrierea paralela a celor n biti si deplasarea informatiei intr-un singur sens. In figura 5.12 este prezentat un exemplu de registru PISO avand n = 4 biti. Cele trei multiplexoare pe doi biti formate din porti SI-SAU permit inscrierea si deplasarea informatiei. Si in acest caz daca in locul bistabilelor D MS sau D active pe front s-ar utiliza latch-uri D cu intrare de validare, functionarea registrului nu ar mai fi corecta.

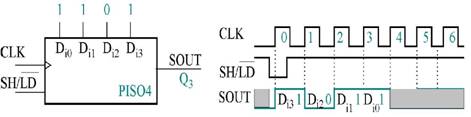

Inscrierea (paralel): Presupunem ca dorim sa scriem cuvantul 1101. La intrarile Di3 Di0 se aplica paralel cuvantul dorit (1101). Pentru inscrierea efectiva SH/nLD = 0 si apoi se aplica un impuls de tact. Informatia prezenta la intrarile Di3 Di0 se va memora in bistabile si se va regasi la iesirile Q , , Q . Doar Q este accesibil sub denumirea de SOUT (Serial Out). In acest caz nu este necesara o initializare pe "0" a bistabilelor registrului deoarece informatia inscrisa paralel va suprascrie oricum registrul. Pentru a obtine la iesire informatia inscrisa paralel sunt necesare doar n - 1 = 3 semnale de tact, deoarece la primul semnal de tact SOUT contine deja Di3 (figura 5.13).

Deplasarea informatiei se realizeaza pentru SH/nLD = 1, cate un bit pentru fiecare impuls de tact.

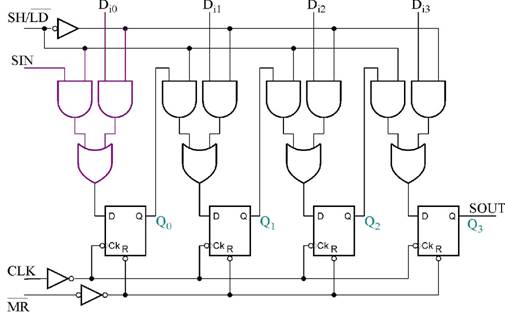

Circuitul din figura 5.12 poate fi modificat pentru a permite si intrarea seriala a datelor. In acest sens este adaugat un multiplexor suplimentar la intrarea primului bistabil si este prevazuta intrarea SIN (figura 5.14). Functionarea ca registru PISO este similara cu cea deja prezentata. Configurat ca registru SISO, informatia trebuie furnizata serial la SIN, bit cu bit, fiecare bit valid fiind urmat de o tranzitie activa JOS SUS a semnalului de tact (atentie! si in acest caz trebuie respectati timpii de stabilire si de mentinere specificati in catalog pentru registru).

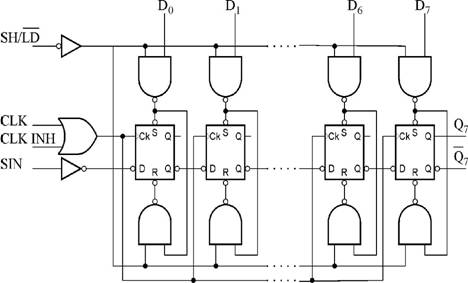

1. 74LS165 - registru combinat de 8 biti cu incarcare paralel PISO, SISO

74LS165 este un registru combinat care permite deplasarea informatiei de la stanga la dreapta si inscriere seriala (functionare ca SISO) sau paralela (functionare ca PISO).

![]()

Incarcarea paralel are loc pentru SH / LD = 0 , iar deplasarea informatiei la dreapta pentru

![]()

SH / LD =1. Mai sunt oferite ca facilitati suplimentarea un pin de inhibare a semnalului de tact (CLK

![]()

INH), iar iesirea seriala este disponibila si negata ( Q si Q

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1546

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved