| CATEGORII DOCUMENTE |

INTRODUCERE IN UTILIZAREA LIMBAJULUI VHDL COMPILAREA SI SIMULAREA UNUI DESIGN

I.1 SCOP

Lucrarea de laborator are ca scop familiarizarea cu utilizarea sistemului VHDL si cu programul Modelsim al firmei Mentor Graphics. De asemenea, se introduc citeva notiuni de limbaj si de conceptie care sa permita descrierea si simularea unui circuit simplu: sumatorul de un bit.

I.2 PARTICULARITATI ale VHDL (VHSIC Hardware Description Language)

Limbajele care descriu sistemele electronice digitale poarta denumirea de limbaje de descriere hardware - hardware description language, in acest moment existind ca standard IEEE doua dintre acestea: VHDL si Verilog.

VHDL este un limbaj de programare de nivel inalt orientat obiect care permite descrierea, modelarea circuitelor electronice si nu numai.

Una din deosebirile fundamentale intre VHDL ca limbaj de descriere a hardware-ului si limbajele de programare clasice(Pascal, C, C++) consta in semnificatia codului scris.

Codul VHDL reprezinta descrierea (comportamentala, structurala, mixta) a unui sistem sau dispozitiv fizic. Din acest motiv se recomanda o permanenta apreciere cantitativa si calitativa a codului scris pentru a obtine o modelare cit mai precisa a sistemului propus.

Utilizatorul creeaza unitati de proiectare (numite in continuare design-uri), care au ca punct de plecare fisiere sursa (cu extensia *.vhd sau *.hdl).

Structura de date utilizata de un sistem VHDL este diferita de cea folosita de un sistem de operare si este orientata spre conceptul de baza de date. Astfel, pe linga notiunea de director, apare si notiunea de biblioteca.

Bibliotecile contin rezultatul compilarii fisierelor sursa. Simulatorul VHDL foloseste rezultatele compilatorului VHDL.

La laborator va fi folosit programul Modelsim al firmei Mentor Graphics, in varianta 5.2d. In prezent, dezvoltarea acestui program a continuat pina la versiunea 5.6 .

Simulatorul dezvoltat de Mentor Graphics suporta standardul VHDL-IEEE1076 actualizat in 1993, precum si standardul Verilog-IEEE 1364-1995, putind fi astfel folosit pentru lucrul cu ambele limbaje de descriere hardware.

Pentru o buna desfasurare a orelor de laborator se recomanda respectarea cu strictete a regulilor expuse mai jos!

Retineti ca directorul in care este instalat sistemul VHDL nu trebuie modificat sub nici un motiv. Poate fi modificat doar directorul dumneavoastra de lucru. Directorul VHDL contine, printre altele, declaratii ale tipurilor fundamentale de date, ale operatorilor si subrutinelor. Nici acestea nu vor fi modificate, ele pot fi doar citite pentru a va usura munca.

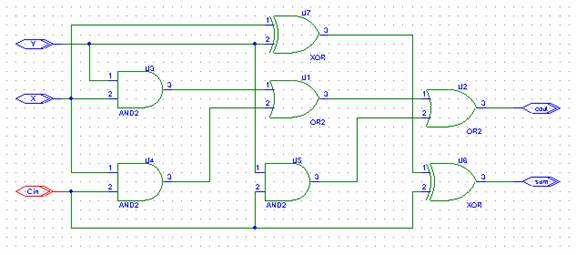

Pentru a atinge scopul declarat al lucrarii vom simula un sumator de 1 bit cu schema din figura I.1 .

Acest lucru necesita parcurgerea citorva etape intermediare:

-creerea bibliotecii work in propriul director de lucru si maparea ei cu biblioteca fizica ;

-construirea surselor in limbaj VHDL ;

-compilarea surselor ;

-simularea propriuzisa .

I.3 Despre biblioteci (libraries) in VHDL

In VHDL exista doua tipuri de biblioteci : biblioteci de lucru (working libraries) si biblioteci de resurse (resource libraries). Biblioteca de lucru este biblioteca in care sint plasate unitatile de proiectare dupa compilare. O biblioteca de resurse contine unitati de proiectare care pot fi instantiate in designul care se compileaza. La un moment dat, poate exista doar o singura biblioteca de lucru (implicit se considera biblioteca work), in schimb, pot exista un numar (finit) de biblioteci de resurse (chiar si biblioteca de lucru work ) in timpul compilarii unui design.

Biblioteca work in VHDL prezinta proprietati speciale: este predefinita in interiorul compilatorului si nu trebuie declarata explicit. De asemenea, este biblioteca utilizata de simulator in mod implicit pentru destinatia unitatilor de proiectare compilate. Implementarea bibliotecilor nu este definita in limbajul VHDL. In interiorul Modelsim bibliotecile sint implementate ca directoare si pot avea orice nume permis de sistemul de operare.

Selectam File > Change Directory din fereastra principala a programului (cea care contine prompterul Modelsim) si se selecteaza directorul de lucru .

Trebuie creeata o biblioteca noua si o mapare logica pentru aceasta. Acest lucru va conduce la crearea unui subdirector numit work(numele bibliotecii de lucru) in directorul de lucru selectat mai sus.

In fereastra principala se introduc comenzile:

vlib work

vmap work work

Comenzile pentru lucrul cu biblioteci sint urmatoarele :

-vlib -creeaza o biblioteca ;

-vdel -sterge o unitate de proiectare din biblioteca specificata ;

-vdir -listeaza selectiv continutul unei biblioteci

-vmap -defineste maparea (legatura) dintre numele logic al unei biblioteci si numele fizic (director) al acesteia, modificind astfel fisierul modelsim.ini, de initializare, al sistemului VHDL .

Prima etapa a luat sfirsit. Urmeaza editarea sursei si compilarea acesteia.

I.5 Editarea si compilarea fisierului VHDL

Editarea sursei se face activind meniul View > Source din fereastra principala. In VHDL nu exista nici o deosebire intre literele mari si mici. Fisierul va fi salvat sub denumirea Full_adder.vhd. Numele fisierului nu influenteaza denumirea designului care e proprie limbajului VHDL.

Pentru a compila un design se apasa pe butonul Compile(primul din stinga sus) din fereastra principala si se selecteaza fisierul dorit.

In fereastra principala trebuie sa urmarim daca compilarea a avut succes sau nu.

Se va acorda o atentie deosebita mesajelor de eroare care pot apare precum si mesajelor de avertizare (warninguri).

Mesajele de avertizare au un rol deosebit, ele au rolul de a atentiona pe proiectant in privinta neindeplinirii citorva conditii substantiale de catre codul VHDL compilat.

De exemplu, unul dintre acestea este cel cu privire la neincluderea in lista de sensitivitati a procesului a unui semnal care este citit in interiorul sau.

Remedierea avertismentului nu se face in mod automat prin includerea semnalului respectiv in lista deoarece este posibil ca acel proces sa nu trebuiasca sa fie sensitiv la toate semnalele care sint citite in interior.

Mesajele de confirmare a compilarii designului in biblioteca work sint:

vcom -work work

# Model Technology ModelSim EE vcom 5.2d Compiler 1999.01 Jan 15 1999

# -- Loading package standard

# -- Loading package std_logic_1164

# -- Compiling entity fulladder

# -- Compiling architecture ecuatii of fulladder

Daca la compilare nu apar erori si au fost rezolvate problemele legate de mesajele avertisment se poate trece la simulare.

I.6 Simularea unui design VHDL

Acest lucru se face activind File > Load New Design din fereastra principala. Se poate observa ca se incarca din biblioteca work designul VHDL, adica perechea entitate-arhitectura asociata fisierelor compilate in biblioteca work.

Numele arhitecturii asociate entitatii poate fi aflat actionind cu un click pe semnul plus asociat entitatii. Se selecteaza caseta Add dupa ce s-a selectat numele arhitecturii si se apasa Load. Urmarim din nou fereastra principala. Daca apar doar mesajele de incarcare atunci inseamna ca simularea a avut succes.

Dar, atentie, acest lucru nu inseamna automat ca am descris corect dispozitivul propus, ci doar ca nu avem erori de limbaj VHDL! Pot exista la acest nivel doar greseli de conceptie care ne apartin in totalitate!

Mesajele de confirmare a incarcarii (simularii) designului din biblioteca work sint:

vsim work.fulladder(ecuatii)

# vsim work.fulladder(ecuatii)

# Loading C:/MODELSIM/WIN32/../std.standard

# Loading C:/MODELSIM/WIN32/../ieee.std_logic_1164(body)

# Loading work.fulladder(ecuatii)

In figura I.1 este prezentata structura interna a sumatorului pe un bit:

Fig.I.1 Sumator pe un bit

Mai jos se prezinta tabela de adevar a sumatorului. Primele trei coloane reprezinta intrarile in sumator :cele doua intrari de sumat X, respectiv Y, si intrarea de transport Cin.

Urmatoarele doua coloane prezinta iesirile: Sum, care reprezinta rezultatul sumarii de un bit a lui X cu Y si Cout transportul rezultat din adunare.

|

X |

Y |

Cin |

Cout |

Sum |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

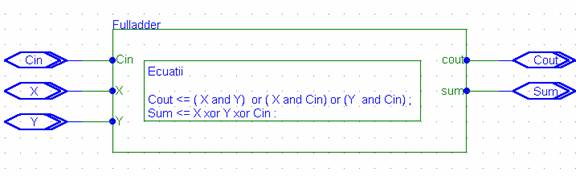

O reprezentare grafica a modelului descris de entitatea 'FullAdder' si de arhitectura 'Ecuatii' este prezentata in figura I.2.

Fig. I.2

Se observa ca semnalul Sum este o functie impara a intrarilor. Cind pe intrari exista un numar impar de biti '1' ( in coloanele 2, 3,5 si 8) Sum are valoarea '1', iar cind pe intrari exista un numar par de biti '1' Sum are valoarea '0' .

Celalalt semnal de iesire Cout are valoarea '1' numai cind exista macar doua valori de '1' pe intrari.

Declaratia de entitate pentru sumatorul de un bit este:

( fisier Full_adder.vhd)

library IEEE;

use IEEE.std_logic_1164.all;

3 entity FullAdder is

4 port ( X,Y : in Bit;

5 Cin: in Bit;

6 Cout: out Bit;

7 Sum: out Bit);

8 end FullAdder ;

12 architecture Ecuatii of FullAdder is

13 begin

Sum<= X xor Y xor Cin;

15 Cout<= (X and Y) or (X and Cin) or (Y and Cin);

16 end;

In VHDL orice componenta hardware (poate fi o poarta logica sau microprocesor) este alcatuita din doua parti: declaratia de entitate (entity interface), care defineste interfata modelului cu exteriorul si corpul arhitecturii (architecture body) care defineste implementarea, descrierea comportamentului sau a structurii modelului.

Declaratia de entitate, cuprinsa intre liniile 3 si 8, incepe cu cuvintul cheie entity urmat de numele entitatii "FullAdder".

Entitatea poate fi vazuta ca o cutie neagra deoarece contine doar porturile ce o interconecteaza cu circuitele cu care interactioneaza in sistem.

Pentru un port se specifica modul adica sensul de curgere a informatiei si tipul de date ce poate fi manipulat de portul respectiv.

Cuvintele cheie in VHDL sint elemente structurale ale acestuia si nu pot fi folosite in alte scopuri.

Declaratia de entita se incheie cu cuvintul rezervat end urmat de numele entitatii .

Intre cuvintele rezervate is si end se afla lista de porturi a entitatii, care contine semnalele de interfata cu care modelul poate comunica cu mediul exterior.

Lista este alcatuita din declaratii de semnale de interfata separate de punct si virgula.

Fiecare declaratie de semnal de interfata declara unul sau mai multe porturi de interfata.

Sint precizate numele semnalelor ( "X", "Y", "Cout"), apoi modul, aici de intrare ("in") sau iesire ("out") si in final un tip. Tipul "bit" este predifinit in VHDL si contine valorile "0" sau "1".

Modul indica directia schimbului de date cu exteriorul .

Astfel semnalele "X", "Y" ,"Cin" pot fi citite ( se vor regasi in partea dreapta a instructiunii de atribuire pentru semnale). dar nu pot fi modificate in interiorul arhitecturilor entitatii. La citire ele trec informatia in interiorul modelului.

Semnalele "Sum" si "Cout" pot fi modificate in interiorul arhitecturii entitatii. La scriere ele trec informatia in exteriorul modelului.

Corpul arhitecturii, descris intre liniile 12-16, contine doua specificatii de atribuire de semnale (liniile 14 si 15) care definesc valoarea semnalelor "Sum" si "Cout" in functie de semnalele de intrare.Valoarea semnalului "Sum" este data de operatorul SAU-EXCLUSIV aplicat celor trei semnale de intrare, obtinind astfel functia impara a semnalelor de intrare.

Aceasta modalitate de obtinere a semnalelor este denumita descriere sub forma de ecuatii a semnalelor deoarece iesirile modelului sint definite ca ecuatii ale semnalelor de intrare.

O caracteristica fundamentala a arhitecturii este data de executarea specificatiilor din corpul sau in paralel (corpul arhitecturii e mediu concurential). Astfel, ordinea specificatiilor nu influenteaza comportamentul modelului.

Pentru a da valori semnalelor de intrare se poate folosi comanda force :

force X valoare1 timp1, valoare2 timp2,. valoaren timpn

force Y valoare1 timp1, valoare2 timp2,. valoaren timpn

force Cin valoare1 timp1, valoare2 timp2, valoaren timpn

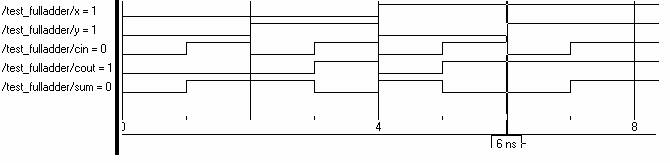

Introduceti in fereastra principala prin comanda force perechile (valoare, timp) pentru porturile de intrare X, Y, Cin asa cum sint prezentate in formele de unda din figura I.3 .

I.7 Testarea unui design VHDL

Odata descris modelul VHDL pentru sumatorul complet apare necesitatea construirii unui circuit de test pentru verificarea functionarii sale.

Pentru a putea incarca programul de test trebuie incheiata simularea sumatorului. Pentru aceasta se selecteaza File > End Simulation din fereastra principala si se confirma mesajul de parasire a simularii. Se editeaza, compileaza si se incarca designul pentru testul sumatorului intocmai ca in pasii aratati anterior.

Circuitul de test este descris mai jos in fisierul Test_Fulladder.vhd:

library IEEE;

use IEEE.std_logic_1164.all;

21 entity Test_FullAdder is end;

25 architecture Driver of Test_FullAdder is

27 component FullAdder

28 port (X,Y: in Bit;

29 Cin: in Bit;

30 Cout: out Bit;

31 Sum: out Bit ) ;

32 end component;

34 signal X,Y,Cin,Cout,Sum:Bit;

36 begin

38 UUT: FullAdder port map (X,Y,Cin,Cout,Sum);

40 Stimulus:

41 process

42 type Entry is record

43 X,Y,Cin : Bit;

44 Cout ,Sum: Bit;

45 end record;

46 type Table is array ( 0 to 7) of Entry;

47 constant TruthTable: Table :=

48 (

-------- ----- ------ -X----Y-Cin-Cout-Sum

('0' ,'0', '0', '0', '0'),

('0', '0', '1', '0', '1' ),

('0', '1', '0', '0', '1' ),

('0', '1', '1', '1', '0' ),

('1', '0', '0', '0', '1' ),

('1', '0', '1', '1', '0' ),

('1', '1', '0', '1', '0' ),

('1', '1', '1', '1', '1' )

57 );

58 begin

59 for i in TruthTable'range loop

60 X <= TruthTable(i).X;

61 Y <= TruthTable(i).Y;

62 Cin <= TruthTable(i).Cin;

63 wait for 1 ns;

64 assert

65 Cout = TruthTable(i) .Cout and

66 Sum = TruthTable(i) .Sum;

67 end loop;

68 wait;

69 end process ;

71 end;

Declaratia de entitate nu contine porturi pentru ca nu interactioneaza cu exteriorul.

Declaratia trebuie furnizata chiar atunci cind descrie un circuit de test autoconsistent.

Corpul arhitecturii ( liniile 25-71) este alcatuit din unitatea supusa testului ( linia 38) si tester ( liniile 40-69). Unitatea supusa testului este modelata ca o instantiere de componenta.

O componenta "FullAdder" a carei interfata corespunde cu cea a modelului, este instantiata si conectata la tester. Componenta este declarata la liniile 27-32, semnalele interne prin care instanta este conectata sint declarate la linia 34. Sintaxa "Port map" conecteaza porturile componentei la semnalele interne.

Circuitul de test este modelat cu ajutorul constructiei process. Procesul contine declaratia unui tablou ( liniile 47-57) care descrie stimulii (semnalele de test ) si semnalele raspuns. Tipul tabloului este descris ca un tablou de intrari la linia 46, intrarile fiind descrise ca tip bit ( liniile 43-45)

Circuitul de test aplica stimulii si verifica semnalele raspuns in sectiunea cu instructiuni secventiale a procesului ( 59-68). Instructiunile secventiale ale procesului sint executate una dupa alta, in ordinea aparitiei lor. Bucla for (liniile 59-67) aplica succesiv fiecare linie a tabelului semnalelor de intrare si verifica semnalele de iesire.

Instructiunile de atribuire de semnale (liniile 60-62) aplica intrarea curenta semnalului intern corespunzator, care la rindul sau este conectat la intrarea corespunzatoare unitatii supusa testarii.

Specificatia wait (linia 63) suspenda o nanosecunda din timpul simulat, dind astfel timp sumatorului pentru calculul valorilor semnalelor de iesire.

Specificatia assert verifica indeplinirea conditiei ce urmeaza cuvintului rezervat assert , in acest caz semnalele de iesire curente sint comparate cu raspunsurile asteptate.

Dupa epuizarea domeniului tabloului bucla for isi incheie executia iar instructiunea wait (linia 68) este executata. Executia procesului este astfel suspendata . Deoarece wait nu contine nici o clauza de timp procesul este suspendat.

Rezultatele simularii entitatii Test_FullAdder cu arhitectura Driver sint prezentate in figura I.3:

Fig.I.3

I.8 Sarcini de indeplinit la laborator

Editati in fereastra Source a programului Modelsim fisierele pentru sumatorul de un bit si pentru circuitul de test. Salvati fisierele in directorul dumneavoastra de lucru.

Compilati cele doua surse in ordinea prezentata in lucrarea de laborator utilizind butonul Compile.

Incarcati cele doua designuri in aceeasi ordine, activind meniul File > Load New Design.

Vizualizati toate ferestrele programului Modelsim activind meniul View > All .

Urmariti formele de unda in fereastra Wave si comentati semnificatia lor.Coincid cu cele ce ati invatat la cursul de Circuite Digitale?

6. Inversati ordinea celor doua atribuiri de semnale in arhitectura 'Ecuatii' a sumatorului. Ce observati? Se modifica sau nu functionalitatea sumatorului?

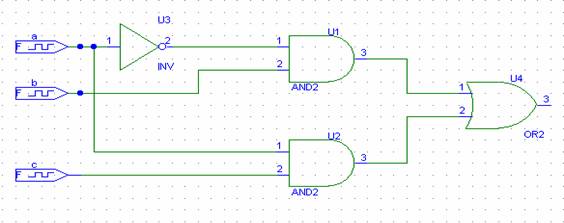

7. Scrieti tabelul de adevar si arhitectura cu ecuatii a circuitului din figura I.4. Ce functie logica indeplineste el?

Fig.I.4

Bibliografie:

1.Popescu, Gabriel Stefan - 'Proiectare asistata de calculator a circuitelor electronice:Spice - VHDL' Partea II VHDL, Editura Matrix Rom1999.

2.Toacse, Gh.; Nicula D. - 'Electronica digitala', Editura Teora 1996.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2300

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved