| CATEGORII DOCUMENTE |

Descrierea structurala

Se prezinta elemente legate de descrierea structurala a sistemului. Se defineste notiunea de componenta, indicandu-se cum anume se poate utiliza o anumita entitate compilata, in cadrul altei entitati din aceeasi librarie. Se va exemplifica pe un sumator fara semn.

In arhitectura entitatii de top, componenta se declara odata cu semnalele:

architecture behave of <nume_entitate> is

component <nume_componenta> is

generic(<lista parametri>);

port(<lista porturi>);

end component;

signal <lista semnale>

begin

Declararea entitatii folosite drept componenta este similara declararii de entitate.

Cuvantul cheie is apare numai in sintaxa VHDL 1993. In versiunea noua de limbaj, el dispare.

Componentele se instantiaza in corpul arhitecturii. In acest punct se efectueaza "conectarea" porturilor entitatii folosite la firele din interiorul entitatii ce se proiecteaza.

<eticheta> : <nume_componenta>

generic map( <parametrul1> => <valoare1>,

![]()

)

port map(

<portul 1> => <semnalul 1>,

![]()

);

Valorile atribuite genericelor si porturilor sunt separate prin virgula.

Intre atribuirea genericelor si a porturilor nu se pune vreun separator.

Intotdeauna trebuie avut grija la atribuire ca cele doua semnale sa fie de acelasi tip.

<eticheta> reprezinta numele componentei in cadrul entitatii folosite. Ea va fi astfel folosita de simulare si de tool-ul de sinteza.

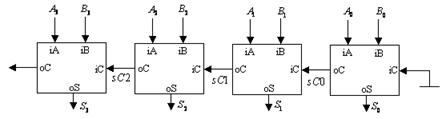

Ca la orice adunare in baza 10, si in baza 2, operanzii intregi pozitivi se aduna bit cu bit, incepand de la cel mai putin semnificativ si terminand cu cel mai semnificativ.

Prin urmare, sumatorul pe 4 biti se bazeaza pe mai multe sumatoare de cate un bit, interconectate. Interconectarea se datoreaza faptului ca la adunarea de un bit, poate aparea "transportul" unui bit la bitul imediat superior.

Sumatorul este in esenta un circuit combinational, de aceea el nu va fi prevazut cu semnal de ceas sau de reset. La cresterea numarului de biti, adancimea circuitului se va observa ca se mareste, fapt ce va duce la cresterea timpului de prelucrare prin logica combinationala si deci la diminuarea vitezei de functionare a circuitului.

Fig. 2. . Schema unui sumator complet pe 4 biti, folosind sumatoare de un bit

In aceste conditii, sumatorul de un bit are urmatoarea tabela de adevar:

|

iC |

iA |

iB |

oC |

oS |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Relatiile de sinteza sunt

![]()

![]()

Codul VHDL pentru sumatorul de un bit este:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity sum1 is

generic (

N : natural );

port(

iA,iB,iC : in std_logic;

----- ----- --------- ----- ------

oC,oS : out std_logic

);

end sum1;

architecture behave of sum1 is

begin

--proces senzitiv la intrari

process(iA,iB,iC)

begin

oS <= iA xor iB xor iC;

oC <= ((not iC) and iB and iA) or

((not iB) and iA and iC) or

((not iA) and iB and iC) or

(iA and iB and iC) ;

end process;

end ;

Acesta se va compila inainte de a se integra in sumatorul pe 4 biti.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity sum4 is

generic (

N : natural );

port(

iA,iB : in std_logic_vector(3 downto 0);

----- ----- --------- ----- ------

oS : out std_logic_vector(3 downto 0);

oC : out std_logic

);

end sum4;

architecture behave of sum4 is

--declararea componentei

--sumator pe un bit

component sum1 is

port(

iA,iB,iC : in std_logic;

----- ----- --------- ----- ------

oC,oS : out std_logic

);

end component;

--semnalele de carry intermediare

signal sC0,sC1,sC2 : std_logic;

signal sGND : std_logic := '0';--GROUND

begin

--sumatoarele de un bit instantiate

SUM_0 : sum1

port map(

iA => iA(0),

iB => iB(0),

iC => sGND,

oS => oS(0),

oC => sC0

SUM_1 : sum1

port map(

iA => iA(1),

iB => iB(1),

iC => sC0,

oS => oS(1),

oC => sC1

SUM_2 : sum1

port map(

iA => iA(2),

iB => iB(2),

iC => sC1,

oS => oS(2),

oC => sC2

SUM_3 : sum1

port map(

iA => iA(3),

iB => iB(3),

iC => sC2,

oS => oS(3),

oC => oC

end ;

Se observa ca sumatorul de un bit se instantiaza de patru ori, cu patru nume diferite, respectand indicatia din Fig. 2.1.

Totusi, daca numarul de biti este prea mare sau daca el este chiar necunoscut (parametrizabil printr-un generic), instantierea componentei devine greoaie sau imposibila. Se poate instantia un set de sumatoare intr-o bucla (pana la numarul necesar dorit), folosind instructiunea generate.

Partea de instantiere se modifica astfel:

G: for i in 0 to N-1 generate

SUM : sum1

port map(

iA => iA(i),

iB => iB(i),

iC => sCARRY(i),

oS => oS(i),

oC => sCARRY(i+1)

end generate;

sCARRY(0) <= '0';

oC <= sCARRY(N);

unde N este presupus ca fiind generic (4 in cazul nostru), iar sCARRY este un vector de biti de lungime N+1 care preia semnalele de transport din noduri. Primul nod este legat la masa (si ii este atribuita valoarea '0' in afara buclei de generare), iar ultimul este legat chiar la transportul de iesire.

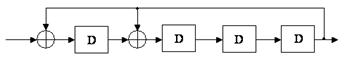

Fig. 2. . Registru de deplasare cu reactie

Sa se implementeze acest circuit particular:

in descriere comportamentala;

in descriere structurala, folosind pentru bistabile entitatile deja compilate din lucrarea anterioara.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1938

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved