| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

Etapele descarcarii codului pe placa

Simularea

In aceasta etapa se presupune ca programul .vhd a fost editat si testat prin simulare cu ajutorul ModelSim-ului.

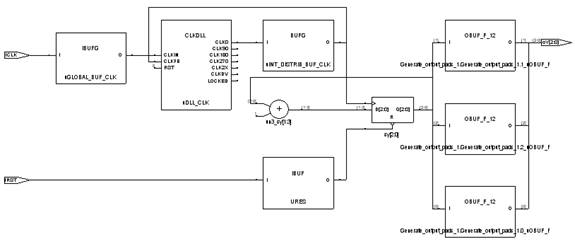

Inainte de sinteza si implementare, entitatea trebuie integrata in ceea ce se numeste o entitate de top, in care se realizeaza efectiv interfata cu pinii chipului. Un astfel de exemplu este prezentat mai jos, pentru un numarator pe 3 biti.

Fig. . Integrarea numaratorului in entitatea de top

In schema, numaratorul este format din sumator si din registrul pe 3 biti. Se observa din figura ca, pe langa aceste componente mai apar si alte componente noi necesare indiferent de aplicatia sau de entitatea ce se doresc implementate. Acestea sunt:

IBUF: buffer de intrare. Acest buffer se insereaza pe orice port de intrare in entitate, asa cum este cazul semnalului de RESET al numaratorului. Daca entitatea are mai multe intrari sau intrari pe mai multi biti (vector de biti), pe fiecare din acesti biti se va pune buffer de intrare.

OBUF_F_12: buffere de iesire. Joaca acelasi rol ca si bufferele de intrare cu diferenta ca se pun pe fiecare bit al iesirilor din entitate (in acest caz pe cei trei biti de iesire ai numaratorului). Rolul acestor buffere este de a regenera frontul datelor, deci de a micsora timpii de tranzitie intre fronturi.

IBUFG, CLK_DLL si BUFG se folosesc pentru regenerarea ceasului (bufferare). CLKDLL si BUFG formeaza o bucla de reactie cu scopul sincronizarii digitale prin calare de faza.

Componentele de mai sus sunt existente intr-o librarie speciala .vhd a Xilinx, UniSIM, ce trebuie compilata inainte de utilizare.

Sinteza

Aici este primul punct in care trebuie sa indicati tipul cipului pentru care doriti sa generati fisierul ce urmeaza a fi descarcat pe placa. In continuare vom prezenta pas cu pas procedura de sinteza pentru doua tool-uri diferite: Synplify 7.0 si Xilinx XST. Sinteza cu Synplify va fi folosita doar pentru vizualizarea schemelor RTL si pentru obtinerea unor repere orientative legate de aria ocupata si de frecventa maxima de lucru. Sinteza cu Xilinx XST va fi folosita efectiv ca etapa intermediara a procesului de descarcare a codului pe placa.

Sinteza cu Synplify

Se deschide Synplify

File/ New Project

Click dreapta pe numele proiectului/ New Implementation

Din fereastra aparuta setati pe Device:

o Technology => Xilinx Spartan2

o Part => XC2S50

o Speed => -6

o Package => TQ144

Din fereastra aparuta setati pe Options/Constrains:

o Frequency MHz) => 100

Se inchide fereastra de New Implementation cu OK

Project/ Add Source File (sau din stanga ferestrei folosind butonul Add File)

Din fereastra aparuta mergeti in directorul unde aveti sursele pe care vreti sa le sintetizati. Trebuie sa includeti toate sursele instantiate in entitatea de top, precum si sursele instantiate in sursele instantiate in entitatea de top, etc. Sursa care contine entitatea de top va fi pozitionata ultima in lista de surse din proiect. Acest lucru se poate face selectand cu click stanga sursa si tragand-o in jos, iar in locul dorit se elibereaza click-ul.

Se apasa butonul RUN

Daca sunt raportate erori se apasa butonul View Log si se determina erorile aparute. Dupa inlaturarea lor se apasa RUN.

Daca sinteza s-a realizat cu success, in afara de informatiile de arie si frecventa obtinute prin apasarea butonului View Log, mai dispunem si de schemele RTL si Tehnologica ale codului sintetizat. Acestea se deschid: HDL Analyst/RTL/Hierarchical View sau HDL Analyst/Technology/ Hierarchical View. De asemenea exista si in bara de comanda butoane pentru deschiderea acestor scheme.

Daca ar urma sa facem implementarea din acest punct, in Xilinx s-ar crea un proiect care sa accepte ca surse de intrare fisiere cu extensia .edif (generate de Synplify). Deoarece am spus insa ca implementarea de va face in totalitate cu Xilinx, trecem la punctul urmator.

Sinteza cu Xilinx XST

Acest proces reprezinta o etapa din procesul complet al implementarii. Aici vom descrie pasii necesari pentru sinteza, urmand ca la implementare sa continuam din punctul in care ne-am oprit aici.

Deschidem Xilinx ISE

File/ New Project

Se seteaza in campul Project location calea unde vrem sa generam proiectul; Se seteaza in campul Project name numele proiectului; Se seteaza in campurile Property name:

o Device family => Spartan2

o Device => XC2S50

o Package => TQ144

o Speed grade => -6

o Design flow => XST VHDL

In fereastra Sources in Project vor aparea 2 linii: una pe care scrie Spartan, iar cealalta pe care scrie xc2s50-6tq144-XST VHDL. Cu click dreapta pe cea de-a doua linie si selectare Add Source se pot adauga fisierele dorite pentru sinteza. Ele se vor aseza automat in ordinea ierarhica in care au fost instantiate. In plus se adauga si fisierul .ucf care contine constrangerile de timp ale programatorului si rutarea semnalelor de intrare si iesire ale entitatii de top pe pinii cipului.

Se da click stanga pe fisierul de top si in acel moment in fereastra Processes for Current Source apar urmatoarele linii:

o Design Entry Utilities

o User Constrains

o Synthesize

o Implement Design

o Generating Programming File

Click dreapta pe Synthesize si se alege Properties. In fereastra aparuta pe butonul Synthesis Options se seteaza:

o Optimization Goal/ Speed sau Area

o Optimization Effort/Normal sau High

Click dreapta pe Synthesize si Run.

Implementarea

Se continua procesul descris in sucapitolul A.2 dupa ce sinteza s-a incheiat .

Se detaliaza Implement Design (prin apasarea plusului de langa el).

Apar: Translate, Map, Place and Route

Click dreapta pe Place and Route si se alege Properties:

o Place & Route Effort Level => Lowest sau Low sau Normal sau High sau Higher

o Se selecteaza Generate Post-Place&Route Static Timing report

o Se selecteaza Generate Post-Place&Route Simulation Model (genereaza fisierele .vhd si .sdf care vor putea fi simulate cu ModelSim)

Click dreapta pe Implement Design/Run

Click dreapta pe Generating Programming File/ Properties:

o Se selecteaza Create Bit File

Click dreapta pe Generatin Programming File/ Run

In acest moment procesul de implementare s-a incheiat.

Observatii

Dupa implementare se poate deschide Place and Route (apasand plusul de langa el) si se pot selecta urmatoarele optiuni:

Dublu click stanga pe Place&Route Report deschide raportul de place and route. Acesta contine informatii despre routarea catre pini, despre aria ocupata (detaliat pe luturi, bistabili, tri-state, memorii, etc) si despre frecventa de lucru.

Deschidem Generate Post-Place&Route Static Timing si dam dublu click stanga pe Post-Place&Route Static Timing Report. Acesta contine informatii despre intarzierile prin logica si prin rute. In acelasi timp indica punctele in care constrangerile de timp ale utilizatorului (specificate in .ucf) nu au fost indeplinite (daca este cazul).

Dublu click stanga pe View/Edit Routed Design(FPGA Editor). Se va deschide FPGA Editor care va arata modul concret in care au fost ocupate componentele de pe placa si cum s-a realizat rutarea semnalelor.

Pregatirea fisierelor pentru descarcarea pe placa

Se deschide Start/Programs/Xilinx ISE 5/Accessories/iMPACT

La intrebarea What do you want to do first? se selecteaza Prepare configurations Files. Se apasa Next.

La pasul I want to create a: se selecteaza PROM File. Se apasa Next.

La pasul I want to target a: se selecteaza Parallel PROM, iar pentru PROM File Format se allege .mcs. Se mai indica numele fisierului si calea unde el va fi format. Se apasa Next.

La pasul Select a Parallel PROM Density se seteaza 32M si se apasa butonul Add o data. Se apasa Next.

Urmatoarea fereastra recapituleaza setarile utilizatorului. Se apasa Next daca totul este OK. Daca nu se poate reveni la setarile anterioare prin Back.

Daca s-a mers inainte se apasa Add File, de unde se selecteaza fisierul .bit generat la implementare (acesta se gaseste chiar in directorul in care s-a facut implementarea). Urmeaza o serie de intrebari la care se raspunde astfel:

o Would you like to add another design file to Data Stream 0? apasati No.

o Se apasa Finish in noua fereastra aparuta

o La intrebarea Do you want to generate file now? raspundeti Yes.

o La intrebarea Do you want to change the file name? raspundeti No.

Dupa parcurgerea acestor pasi aveti fisierul .mcs care se va descarca in FLASH-ul FPGA-ului.

Fisiere.

5.1. Fisierul .vhd al contorului pe 3 biti in entitatea de top.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

--library unisim;

--use unisim.all;

entity counter is

generic

Nb : natural :=3 );

port(

iRST : in std_logic;

iCLK : in std_logic;

oY : out std_logic_vector(Nb-1 downto 0)

end counter;

architecture behave of counter is

------XILINX COMPONENTS----

component CLKDLL

port(

CLK0: out std_logic;

CLK90: out std_logic;

CLK180: out std_logic;

CLK270: out std_logic;

CLK2X: out std_logic;

CLKDV: out std_logic;

LOCKED: out std_logic;

CLKIN: in std_logic;

CLKFB: in std_logic;

RST: in std_logic

end component;

component IBUF

port(

O: out std_logic;

I: in std_logic

end component;

component IBUFG

port(

O: out std_logic;

I: in std_logic

end component;

component BUFG

port(

O: out std_logic;

I: in std_logic

end component;

component OBUF_F_12

port(

O: out std_logic;

I: in std_logic

end component;

------XILINX COMPONENTS----

signal sy : std_logic_vector(Nb-1 downto 0);

signal CLK_BUF,CLK_int,CLK_int_buf : std_logic;

signal sRST : std_logic;

signal gnd : std_logic;

begin

gnd <= '0';

process(CLK_int_BUF, sRST)

begin

if sRST = '0' then

sY <= (others => '0');

elsif rising_edge(CLK_int_BUF) then

sy <= sy + '1';

end if;

end process;

uGLOBAL_BUF_CLK: IBUFG

port map(

O => CLK_buf,

I => iCLK

uDLL_CLK: CLKDLL

port map(

CLK0 => CLK_int,

CLK90 => open,

CLK180 => open,

CLK270 => open,

CLK2X => open,

CLKDV => open,

LOCKED => open,

CLKIN => CLK_buf,

CLKFB => CLK_int_buf,

RST => gnd

uINT_DISTRIB_BUF_CLK: BUFG

port map(

O => CLK_int_buf,

I => CLK_int

URES : IBUF

port map(

O=>sRST,

I=>iRST

Generate_output_pads_1:

for i in 0 to 2 generate

uOBUF_F_12: OBUF_F_12

port map(

O => oY(i),

I => sY(i)

end generate;

end

5.2. Exemplu de fisier .ucf. Presupunem ca entitatea noastra este un contor pe 3 biti care are ca intrari iCLK si iRST si ca iesire oY (3 biti).

CONFIG PART = XC2S50-tq144-6 ;

TIMESPEC TS_PADS_TO_REGS = FROM:PADS:TO:FFS:10.000000;

TIMESPEC TS_REGS_TO_REGS = FROM:FFS:TO:FFS:10.000000;

TIMESPEC TS_REGS_TO_PADS = FROM:FFS:TO:PADS:10.000000;

NET 'oY<2>' LOC = 'P86';

NET 'oY<1>' LOC = 'P84';

NET 'oY<0>' LOC = 'P83';

NET 'iCLK' LOC = 'P88';

NET 'iRST' LOC = 'P93

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1408

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2026 . All rights reserved