| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

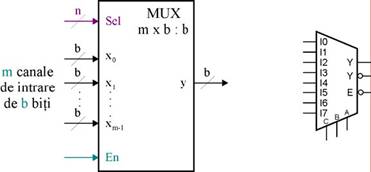

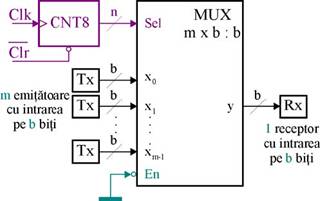

Functie. Permite transmiterea succesiva a datelor de la m surse de date la un receptor unic.

In cazul general, un MUX este prevazut cu:

m canale de date de intrare de cate b biti;

un canal iesire pe b biti;

un cod de selectie a canalului de intrare cu n biti unde n = log2 m;

o intrare de validare a functionarii.

Figura 3.24. Schema functionala a unui multiplexor si simbolul unui MUX 8:1.

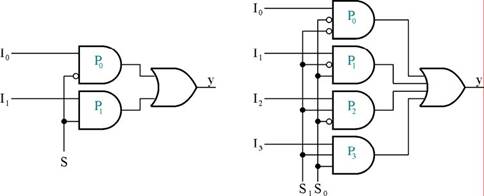

Cel mai simplu MUX are 2 intrari si o iesire (figura 3.25.a). Un MUX 4:1 necesita 4 porti SI-NU, o poarta SAU si minim 3 inversoare (figura 3.25.b).

a. b.

Figura 3.25. MUX simple - schema electrica,

a - MUX 2:1, b - MUX 4:1.

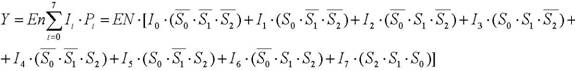

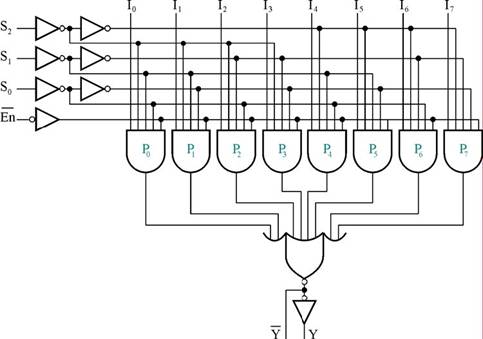

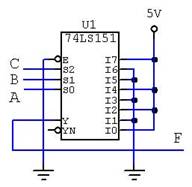

74LS151 (figura 3.23):

Este un multiplexor cu m = 8 canale de intrare, n = log2 m = 3 linii de selectie si un canal de iesire de b = 1 bit.

Ecuatia care descrie functionarea MUX 74LS151 este:

Figura 3.23. MUX 74LS151.

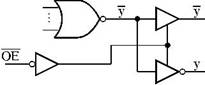

74LS251

Are o structura asemanatoare cu 74LS151 (m = 8, n = 3, b = 1), fata de care prezinta insa urmatoarele deosebiri:

iesirile Y

si ![]() sunt de tip trei stari, validate de

semnalul

sunt de tip trei stari, validate de

semnalul ![]() activ pe 0 (Output Enable), asa

cum se poate observa in figura 3.27. Nu mai exista (si nici nu mai

este necesara) intrarea

activ pe 0 (Output Enable), asa

cum se poate observa in figura 3.27. Nu mai exista (si nici nu mai

este necesara) intrarea ![]()

![]() (inlocuita cu

(inlocuita cu ![]() ). Daca

). Daca ![]() , ambele iesiri sunt in stare de

impedanta ridicata HiZ.

, ambele iesiri sunt in stare de

impedanta ridicata HiZ.

sunt circuite utilizate pentru conectare la magistrale

Figura 3.27. Iesirea multiplexorului 74LS251.

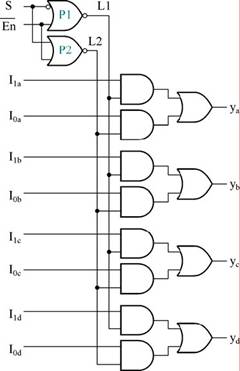

74LS157 (figura 3.28).

Este un multiplexor cvadruplu 2:1 cu intrare de validare, avand m

= 4 canale, b = 2 biti, n = 1 bit. Functionare:

Daca ![]() , liniile L1, L2

vor fi 0 logic, iar iesirile Y0,.,Y3

vor fi de asemenea 0 logic.

, liniile L1, L2

vor fi 0 logic, iar iesirile Y0,.,Y3

vor fi de asemenea 0 logic.

Daca ![]() , portile P1, P2

functioneaza pentru semnalul de selectie ca inversoare; pentru S

= 0 sunt selectate intrarile I0a, I0b,

I0c, I0d, iar pentru S = 1 sunt

selectate intrarile I1a, I1b, I1c,

I1d.

, portile P1, P2

functioneaza pentru semnalul de selectie ca inversoare; pentru S

= 0 sunt selectate intrarile I0a, I0b,

I0c, I0d, iar pentru S = 1 sunt

selectate intrarile I1a, I1b, I1c,

I1d.

Figura 3.28. Multiplexor cvadruplu 2:1 cu intrare de validare, 74LS157.

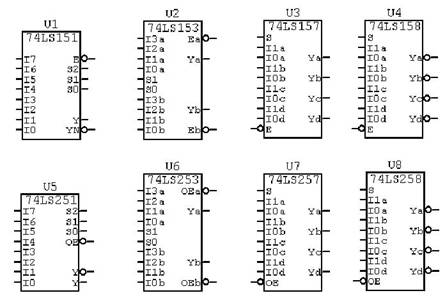

Figura 3.29. Multiplexoare in tehnologie TTL.

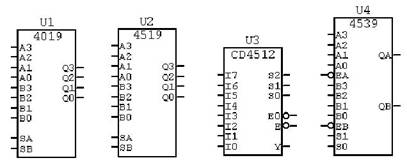

Figura 3.30. Multiplexoare in tehnologie CMOS.

Extinderea numarului de canale m, fara modificarea numarului de biti b pe canal.

Extinderea numarului de biti b, fara modificarea numarului de canale m.

Extinderea numarului de canale m si a numarului de biti b pe canal.

Transmiterea succesiva a datelor de la m surse de date la un singur receptor (aplicatia fundamentala):

Figura 3.31. Multiplexor utilizat pentru transmisia succesiva a informatiei.

CNT este un numarator binar modulo m. Cand este activata, intrarea nCLR determina stergerea numaratorului. Aplicarea unui impuls de tact Clk determina incrementarea codului de la iesirea CNT. Se selecteaza astfel succesiv cele m = 2n canale de date, iar informatia prezenta la intrare este transferata succesiv la receptorul Rx.

Conversia paralel-serie a unui cuvant binar cu m biti

Se foloseste un MUX cu m canale de cate 1 bit. De exemplu pentru conversia paralel-serie a unui cuvant binar se poate folosi MUX 74LS151. Cei 8 biti aplicati paralel la intrarile de date, apar succesiv la iesire, bit dupa bit. Dupa 8 impulsuri de tact (CK) la iesire se obtine intregul cuvant, in forma seriala.

Figura 3.32. Conversia paralel - serie cu MUX 74LS151.

Implementarea functiilor logice

Spre deosebire de decodificator care permite teoretic implementarea unui numar ori cat de mare de functii in acelasi timp, multiplexorul are o singura iesire. Acest lucru permite implementarea doar a unei singure functii logice (respectiv a valorii negate a acesteia). Se utilizeaza in acest scop multiplexoare care au b = 1. Pot fi implementate functii cu un numar de variabile egale cu numarul de biti ai codului de selectie n. Implementarea se bazeaza pe relatia care exprima variabila de iesire Y in functie de codul de selectie si datele de intrare.

Exemplul 1. Fie F =P1 + P3 + P5 + P3. Se noteaza cu A, B, C intrarile aferente variabilelor binare.

![]()

Pentru ca la iesirea Y sa se gaseasca functia F, se dau urmatoarele valori intrarilor: I1 = I3 = I5 = I3 = 1, I0 = I2 = I4 = I7 = 0

Daca se doreste utilizarea iesirii ![]() , se pun pe 0 intrarile Ii

care corespund termenilor P existenti in functie si pe 1

intrarile Ii ce corespund termenilor P care

lipsesc din functie. In exemplul de mai sus, pentru ca

, se pun pe 0 intrarile Ii

care corespund termenilor P existenti in functie si pe 1

intrarile Ii ce corespund termenilor P care

lipsesc din functie. In exemplul de mai sus, pentru ca ![]() = F se dau urmatoarele valori

intrarilor: I1 = I3 = I5

= I3 = 0, I0

= I2 = I4 = I7 = 1.

= F se dau urmatoarele valori

intrarilor: I1 = I3 = I5

= I3 = 0, I0

= I2 = I4 = I7 = 1.

Figura 3.33. Implementarea unei functii cu MUX.

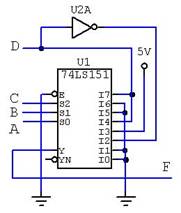

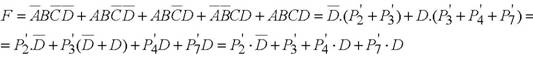

Exemplul 2. In afara de situatia descrisa anterior, este de mentionat ca este posibila implementarea unei functii de n + k variabile binare cu ajutorul unui multiplexor cu n biti ai codului de selectie, daca numarul termenilor P din functia F nu depaseste numarul canalelor de intrari m.

Pentru 74LS151: codul de selectie fiind pe 3 biti, k = 1 - ceea ce corespunde la 4 variabile de intrare, iar numarul termenilor P trebuie sa fie cel mult egal cu 8.

Figura 3.34. Implementarea unei functii cu multiplexor - varianta a II-a.

Fie F= P2 + P3 + P11 + P12 + P15. Este o functie de 4 variabile, dar implementarea se poate face cu un multiplexor avand n = 3 deoarece numarul termenilor P este mai mic decat m = 23 = 8. Se rescrie functia:

Daca se foloseste 74LS151 si iesirea Y, la intrarile de date se aplica:

I = I1

= I5 = I3

=0, I2 =![]() , I3

= 1, I4 = D, 0, D7 = D, iar

, I3

= 1, I4 = D, 0, D7 = D, iar ![]() (figura 3.34).

(figura 3.34).

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 4208

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved