| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

Numarator binar sincron reversibil

Numaratoarele binare sincrone se fabrica in general sub forma de numaratoare reversibile. Interconectarea celulelor in vederea obtinerii schemei de numarator sincron reversibil se face conform anexei 1.

Fata de schemel din fig 1.6 si 1.7 apare urmatoarea modificare : intrarile J si K ale tuturor celulelor sunt la nivel 1 iar impulsul de tact este dirijat prin intermediul unor porti spre celulele ce trebuie sa basculeze conform tabelului de functionare. Bascularea celulelor binare se produce la tranzitia 0→1 a semnalului de pe una din intrarile de tact : CU (COUNT UP) pentru numararea directa respectiv CD (COUNT DOWN) pentru numarare inversa.

Sensul de numarare este determinat de intrarea activata in timp ce cealalalta intrare este in starea 1.

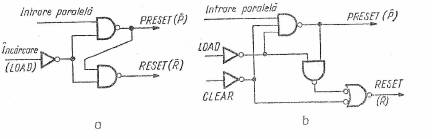

Pentru a oferi o flexibilitate maxima schemei, celulele de baza s-au ales de tipul J-K Master-Slave cu intrari prioritare de preselectie si de stergere. Folosind aceste intrari intr-o conexiune de tipul D sincrona putem realiza incarcarea paralela a celulelor numaratorului (vezi fig 1.8).

Operatia de incarcare este independenta de intrarile de tact si se realizeaza cand intrarea de incarcare (LOAD) este in 0. Circuitul mai este prevazut si cu o intrare prioritara de stergere (CLEAR), care forteaza iesirea in starea Q=0 atunci cand pe aceasta borna se aplica nivel 1.

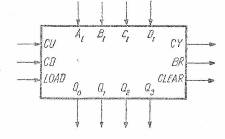

Schema bloc completa a numaratorului binar sincron reversibil este reprezentata in fig 1.9.

Fig 1.8 Schema incarcarii paralele si a stergerii.

Fig 1.9 Schema bloc a numaratorului sincron reversibil

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1963

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved