| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

Registrul SISO

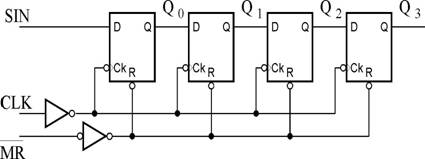

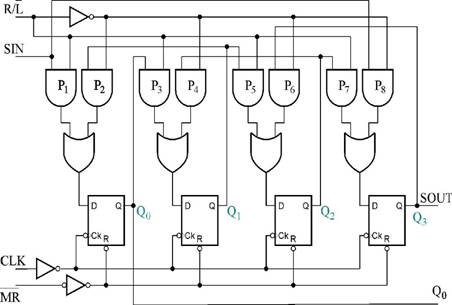

Acest tip de registru respecta structura din figura 5.2, formata din n bistabile de tip D. Intrarea D a bistabilului k + 1 este conectata la iesirea Q a bistabilului k. O intrare asincrona activa pe '0' notata nMR (Master Reset) permite stergerea simultana a tuturor bistabilelor. Deplasarea informatiei se face de la intrare notata SIN (Serial Input sau DS Data Serial) spre iesire, notata SOUT (Serial Output) sau Qn-1 daca se iau in considerare cele n bistabile D ale registrului si primul se noteaza cu 0. Deplasarea informatiei se efectueaza de la stanga la dreapta. Bistabilele D utilizate comuta pe frontul scazator al semnalului de tact si pot fi de exemplu Master Slave realizate din doua latch-uri SR.

Observatie: Daca nu s-ar folosi bistabile care comuta pe frontul scazator, ci latch-uri D cu validare, registrul nu ar functiona corect, deoarece latch-urile ar deveni transparente pe palierul semnalului de tact, iar pentru SIN = 1, la primul palier 1 logic al tactului toate iesirile Qi ar deveni 1 logic.

Descrierea functionarii registrului SISO Pentru inscrierea informatiei in registru, in general nu este necesara in general initializarea prin

![]()

MR deoarece pachetul de n biti ce va fi inscris va inlocui oricum informatia existenta anterior in

![]()

registru. Operatia de scriere propriu-zisa se face cu MR , intr-un numar de impulsuri de tact egal cu numarul de biti ai cuvantului inscris.

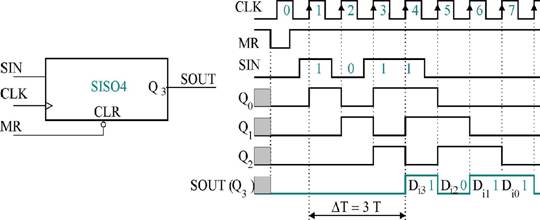

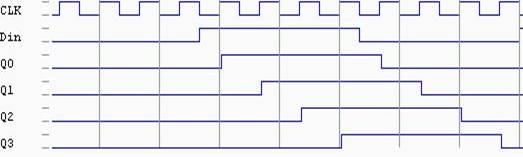

Se aplica la intrarea SIN bitii Di3, Di2, Di1 si Di0 si cele 4 impulsuri de tact corespunzatoare. Functionarea poate fi exemplificata cu ajutorul tabelului 3.1, considerand ca date de intrare Di3 = 1, Di2 = 0, Di1 =1, Di0 = 1. Simbolul circuitului si diagramele de semnal sunt prezentate in figura 3.3.

Citirea (seriala) se face folosind iesirea Qn-1 (DOUT). Registrul poate fi citit si paralel daca iesirile Q , , Qn-1 sunt accesibile la pinii circuitului integrat.

Tabelul 5.1

Inscrierea registrului SISO de 4 biti

|

Tact |

SIN |

Q |

Q |

Q |

Q |

|

nMR |

x | ||||

|

1 (Di3 | |||||

|

0 (Di2 | |||||

|

1 (Di1 | |||||

|

1 (Di0 |

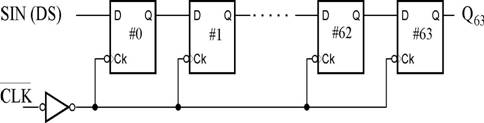

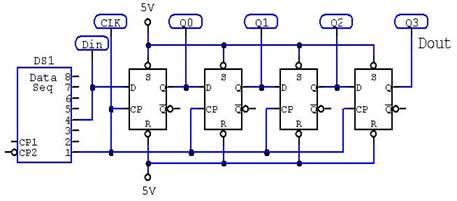

Circuitul 4731B (figura 5.4) produs de firma Fairchild contine 4 registre SISO de 64 de biti, la care sunt accesibile doar intrarea SIN si iesirea Q

Pentru registrul SISO din figura 5.5, diagramele de semnal prezinta principala aplicatie a acestui tip de registru - intarzierea informatiei cu o durata egala cu perioada a n -1 semnale de tact (figura 5.6).

Tema. In figura 5.5 desi bistabilele comuta pe frontul crescator al semnalului de tact, registrul functioneaza corect. De ce?

5.1.1. Registre bidirectionale

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1885

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved