| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

Structuri combinaTionale SSI implementate In verilog

Scopul lucrarii

Introducere in limbajul de descriere hardware Verilog HDL si folosirea simulatorului Veriwell pentru sinteza structurilor combinationale implementate cu porti logice.

2. Aparate necesare

- calculator compatibil Pentium

- sistem de operare Windows 95 sau superior

- programul VeriWell 2.0, produs de Wellspring Solutions, versiunea freeware, disponibila pe Internet

3. Consideratii teoretice

Metodele manuale de sinteza a sistemelor numerice, care presupun tehnici de minimizare a functiilor binare, utilizarea tabelelor de tranzitii etc., nu permit proiectantului conceperea unor sisteme de mare complexitate. Pentru automatizarea proiectarii au fost concepute instrumente sub forma unor limbaje de descriere a hardware-ului, numite limbaje HDL (Hardware Description Languages). Aceste limbaje permit specificarea riguroasa a functionalitatii sistemelor numerice, permit simularea acestor circuite (prin vizualizarea formelor de unda in timp se verifica daca functionarea circuitului corespunde asteptarilor noastre), precum si sinteza circuitelor, generand conexiunile necesare pentru o structura programabila, sau mastile necesare pentru constructia unui circuit integrat ASIC. Rezultatul compilarii programului nu este un cod masina, ci schema de conexiuni a unui circuit numeric.

Sursele HDL-urilor nu sunt reprezentari grafice de scheme logice, ci fisiere text, care respecta sintaxa limbajului respectiv, si care ofera, asemenea unui limbaj de nivel inalt, o descriere comportamentala a circuitelor. Este posibila si o descriere structurala, legata mai mult de schema circuitului, preferata de unii proiectanti, macar pentru unele portiuni ale sistemului numeric.

La ora actuala sunt standardizate doua limbaje HDL: Verilog HDL, usor de invatat, cu o sintaxa asemanatoare limbajului C (chiar daca mai exista si unele instructiuni care mai amintesc de Pascal), care ocupa circa jumatate din aplicatiile comerciale HDL din Statele Unite, si limbajul VHDL (Very High Speed Integrated Circuit Hardware Description Language), ceva mai dificil, cu o sintaxa bazata pe limbajul Ada, care ocupa cealalta jumatate din piata. Simulatorul de Verilog pe care il vom folosi se numeste Veriwell si poate fi descarcat gratuit din Internet. Singura limitare a acestei versiuni gratuite este limitatea surselor la circa 1000 linii de cod.

Sa consideram circuitul combinational simplu cu 3 intrari si o iesire din figura 3.1. Pentru sinteza si analiza acestui circuit trebuie sa generam doua fisiere sursa, pe care le-am numit clc1.v si test_clc1.v, iar continutul lor este reprezentat in figura 3.3. Cele doua fisiere sunt incluse intr-un proiect nou, numit clc1.prj

Fig. 3.1 Schema logica a unei structuri combinationale

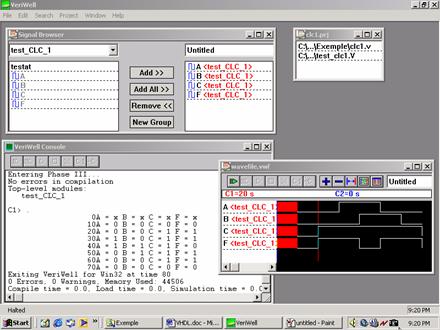

Interfata grafica a mediului VeriWell 2.0 este prezentata in figura 3.2. Primul pas consta in crearea unui proiect nou, alegand optiunea Project si apoi New Project. Am numit proiectul clc1.prj, iar fisierele componente sunt listate in fereastra din dreapta-sus: clc1.v si test_clc1.v. Orice fisier Verilog nou, adica orice fisier *.v, poate fi creat cu optiunea File si apoi New, si poate fi adaugat la proiectul curent prin optiunea Project si apoi Add file.. Comanda Run din meniul Project determina compilarea fisierelor sursa, iar rezultatul apare in ferestra de consola VeriWell Console din partea stanga-jos a ecranului. Se observa lipsa erorilor din procesul de compilare a proiectului, se raporteaza modulul ierarhic superior, in cazul nostru test_clc_1 si se listeaza nivelurile logice ale semnalelor de intrare A, B, C si de iesire F pentru 80 unitati de timp, asa cum s-a cerut in fisierul sursa test_clc1.v. Aceste semnale pot fi vizualizate in fereastra wavefile.wmf, reprezentata in partea dreapta-jos, obtinuta prin comanda Open Wave File. din meniul File. Fereastra Signal Browser din stanga-sus permite alegerea semnalelor pe care vrem sa le vizualizam.

Putem observa ca fisierul clc1.v realizeaza o descriere structurala a circuitului, iar fisierul test_clc1.v realizeaza testarea circuitului, prin aplicarea la anumite intervale de timp a unor stimuli pe intrari. Observam ca orice circuit sau sistem se defineste ca un "modul", care incepe si se termina cu cuvintele cheie module si respectiv endmodule (dupa endmodule nu se mai pune Portile logice din schema nor and not sunt predefinite in limbajul Verilog. Alte porti logice .

Fig. 3.2 Cateva ferestre din mediul VeriWell 2.0

Fig. 3.3 Fisierele sursa ale proiectului clc1.prj

predefinite sunt : nand or xor xnor si buf Observam ca fiecare poarta are un nume si o lista de intrari/iesiri. Iesirea este pusa prima in lista. Cu exceptia bufferelor, toate portile au o singura iesire. Bufferele repeta semnalul de intrare pe mai multe iesiri, de exemplu: buf BUF1 (out1, out2, out3, in); Prin input si output se declara intrarile si iesirile din blocul combinational CLC_1. Variabilele care reprezinta semnale numerice sunt de doua tipuri: wire (fir) sau reg (registru). O variabila de tip wire modeleaza un semnal combinational, iar atribuirea ei se face cu instructiunea assign, care inseamna ca la fiecare modificare de variabila se reevalueaza valoarea atribuirii si se modifica daca este cazul. O variabila de tip reg modeleaza o celula de memorie, iar atribuirea se face procedural, ca in limbajele de programare uzuale.

Daca vrem sa tinem seama si de intarzierile datorate timpilor de propagare prin porti, este suficient sa introducem la definirea portii o intarziere egala cu acest timp de propagare. De exemplu, instructiunea nor #2 p3(outF,S1,S2) introduce un timp de propagare de 2 unitati pentru poarta p3. Daca o intrare se modifica la t = 6, atunci iesirea portii se modifica la t = 8.

Pentru o descriere comportamentala a circuitului, in interiorul modulului CLC_1 se pastreaza numai declaratiile semnalelor de intrare si de iesire input si output. Restul liniilor din interiorul modulului se inlocuiesc prin instructiunea assign outF = ~((inA&inB)|~inC). Programul este scris mai usor si mai compact, pentru ca acum ne intereseaza functia si nu conexiunile interne ale circuitului.

Al doilea fisier al proiectului, test_clc1.v, genereaza semnalele de testare a circuitului. Sistemul de testare este tot un modul. Instructiunile care genereaza semnalele de test sunt cuprinse intre begin si end. Cuvantul cheie initial determina executia instructiunilor de la t = 0. Functia de sistem $monitor permite monitorizarea variabilelor. Simbolurile specifice % ne trimit la lista de variabile unde se cauta o valoare zecimala (d) sau binara (b). Monitorizarea urmareste in permanenta valoarea

Fig. 3.4 Schema logica a unui comparator de 4 biti

variabilelor, repetand instructiunea la fiecare modificare a variabilelor. Numele modulului testat, CLC_1, apare inainte de ultima comanda endmodule din fisierul test_clc1.v

Un alt exemplu de circuit combinational este comparatorul a doua numere binare de cate 4 biti, reprezentat in figura 3.4, atat sub forma de bloc logic cu functie de comparator, cat si sub forma de schema logica cu porti. Daca cele doua numere de la intrare sunt egale, atunci iesirea are valoarea logica 1, iar in caz contrar este 0. Codul sursa care descrie structural acest circuit este urmatorul:

module comp_4(out, a, b);

input[3:0] a, b; // cele doua intrari sunt vectori pe 4 biti

output out ;

wire w0, w1, w2, w3 ; // se declara conexiunile interne

xor xor_3(w3, a[3], b[3]),

xor_2(w2, a[2], b[2]),

xor_1(w1, a[1], b[1]),

xor_0(w0, a[0], b[0]),

nor nor_1(out, w0, w1, w2, w3);

endmodule

Un modul de testare pentru acest circuit este propus mai jos. El poate fi introdus in acelasi fisier, sau intr-un fisier separat, asa cum am procedat la exemplul anterior.

module test_comp;

reg[3:0] number_1, number_2; // cele doua numere de intrare

wire out_; // "firul" de conectare la "monitor"

initial begin number_1 = 4'd5; // numarul zecimal 5 scris in binar pe 4 biti

number_2 = 4'd7; // numarul zecimal 7 scris in binar pe 4 biti

#1 number_1 = 4'd7; // deci a = b la t = 1

#2 number_2 = 4'd12;

#3 number_1 = 4'd12; // din nou a = b, la t = 6

#4 number_1 = 4'd1;

end

comp_4 COMP(out_, number_1, number_2); //COMP este un circuit de tipul comp_4

initial $monitor("Time=%0d number_1=%b number_2=%d out_",

$time, number_1, number_2, COMP.out_);

endmodule

Fig. 3.5 Sumator complet pe un bit si schema interna

Sumatorul complet pe 1 bit aduna bitii de intrare a + b + carry_in si are la iesire un bit de suma sum si transportul catre rangul superior, carry_out Functionarea corecta a acestui circuit poate fi testata cu urmatorul modul de test:

module test_adder;

reg[2:0] signals; // in ordine, cei trei biti sunt (carry_in, a, b)

wire sum, carry_out; // conexiunile la "monitor"

initial begin signals = 3'b000; // se genereaza toate combinatiile posibile

#10 signals = 3'b001; // pentru cei trei biti de intrare

#10 signals = 3'b010;

#10 signals = 3'b011;

#10 signals = 3'b100;

#10 signals = 3'b101;

#10 signals = 3'b110;

#10 signals = 3'b111;

end

adder dut(sum, carry_out, signals[1], signals[0], signals[2]);

initial $monitor("Time=%0d signals=%b sum=%b carry_out=%b",

$time, signals, dut.sum, dut.carry_out);

endmodule

Modulul care descrie functionarea sumatorului complet de un bit poate fi folosit in sinteza altor circuite, cum ar fi sumatorul pentru doua numere binare de cate 4 biti, obtinut prin conectarea in cascada a patru sumatoare de un bit.

4. Modul de lucru

Se lanseaza in executie VeriWell 2.0, se deschide proiectul clc1.prj si se vizualizeaza fisierele componente clc1.v si test_clc1.v. Studiati meniul principal, consultand si optiunea Help. Faceti simularea circuitului si verificati ca nu aveti erori. Vizualizati formele de unda, folosind fereastra wavefile.vwf, asa cum se vede in figura 3.3. Modificati fisierele proiectului, dar salvati-le cu alte nume intr-un subdirector nou, creat de dumneavoastra, si reluati simularea pentru diverse tipuri de porti logice si pentru diverse secvente de intrare. Repetati simularile tinand seama si de timpii de propagare nenuli prin portile logice. Verificati si descrierea comportamentala a circuitului.

Simulati functionarea unui comparator pe 4 biti. Construiti un nou proiect folosind sursele propuse pentru comparatorul din figura 3.4. Incercati sa faceti o descriere comportamentala a circuitului si verificati prin simulare solutia obtinuta. Refaceti testarea circuitului, introducand timpii de propagare pentru portile din circuit.

Descrieti structural sumatorul complet de un bit din figura 3.5. Testati functionarea circuitului, folosind modulul de test recomandat mai sus. Completati modulul sumator realizat anterior prin introducerea timpilor de propagare (considerati un timp de 1 pentru portile NAND si un timp de 2 pentru portile XOR - in general, portile inversoare sunt ceva mai rapide). Rulati din nou programul de testare si remarcati intarzierile semnalelor la iesire, fata de cazul anterior. Observati faptul ca, la inceput, pana la propagarea semnalelor de intrare la iesire, iesirile sunt necunoscute (sunt marcate prin valoarea x).

In programul urmator este descris un sumator pentru 2 numere binare de cate 4 biti, realizat prin conectarea in cascada a 4 module sumatoare de un bit (este folosit modulul adder, proiectat mai sus). Desenati schema descrisa in acest modul, precizand toate semnalele de intrare, iesire si interconectare a celor 4 sumatoare elementare folosite. Apoi, generati o sursa pentru testarea sumatorului de 4 biti. Este posibila testarea circuitului in proportie de 100%?

module four_bit_adder(sum, carry_out, a, b, carry_in);

input carry_in;

input[3:0] a, b;

output carry_out;

output[3:0] sum;

wire carry_1, carry_2, carry_3;

adder add_3(sum[3], carry_out, a[3], b[3], carry_3),

add_2(sum[2], carry_3, a[2], b[2], carry_2),

add_1(sum[1], carry_2, a[1], b[1], carry_1),

add_0(sum[0], carry_1, a[0], b[0], carry_in);

endmodule

Nota: Instructiunea $vw_dumpvars; permite vizualizarea semnalelor prin forme de unda in fereastra wavefile.wmf. Daca ea lipseste din fisierul de test, atunci rezultatul simularii se poate vedea numai in fereastra de consola ca un fisier text, fereastra wavefile.wmf continand formele de unda de la simulari anterioare. Noi am introdus-o numai in primul exemplu.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2194

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2026 . All rights reserved