| CATEGORII DOCUMENTE |

MEMORII SEMICONDUCTOARE

0. Introducere

Sunt circuite integrate care au ca scop stocarea informatiei sub forma binara. Memoriile reprezinta categoria de circuite integrate cu cea mai mare raspandire si vanzare in lume in prezent. Ele se gasesc sub forma distincta sau intra in componenta altor circuite integrate cum ar fi microprocesoare, microcontrolere, FPGA, circuite de telecomunicatii, etc.

1. Clasificarea memoriilor

Traditional se deosebesc doua categorii largi de memorii:

-memorii care pot fi doar citite, denumite ROM (Read Only Memory);

-memorii care pot fi si scrise si citite, denumite RAM (Random Access Memory). In functionare normala, memoriile ROM se pot doar citi. Inscrierea informatiei intr-o astfel de memorie se realizeaza intr-o etapa anterioara utilizarii ei printr-o procedura numita programare (programming sau mai corect burning). Memoriile RAM ar trebui denumita corect RWM (Read Write Memory) deoarece se pot citi si scrie in orice moment si la orice adresa, ele fiind memorii la care accesul poate fi aleator.

Din punct de vedere al tehnologiei de fabricatie exista memorii cu tranzistoare bipolare, MOS, CMOS respectiv BiCMOS.

Memoriile volatile isi pierd continutul la deconectarea alimentarii, pe cand memoriile nevolatile isi mentin informatia stocata si fara prezenta tensiunii de alimentare. In general memoriile ROM sunt nevolatile, iar cele RAM sunt volatile.

In functie de organizarea magistralei de date, deosebim memorii paralel si seriale. In prezent se fabrica memorii seriale EEPROM si SRAM.

In functie de modul de utilizare:

-memorii de program.

-memorii de date. In general memoriile ROM sunt folosite pentru stocarea programelor iar memoriile RAM a datelor.

Clasificarea in memorii RAM si ROM mai are in prezent doar o semnificatie academica, deoarece memoriile EEPROM si Flash pot fi citite si scrise in functionare normala la orice adresa (comportament de RAM), iar memoriile SRAM nevolatile (NV SRAM) stocheaza informatia peste 10 ani fara alimentare externa (comportament de ROM).

Cateva caracteristici importante ale principalelor tipuri de memorii produse in prezent sunt prezentate comparativ in tabelul 5.1. Reprogramabilitatea si posibilitatea de programare in montaj sunt specifice doar unor tipuri de memorii ROM, de aceea campurile aferente lor au fost hasurate in cazul memoriilor RAM. O memorie ideala se caracterizeaza prin capacitate ridicata de stocare (si implicit densitate mare de integrare), timp de acces redus, programabilitate in circuit, informatie nevolatila, consum de curent scazut si cost redus. Categoriile de memorii din tabelul 1 au doua sau mai multe avantaje din cele de mai sus - singura care le indeplineste pe toate fiind insa memoria Flash.

Tabelul 1

Comparatie intre caracteristicile diverselor tipuri de memorii

|

Tipul memoriei |

Capacitate |

Volatila |

Celula elementara cu 1 tranzistor |

Reprogramabila |

Programare in montaj |

|

ROM |

Mare |

NU |

DA |

NU |

NU |

|

PROM |

Mica |

NU |

DA |

NU |

NU |

|

EPROM |

Medie |

NU |

DA |

DA |

NU |

|

OTP |

Medie |

NU |

DA |

NU |

NU |

|

EEPROM |

Medie |

NU |

NU |

DA |

DA |

|

Flash |

Mare |

NU |

DA |

DA |

DA |

|

NV RAM |

Medie |

NU |

NU | ||

|

SRAM |

Mare |

DA |

NU | ||

|

DRAM |

Foarte mare |

DA |

DA |

2. Unitati de masura a informatiei

Bitul este cea mai mica unitate de masura a informatiei. Un bit este prin definitie masura cantitatii de informatie necesara eliminarii nedeterminarii la aruncarea cu banul. In algebra booleana un bit poate memora un 0 sau un 1. Multiplii bitului (notat cu b) sunt kilobitul, megabitul, gibabitul si terabitul:

1kb =210 b=1024b

1 Mb = 220 b = 1024 kb = 1.048.576 b

1 Gb = 2 b =1024 Mb = 1.073.741.824 b

1 Tb = 240 b = 1024 Gb = 1.099.511.62776 b

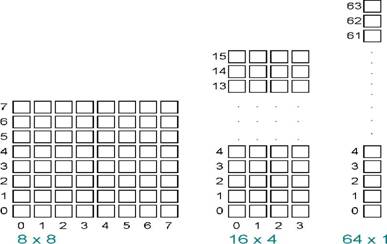

In echipamentele numerice informatia este organizata fizic si logic. Prin organizare fizica se intelege modul de stocare propriu memoriei semiconductoare, iar prin organizare logica - modul de organizare a informatiei in echipament. Cele doua marimi nu sunt neaparat egale. Exista memorii integrate cu organizare multipla de obicei pe 8 sau 16 biti (memoria din figura 1 are o capacitate de 64 de biti si se poate organiza in 64 de cuvinte de 1 bit, 16 cuvinte de 4 biti sau 8 cuvinte de 8 biti).

Marimea logica care caracterizeaza latimea unei adrese de memorie adresata unic se numeste cuvant. Cuvantul are o latime de unul sau mai multi octeti (1, 2, 4 sau 8). Mai multe locatii de memorie de la adrese succesive formeaza o pagina de memorie. O pagina de memorie poate avea 2 kB sau mai mult.

In circuitele de memorie, informatia este organizata fizic pe 1 bit, 4 biti, 8 biti, 16 biti sau 32 de biti. O locatie de memorie de 8 biti se mai numeste octet (byte), iar una de 4 biti o jumatate de octet sau nibble. Octetul (notat o sau B) are aceeasi multipli ca si bitul - kB, MB, GB, TB.

3. Parametrii memoriei

Timpul de acces este cel mai important parametru dinamic al unei memorii si reprezinta durata dintre momentul adresarii memoriei pana la momentul in care la iesirea de date devine disponibila informatia accesata. Timpul de acces este cuprins intre cateva ns la cele mai rapide memorii SRAM la cateva sute de ns la cele mai lente memorii EPROM.

Capacitatea memoriei (exprimata de obicei in multipli de biti sau de octeti) este C = m k unde:

m = numarul de cuvinte distincte ce pot fi adresate;

k = numarul de biti ce corespund fiecarui cuvant memorat.

4. Functionarea unei memorii

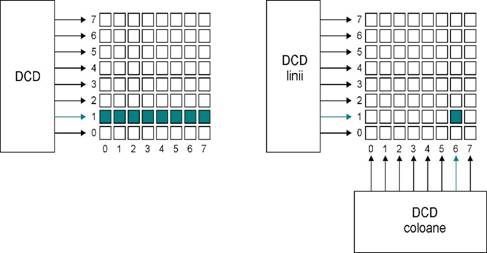

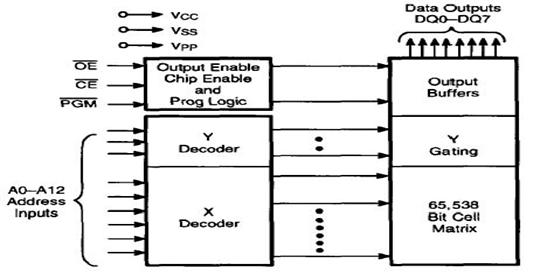

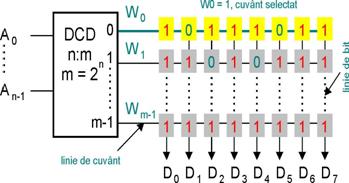

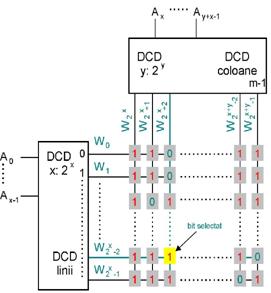

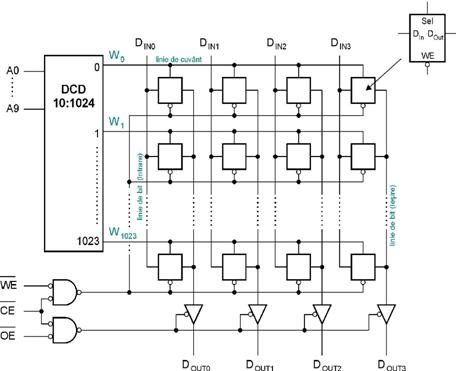

Selectia unui cuvant din memorie se poate face liniar, utilizand un singur decodificator sau prin coincidenta, utilizand doua decodificatoare - unul pentru linii si altul pentru coloane (figura 2). Selectia prin coincidenta este singura utilizata la memoriile de capacitate mare. De exemplu in cazul unei memorii avant o capacitate de 1 Mcuvant, sunt necesare 20 de linii de adresa, iar utilizarea unui singur DCD ar presupune ca acesta sa aiba 1.048.576 linii de iesire, pe cand utilizarea a doua DCD, fiecare cu 10 intrari, reduce numarul de linii de iesire pentru fiecare DCD la 1024. In figura 2 matricea de memorare este presupusa bidirectionala, la selectia prin coincidenta cuvantul avand o latime de 1 bit. In cazul des intalnit in practica de cuvinte pe 4, 8 sau 16 biti modelul matricii de memorare bidirectional nu mai satisface si se utilizeaza un model tridimensional (figura 2).

5. Memorii ROM

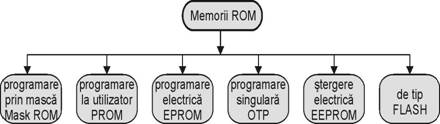

Exista mai multe variante constructive pentru memoriile ROM (figura 3).

Memoriile ROM cu programare prin masca - se refera la memorii programate la producator, caz in care informatia se scrie la locul fabricatiei si nu poate fi modificata ulterior de utilizator. Continutul memoriei este conform cu dorintele utilizatorului. Aceste memorii sunt ieftine, dar se produc doar la comenzi ridicate (peste 10.000 de bucati).

Memoriile PROM (Programmable ROM) pot fi programate la utilizator, dar o singura data (informatia scrisa nu mai poate fi rescrisa).

Memoriile EPROM (Erasable PROM) sunt reprogramabile electric de catre utilizator. Circuitele EPROM se sterg prin expunere la radiatii ultraviolete, permitand apoi o noua inscriere.

Memoriile OTP (One Time Programmable) sunt o varianta a circuitelor EPROM incapsulate in plastic fara fereastra de cuart. Acestea se pot programa o singura data, fiind insa mai ieftine decat omoloagele EPROM.

Memoriile EEPROM (Electrically Erasable PROM) - asigura utilizatorului posibilitatea programarii si stergerii electrice in circuitul final, fara a fi nevoie de expunerea structurii la radiatii ultraviolete.

Memoriile FLASH sunt o varianta de EEPROM la care procesul de stergere este foarte scurt (cateva microsecunde) - fata de zeci de ms la EEPROM, respectiv zeci de minute la expunere la radiatii ultraviolete la EPROM).

Memoriile ROM programabile prin masca si cele PROM s-au produs si cu tranzistoare bipolare; aceste tipuri nu se mai utilizeaza in proiectele moderne. Memoriile EPROM, OTPROM, EEPROM sunt fabricate in tehnologie NMOS si mai ales CMOS.

5.1. Schema bloc a unei memorii ROM

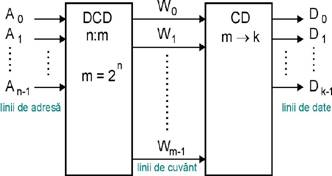

Se pot imagina mai multe arhitecturi didactice pentru a putea explica si intelege functionarea unei memorii ROM. Una dintre acestea (figura 4) se obtine interconectand un decodificator cu un codificator. In figura 5.4, semnificatia liniilor electrice este:

A -An-1 sunt liniile de adresa prin intermediul carora se specifica cuvantul ce va fi citit;

W , , Wm-1 sunt m= 2n linii de cuvant, ele selecteaza intern cuvantul adresat.

D , , Dk-1 sunt k linii de date, k fiind latimea cuvantului memorat.

Aplicand o adresa la liniile A - An-1, la iesirea DCD se activeaza o singura linie Wi. La iesirea CD se obtine un cod pe k biti ce reprezinta chiar informatia inmagazinata in locatia ce corespunde liniei de cuvant Wi active, respectiv adresei selectate la intrarea DCD si implicit a memoriei ROM. In aceasta schema sediul informatiei memorate este CD, DCD necontinand informatia ce urmeaza sa fie citita. Cuvantul binar obtinut la iesirea CD depinde de structura codificatorului, inscrierea sau programarea unui cuvant intr-o anumita locatie se face prin modificarea structurii schemei CD ce corespunde liniei de cuvant respective.

5.2. Memorii ROM programabile prin masca

Un asemenea circuit este produs parcurgandu-se aproape toate etapele normale de fabricatie cu exceptia unei ultime etape in care folosind o masca specifica cerintelor utilizatorului se adapteaza memoria pe baza unui tabel furnizat de utilizator. Prin mascare, grilele tranzistoarelor MOS se conecteaza selectiv la liniile de cuvant (figura 5). O grila conectata inseamna ca la activarea liniei de cuvant ce este conectata la acel tranzistor, acesta va conduce, la iesire pe linia de bit fiind pe 1 logic. O grila neconectata presupune un 0 logic la iesire. Memoria din figura 5 contine 8 cuvinte a 4 biti, avand o capacitate de 32 de biti. In vederea programarii utilizatorul completeaza un tabel similar cu tabelul 2. Daca la adresa 1 se mascheaza baza celui de-al doilea tranzistor, la activarea liniei W1 (W1 = 1), la iesirea de date se va gasi combinatia dorita, adica Q Q Q Q

Tabelul 2

5.3. Memorii PROM

Memoriile PROM s-au realizat cu tranzistoare bipolare si ulterior cu tranzistoare MOS. Varianta cu tranzistoare bipolare oferea capacitati extrem de mici (maxim sute de biti), puteri disipate ridicate (sute de mW) si de aceea ele u se mai folosesc in prezent. Varianta cu tranzistoare MOS ofera capacitati de memorare mult mai mari si putere disipata semnificativ mai redusa decat in cazul celei bipolare.

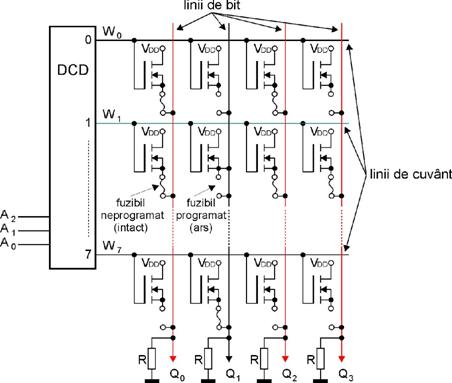

Utilizatorul foloseste un dispozitiv special numit programator prin intermediul caruia poate inscrie informatia dorita intr-o astfel de memorie. Dupa programare, doar in anumite cazuri se mai pot face modificari respectiv programa circuitul. In stare neprogramata, fuzibilele sunt intacte, iesirea fiind pe 1 logic. Programarea se bazeaza pe intreruperea unei conexiuni existente in memoriile neprogramate. Intreruperea se face prin vaporizarea unor trasee prin impulsuri de curent generate in mod corespunzator de echipamentul de programare. Iesirea unui bit programat este pe 0 logic. Memoria PROM din figura 6 are o capacitate de 8 cuvinte a 4 biti, adica de 32 de biti. Pentru a memora la adresa 1 (A A A = 001) cuvantul 1011, in timpul programarii se va "arde" doar cel de-al doilea fuzibil corespunzator liniei W . Dupa programare, la selectia liniei de cuvant W la iesire se va regasi informatia dorita, adica 1011. Trebuie remarcat ca un bit neprogramat poate fi ulterior trecut in 0 la o noua programare, dar un bit programat nu va putea fi readus in 1 logic, cu alte cuvinte la adresa 1 cuvantul 1011 va putea fi reprogramat in 0011, dar nu in 0111.

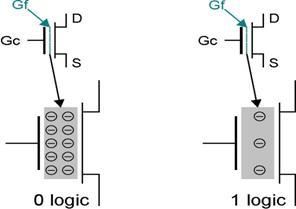

5.4. Memoria EPROM

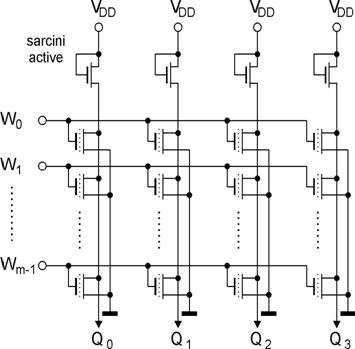

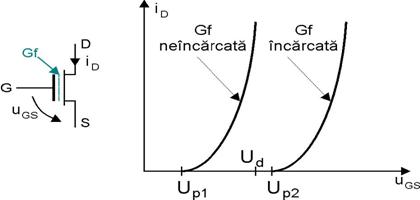

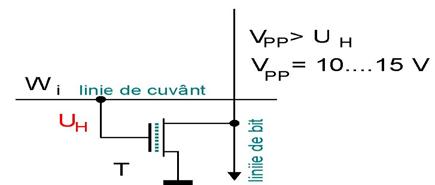

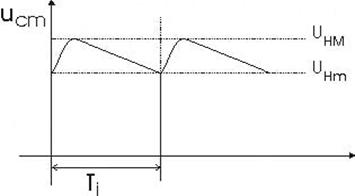

Schema simplificata a unei memorii EPROM la care partea de programare a fost omisa este prezentata in figura Cele 4 tranzistoare MOS din partea superioara a schemei formeaza sarcinile active pentru tranzistoarele utilizate in nodurile matricii de memorare. S-a ales aceasta varianta in locul unor rezistente de sarcina deoarece un tranzistor MOS ocupa un spatiu mai redus in aria de siliciu, iar consumul de putere este mai mic. Daca tranzistoarele matricei de memorare ar fi tranzistoare MOS obisnuite, la activarea liniei de cuvant Wi, toate iesirile ar fi puse la masa puse la masa (0000). Pentru a trece una din liniile de bit pe 1 ar fi necesar ca tranzistorul din nodul ce corespunde liniei Wi sa nu conduca atunci cand Wi = 1, iar programarea ar trebui realizata fara intreruperea legaturii fizice a grilei la linia de cuvant. Pentru aceasta este necesara folosirea unui nou tip de tranzistor MOS, si anume tranzistorul MOS cu grila flotanta, dezvoltare tehnologica care a permis realizarea memoriei EPROM. Caracteristica iD-Ugs a unui astfel de tranzistor MOS (figura 8) depinde de incarcarea cu sarcini negative a grilei flotante. Tranzistoarele din nodurile corespunzatoare unei linii de bit care trebuie sa fie pe 1 trebuie sa aiba poarta flotanta incarcata cu sarcina negativa q-. Programarea este facuta prin incarcarea grilei flotante cu ajutorul unui impuls de programare (10V-15V, tipic 12 V sau uneori 12,5 V) intre drena si sursa tranzistorului, cu durata de cateva zeci de ms, dupa selectarea liniei de cuvant Wi= UH (figura 9).

Tranzistorul MOS cu grila flotanta din figura 9 are Up2 > Ud. La activarea liniei de cuvant Wi(Wi= 1), T nu va conduce, iar linia de bit corespunzatoare va fi in 1 logic datorita sarcinii active formate din alt tranzistor MOS, asa cum se poate observa in figura

Stergerea informatiilor se face iradiind matricea CD cu radiatii UV (ultraviolete) un interval de timp de ordinul zecilor de minute. Deoarece aceasta stergere nu se poate efectua selectiv, dupa expunere memoria EPROM va fi integral stearsa, toti bitii fiind pe 1 logic. Radiatia ultravioleta determina stergerea memoriei EPROM daca are o lungime de unda mai mica de 4000 , valoarea recomandata de catalog fiind de 2537 . Distanta dintre lampa UV si cip trebuie sa fie de circa 2,5 cm, iar puterea radiatiei 12000 mW/cm2; in aceste conditii stergerea completa a circuitului survine dupa 15-20 minute. Studii de specialitate au demonstrat ca expunerea continua a unei memorii EPROM la lumina fluorescenta din camera (care are si o componenta cu lungimea de unda intre 3000 si 4000 ) poate determina stergerea informatiei in circa 3 ani acelasi circuit se sterge in circa 1 saptamana daca este expus la lumina solara directa. Numarul garantat de programari si de stergeri este mai mare de 100, dar defectele sunt frecvente chiar dupa cateva cicluri stergere - programare; durata de mentinere a informatiei memorate este minim zece ani.

Pentru circuitele EPROM moderne, avand capacitati de peste 64 kbiti, o programare octet cu octet la zeci de ms pentru un octet ar fi inacceptabil de lunga (la un EPROM 27512 de 512 kbiti, programarea ar dura 20 ms x 65536 octeti = 22 minute). Pentru reducerea timpului de programare au fost imaginati algoritmi de programare rapida, la care pe durata programarii se face VDD = 6VsiVPP =12,5V, impulsul de programare reducandu-se la 1 ms sau in unele cazuri chiar de 100 s! Prin aceasta chiar la memoriile EPROM de capacitati relative ridicate (peste 1 Mbit), programarea dureaza maxim cateva minute.

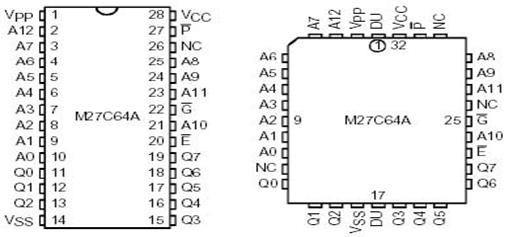

Memoria EPROM 2764A

2764A este o memorie NMOS de 64 kbiti organizata ca 8 k cuvinte de 8 biti, oferita de o serie de producatori. Dispunerea pinilor este prezentata in figura 26, iar aspectul capsulei in figura 13.

Tabelul 3

Modurile de operare pentru memoria EPROM 2764A

|

Mod |

nCS |

nOE |

nPGM |

A |

VPP |

Q - Q |

|

Citire (Read) |

X |

VDD |

Data Out |

|||

|

Inhibare iesiri (Output Disable) |

|

X |

VDD |

HiZ |

||

|

Asteptare (Standby) |

X |

X |

X |

VDD |

HiZ |

|

|

Programare (Program) |

impuls |

X |

VPP |

Data In |

||

|

Verificare (Verify) |

X |

VPP |

Data Out |

|||

|

Inhibarea programarii (Program Inhibit) |

X |

X |

X |

VPP |

HiZ |

|

|

Identificare inteligenta (Electronic Signature) |

12 V |

VDD |

Octet identificare |

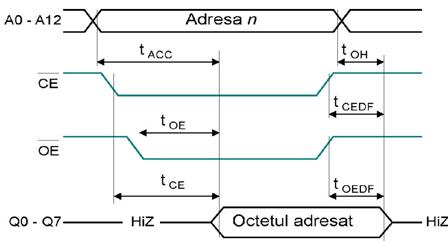

Memoriile EPROM prezinta doua terminale de control asemanatoare: nCS si nOE. Pentru nCS = 1, circuitul este trecut in modul asteptare, in care iesirile sunt in starea de inalta impedanta, iar consumul de curent este substantial redus. nOE controleaza doar bufferele de iesire, care sunt inhibate pentru nOE = 1 si validate pentru nOE = 0. Motivatia existentei a doua terminale de control este mai subtila: intr-un sistem cu microprocesor, controlul cu doua terminale evita conflictele pe magistrala daca se utilizeaza mai multe asemenea memorii si un decodoficator pentru selectia lor. Microprocesorul va emite semnalele de adresa, din care o parte (cele mai semnificative) sunt folosite de DCD si semnalul nRD, care va fi conectat la intrarile nOE ale tuturor memoriilor.

Fabricantul specifica in foaia de catalog punctele de test pentru 0 si 1 logic. In cazul memoriei 2764A aceste puncte de test sunt 0,8 V si 2 V (niveluri TTL), figura 11. Aceste puncte de test sunt valabile si pentru memorii EPROM mai noi, de exemplu pentru memoria de 1 Mbit 27C010, realizata in tehnologie CMOS.

![]()

Figura 11. Punctele de test pentru starea 0 si 1 in cazul memoriei EPROM 2764A.

Datorita numarului mare de variante de memorii EPROM si a specificatiilor uneori usor diferite pentru acelasi tip de circuit la diferiti producatori, memoriile EPROM moderne dispun de un mecanism de identificare inteligenta pe baza unei semnaturi electronice (Electronic Signature). Pe baza semnaturii electronice se identifica tipul circuitului (codificat pe un octet) si producatorul (codificat tot pe un octet). Aceste informatii sunt citite automat de echipamentul de programare care va selecta algoritmul de programare potrivit circuitului utilizat fara interventia operatorului uman, eliminandu-se astfel o posibilitate de eroare. Pentru a activa modul de identificare inteligenta, adresa A9 trebuie adusa la o tensiune de 12 V, toate celelalte linii de adresa se mentin la 0 logic; pentru A0 = 0 logic la liniile de date se va putea citi codul producatorului, (de exemplu pentru SGS-THOMSON se va citi 20H), iar pentru A0 = 1 se va putea citi codul circuitului, in acest caz 08H.

Caracteristici principale 2764A:

timp de acces: 180 ns;

curent de alimentare in repaus: 35 mA;

curent de alimentare in functionare normala: 75 mA

tensiune de programare VPP = 12 V;

algoritm de programare rapid (durata totala de programare este sub 1 minut);

identificare inteligenta prin semnatura electronica;

Varianta CMOS pentru acelasi circuit, notata 27C64 este compatibila pin la pin cu predecesoarea sa si ofera urmatoarele caracteristici imbunatatite:

timp de acces: 150 ns

curent de alimentare in repaus: 100 A

curent de alimentare in functionare normala: 30 mA

tensiune de programare VPP = 12,5 V;

algoritm de programare rapid (durata totala de programare este sub 1 minut);

identificare inteligenta prin semnatura electronica;

5.5. Memoria OTP (One Time Programmable

Este tot o memorie EPROM programata electric la producator sau la utilizator fara fereastra de cuart pentru stergere, avand un pret mai mic cu circa 40% decat la varianta EPROM. Utilizatorul nu o mai poate reprograma ulterior. Este rentabila in productia de masa, fiind asemanatoare cu memoria ROM programata prin masca. Memoriile OTP sunt de obicei disponibile in capsule de plastic ieftine, cum ar fi PLCC (Plastic Leaded Chip Carrier). Memoria 27C64A de exemplu este oferita in varianta OTP intr-o capsula PLCC 32 (cu 32 de terminale fata de 28 la varianta DIP, cu mentiunea ca cele 4 terminale suplimentare nu se folosesc).

NC = neconectat, DU = nu se foloseste

5.6. Memoria EEPROM

Elimina dificultatile de extragere din soclu si expunere la lumina ultravioleta. Atat programarea cat si stergerea se executa electric. Prin perfectionarea tehnologiei si micsorarea grosimii stratului izolator al grilei flotante exista posibilitatea programarii si stergerii electrice cu tensiuni mici aplicate intre drena si poarta. Polaritatea caderii de tensiune drena-poarta este inversata la stergere fata de programare. Sunt mai scumpe decat memoriile Flash; se pot rescrie in timpul functionarii, numarul de stergeri si reprogramari fiind cu un cel putin un ordin de marime mai mare decat la memoriile Flash.

Memoria EEPROM 2864B

2864B este o memorie EEPROM CMOS de 64 kbiti organizata ca 8 k cuvinte de 8 biti, oferita de mai multi producatori. Dispunerea pinilor este redata in figura 26, iar modurile de operare in tabelul 4.

Tabelul 4

Modurile de operare pentru memoria EEPROM 2864B

|

Mod |

nCE |

nOE |

nWE |

I/O - I/O |

|

Citire (Read) |

Data Out |

|||

|

Scriere (Write) |

Data In |

|||

|

Inhibare scriere (Write Inhibition) |

X |

X | ||

|

X |

X | |||

|

Asteptare (Standby) |

X |

X |

HiZ |

Caracteristici principale pentru memoria EEPROM 2864B:

timp de acces - 150 ns;

curent de alimentare in repaus: 1 A;

curent de alimentare in functionare normala: 30 mA

numar minim de stergeri si de reprogramari: 105

durata de mentinere a informatiei memorate: minim 10 ani;

5. Memoria Flash

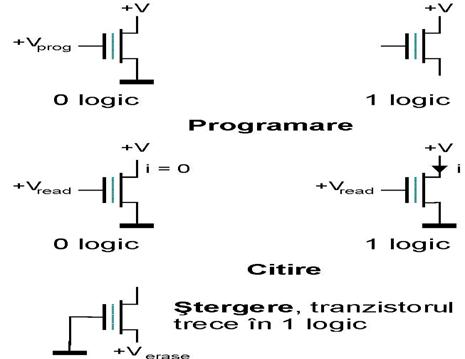

Memoriile Flash permit atat citirea cat si inscrierea informatiei in timpul functionarii normale; sunt memorii de densitate mare, nevolatile, folosite in cele mai diverse aplicatii - de la aparatele de fotografiat digitale la inlocuirea de hard-diskuri. Celula de memorare a unui bit consta dintr-un singur tranzistor MOS cu grila flotanta. Stocarea propriu-zisa este realizata prin prezenta sau absenta sarcinilor in grila flotanta. O sarcina relativ ridicata acumulata in grila flotanta (figura 15) este echivalenta cu 0 logic, iar o sarcina redusa sau absenta cu 1 logic.

Programarea

In stare neprogramata,

toate celulele memoriei sunt in 1 logic (sarcini reduse sau nule in grila

flotanta).

Daca in procesul de programare se doreste memorarea unui 0 logic, grila de

control se aduce la un

potential pozitiv +Vprog, prin aceasta fiind

atrasi electroni spre grila flotanta, ea incarcandu-se negativ.

O data programata, sarcina grilei flotanta se mentine un timp indelungat -

minim 10 ani.

In cazul in care se doreste stocarea unui 1 logic, in timpul programarii celula

respectiva este lasata

nemodificata.

Citirea

Pe durata operatiei de

citire, la grila de control se aplica o tensiune pozitiva + Vread. Cantitatea de

sarcina stocata in grila flotanta va determina in acest caz daca sub actiunea

acestei tensiuni,

tranzistorul MOS va conduce sau nu: daca se memoreaza un zero, datorita

numarului mare de electroni

de pe grila flotanta, tranzistorul ramane blocat. In contrast, daca grila

flotanta contine putini electroni,

sub influenta tensiunii +Vread tranzistorul

MOS va conduce (figura 5.16).

Stergerea

Operatia de stergere se rezuma la inlaturarea electronilor din grila flotanta - aducand grila de control la potentialul masei si sursa la o tensiune pozitiva (+ Verase), electronii vor fi atrasi spre sursa si prin aceasta grila flotanta nu va mai contine sarcini negative sau numarul acestora va fi foarte redus. O memorie Flash este intotdeauna stearsa inainte de a fi programata. La memoriile Flash moderne stergerea se realizeaza pe blocuri sau paginat, dar important este ca un octet singular din cadrul unui bloc nu poate fi scris (programat) decat dupa ce este sters impreuna cu intregul bloc din care face parte. Memoriile Flash ofera suplimentar posibilitatea stergerii globale rapide (bulk erase).

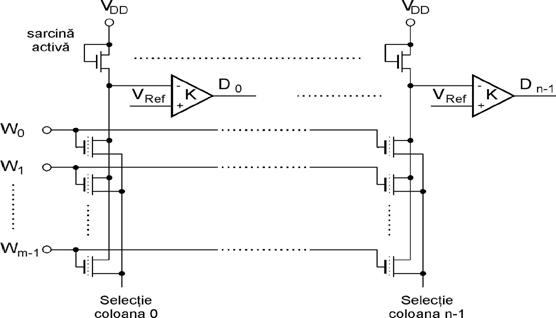

Schema simplificata pentru operatia de citire a unei memorii Flash este ilustrata in figura 1 Aria de memorie contine m cuvinte a n biti fiecare, adica un total de m x n tranzistoare MOS cu grila flotanta pentru acelasi numar de biti de informatie. La fiecare linie de bit un tranzistor MOS formeaza sarcina activa (aceasta abordare este mai eficienta decat cea in care ar fi dispuse rezistente de sarcina, de ce?). Pentru citire se activeaza o linie de cuvant, fiecare din cele n comparatoare furnizand la iesire 1 sau 0 logic, dupa cum tranzistoarele MOS de memorare conduc sau nu (1 logic daca tranzistorul conduce, 0 logic in caz contrar).

Caracteristici generale:

timp de acces: 45 - 150 ns;

numar de stergeri si de reprogramari este de ordinul 104 - 105;

durata de mentinere a informatiei memorate este de minim 10 ani;

sunt cele mai ieftine memorii nevolatile;

se pot rescrie in timpul functionarii.

Memoria Flash 29F010

29F010 este o memorie Flash CMOS de 1 Mbit organizata ca 128 k cuvinte de 8 biti, oferita de mai multi producatori. Dispunerea pinilor este prezentata in figura 28, iar modurile de operare in tabelul 5.

Tabelul 5

Modurile de operare pentru memoria Flash 29F010

|

Mod |

nCE |

nOE |

nWE |

A0 |

A1 |

A9 |

I/O0-I/O7 |

|

Citire (Read) |

A0 |

A1 |

A9 |

Data Out |

|||

|

Scriere (Write) |

A0 |

A1 |

A9 |

Data In |

|||

|

Asteptare (Standby) |

X |

X |

X |

X |

X |

HiZ |

|

|

Inhibare iesire (Output Disable) |

X |

X |

X |

HiZ |

|||

|

Identificare - Codul circuitului |

12 V |

ID |

|||||

|

Id. inteligenta - Codul producatorului |

12 V |

ID |

|||||

|

Protectie sector (Verify Sector Protect) |

12 V |

ID |

Caracteristici principale 29F010:

timp de acces - 45 ns;

curent de alimentare in repaus: 25 A;

curent de alimentare in functionare normala: 30 mA la citire, 50 mA la programare sau stergere;

este impartit in 8 sectoare de 16 kocteti;

permite stergerea intregului circuit sau a oricarui sector;

stergerea si verificarea unui sector dureaza sub 1 secunda;

permite identificarea inteligenta in montaj, activata pentru A9 = 12 V, similar cu memoriile EPROM;

identificarea inteligenta se poate realiza in circuit si in absenta tensiunii ridicate de 12 V printr-o serie de comenzi;

numar minim de stergeri si de reprogramari: 105;

durata de mentinere a informatiei memorate: minim 10 ani;

6. MEMORII RAM

Sunt circuite integrate cu integrare pe scara foarte larga (VLSI) care permit in timpul functionarii atat citirea cat si inscrierea in locatia adresata. O denumire mai potrivita pentru aceste memorii este de memorii RWM (Read-Write Memory).

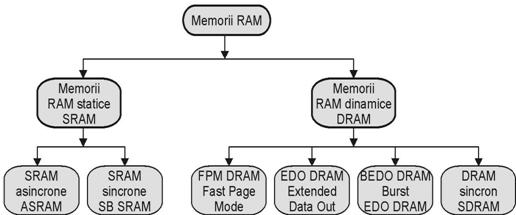

Clasificare RAM:

-RAM statice (SRAM), realizate cu bistabile in tehnologie bipolara sau

unipolara;

-RAM dinamice (DRAM), numai in tehnologie unipolara NMOS sau CMOS.

Dupa modul de selectie a locatiei: selectie liniara, in cazul memoriilor de capacitate redusa, organizate pe cuvinte de mai multi biti; selectie prin coincidenta, in cazul memoriilor de capacitate relativ ridicata, organizate pe cuvinte de un bit; selectia tridimensionala, in cazul memoriilor de capacitate foarte mare, organizate pe cuvinte de mai multi biti.

6.1. Selectia cuvantului adresat

Selectia liniara se realizeaza similar cu selectia omonima prezentata la memoriile ROM. Memoria din figura 19 este organizata pe m = 2n octeti. Pentru combinatia de adrese An-1 A = 00, W = 1, selectandu-se primul octet, care se va regasi la iesire (10111011).

Selectia prin coincidenta utilizeaza doua decodificatoare de adresa, unul pe linii si celalalt pe coloane. Nodul selectat din memoria din figura 5.20 corespunde adresei de linii A0 Ax-1 = 0 1 1 si de coloane Ax Ax+y-1 = 0 0 1 0 0. Pentru o folosire eficienta a ariei de siliciu ocupate se cauta ca matricea de memorare sa fie patrata sau cat mai aproape de un patrat in cazul unui numar impar de adrese, dimensiunile celor doua DCD fiind egale sau apropiate.

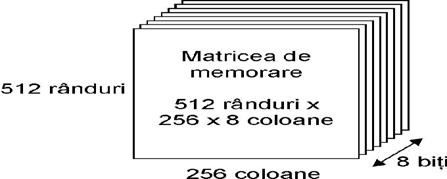

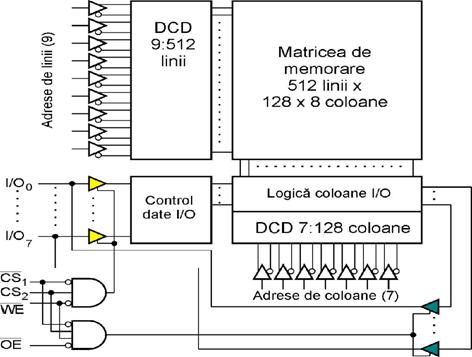

La memoriile RAM de capacitate mare (de peste 1 Mbit) decodificarea bidirectionala nu mai este suficienta, deoarece numarul de linii ale fiecaruia dintre cele doua DCD va depasi 1000. Din acest motiv informatia stocata este dispusa intr-o matrice tridimensionala. De exemplu la memoria 628128A de 128 x 8 kbiti, matricea de memorare se prezinta ca in figura 21. In acest caz decodificarea se face bidimensional, existand 512 randuri a 256 de coloane, dar in punctul de selectie, cuvantul nu are lungimea de 1 bit, ci de 8 biti.

6.2. Memoria SRAM

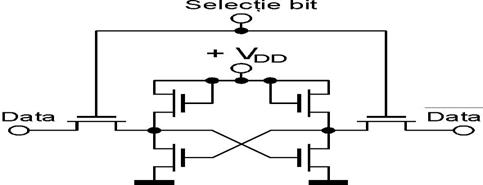

Aceste memorii sunt realizate cu bistabile, celula elementara fiind cea din figura 22.

Terminale memoriei sunt: A0. An-1 -linii de adresa, /CS -selectie capsula, Do0Do(k-1) -date iesire, /OE -validare iesire, Di0Di(k-1) -date intrare, /nWE -validare scriere.

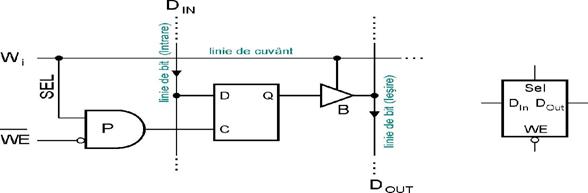

Celula completa de memorie pentru 1 bit cu latch D (figura 23).

Descrierea functionarii: Pentru a putea face o operatie de citire sau de scriere este necesar ca celulele sa fie selectata cu ajutorul liniei de cuvant Wi activa pe 1. Linia de cuvant furnizeaza deci semnalul SEL ce actioneaza asupra portii P si a bufferului B. O data selectat, bufferul B se afla in stare normala de functionare. Cealalta intrare a portii SI se foloseste pentru stabilirea operatiei ce se va efectua: citire (nWE = 1) sau scriere (nWE = 0). La citire (nWE = 1) trebuie selectata celula (SEL=1); in acest caz intrarea C a bistabilului este 0 (C=0) si oricare ar fi datele pe linia de intrare ele nu se inmagazineaza in D-latch in schimb B fiind in stare normala, obtinem la iesirea Do pe Q memorat in bistabil. La scriere (nWE = 0) trebuie selectata celula (SEL=1); in acest caz ceea ce exista pe linia LBIN se inscrie in D-latch. Cu alte cuvinte ceea ce am pe liniile de intrare DIN se va transfera in bistabil (adica la iesirea Q a acestuia). Daca celula nu este selectata (SEL = 0), C = 0, iar B se afla in starea de impedanta ridicata (HiZ).

Consideram in cele ce urmeaza o memorie ipotetica de 1024 cuvinte de cate 4 biti. Aceasta memorie va contine 4192 de celule, selectate liniar prin intermediul unui DCD 10:1024 (figura 24).

Tabelul 6

Functionarea memoriei SRAM

|

Operatie |

CS |

OE |

WE |

|

Citire (Read) | |||

|

Scriere (Write) | |||

|

Memorare (Hold) |

X |

X |

Descrierea functionarii

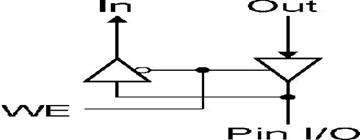

Reducerea numarului de pini ai capsulei circuitului integrat se poate realiza folosind pini unici pentru intrare si iesire, caracteristica obtinuta adoptand urmatoarea structura I/O (figura 25):

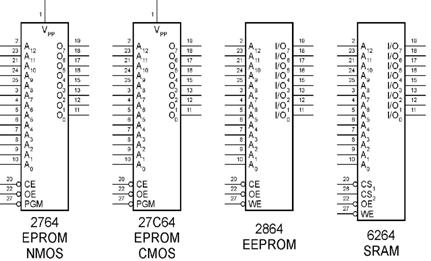

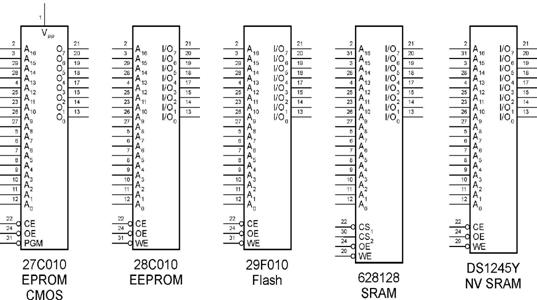

Dispunerea terminalelor la memoriile SRAM respecta aranjamentul initiat de memoriile EPROM si continuat de memoriile EEPROM, in figura 26 fiind prezentata dispunerea terminalelor pentru memoriile de 64 kbiti.

Memoria SRAM HM6264A de 64 kbiti (Hitachi)

Memoria SRAM 6264 nu are pin de tensiune de programare (pinul 1, VPP de la EPROM), acesta ramanand neconectat, iar selectia circuitului se face cu 2 semnale (nCS1 si CS2), aspect folositor pentru extinderea capacitatii (vezi si aplicatiile de la 5.8). De cele mai multe ori producatorul de memorii specifica timpul de acces ca un prefix la denumirea circuitului, de exemplu Hitachi ofera circuitele HM6264A-10 (100 ns), HM6264A-12 (120 ns) si HM6264A-15 (150 ns).

Caracteristici principalele pentru memoria HM6264-10:

timp de acces - 100 ns;

putere disipata in repaus: 100 W;

putere disipata in functionare normala: 15 mW / MHz;

8 intrari si iesiri trei-stari comune.

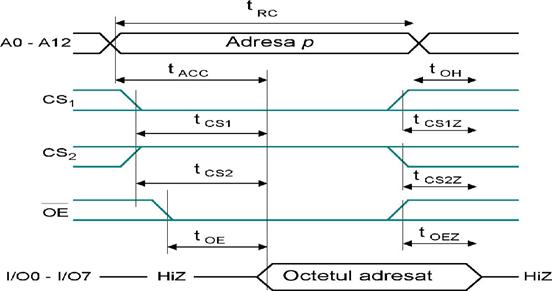

Diagramele de citire (figura 27) pentru memoria 6264 sunt asemanatoare cu cele de la memoria EPROM. Toate valorile urmatoare se vor referi la memoria HM6264A-10, la care timpul de acces (tACC) este de 100 ns. Pentru citire, trebuie specificata o adresa pe liniile A0-A12 pe durata ciclului de citire, a carui durata minima tRC este de 100 ns. Deoarece memoria SRAM este statica, nu este specificata si o valoare maxima - tRC poate fi oricat de lung.

Tabelul 7

Principalii parametri dinamici ai ciclului de citire pentru memoria SRAM HM6264A-10

|

Parametru |

Simbol |

Min |

Max |

UM |

|

|

Durata ciclului de citire (Read cycle time) |

tRC |

ns |

|||

|

Timpul de acces (Address access time) |

tACC |

ns |

|||

|

Timpul de acces selectie circuit -iesire (Chip Seletion to Output) |

CS1 |

tCS1 |

ns |

||

|

CS2 |

tCS2 |

ns |

|||

|

Timp de acces validare iesire (Output enable to output valid) |

tOE |

ns |

|||

|

Timp inhibare circuit (Chip deselection to output in HiZ) |

CS1 |

tCS1Z |

ns |

||

|

CS2 |

tCS2Z |

ns |

|||

|

Timp inhibare iesiri (Output disable to output in HiZ) |

tOEZ |

ns |

|||

|

Timpul de mentinere de la modificarea adresei (Output hold from address change) |

tOH |

ns |

|||

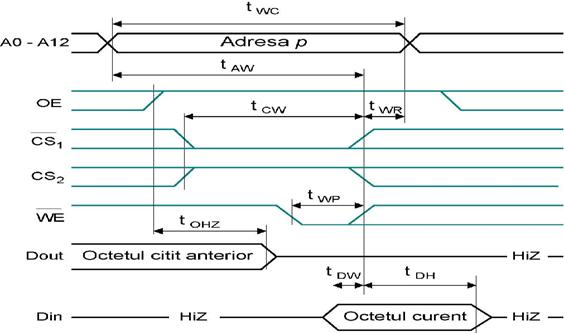

Scrierea informatiei in memorie se realizeaza conform diagramelor din figura 28.

Tabelul 8

Principalii parametri dinamici ai ciclului de scriere pentru memoria SRAM HM6264A-10

|

Parametru |

Simbol |

Min |

Max |

UM |

|

Durata ciclului de scriere (Write cycle time) |

tWC |

ns |

||

|

Timpul selectie circuit - sfarsitul nWE (Chip selection to end of write) |

tCW |

ns |

||

|

Timpul adrese valide - sfarsitul nWE (Address valid to end of write) |

tAW |

ns |

||

|

Latimea impulsului de scriere (Write pulse width) |

tWP |

ns |

||

|

Timpul de recupereare nWE (Write recovery time) |

tWR |

ns |

||

|

Timp suprapunere Dout cu nWE (Data to write time overlap) |

tDW |

ns |

||

|

Timpul de mentinere pentru DiN (Data hold from write time) |

tDH |

ns |

||

|

Timp inhibare iesiri (Output enable to output in HiZ) |

tOHZ |

ns |

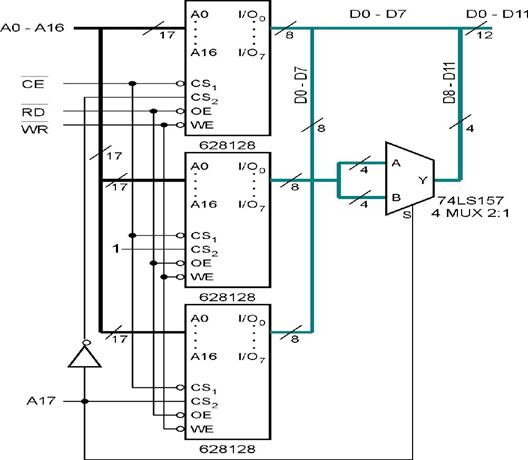

Exista si pentru celelalte memorii o compatibilitate a pinilor. Pentru familia de memorii de 1 Mbit organizate ca 128 kcuvinte de 8 biti, dispunerea terminalelor pentru cele mai reprezentative circuite este prezentata in figura 28. Memoria SRAM 628128 este un alt exemplu de memorie SRAM de 1 Mbit, avand structura reprezentata simplificat in figura 29.

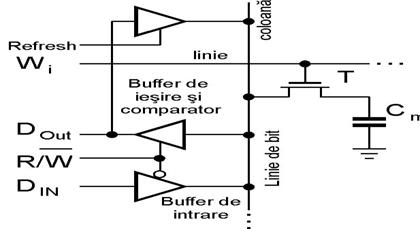

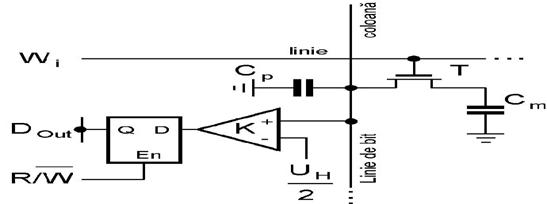

6.3. Memorii DRAM

Memorarea se realizeaza prin incarcarea sau

descarcarea unei capacitati (integrate sau parazite) Cm.

Daca Cm este incarcata la UH, daca Cm este

incarcata la UL (descarcata) → 0.

Aceasta categorie de memorii se realizeaza numai in tehnologie MOS. Celula de

memorare actuala

contine un singur tranzistor MOS si functioneaza in regim de impulsuri.

Bufferul B deserveste toate celulele conectate la linia de bit LB, din care s-a prevazut o singura celula. Cu ajutorul lui B se alimenteaza in impuls linia de bit. Fiecare linie de bit este prevazuta cu comparatorul K si bistabilul D-latch ce servesc la citirea informatiei. Linia de cuvant este activa pe 1 actionata in impulsuri. Celula de memorare propriu-zisa se compune din tranzistorul de comutatie T si capacitatea integrata de memorare de valoare foarte mica Cm

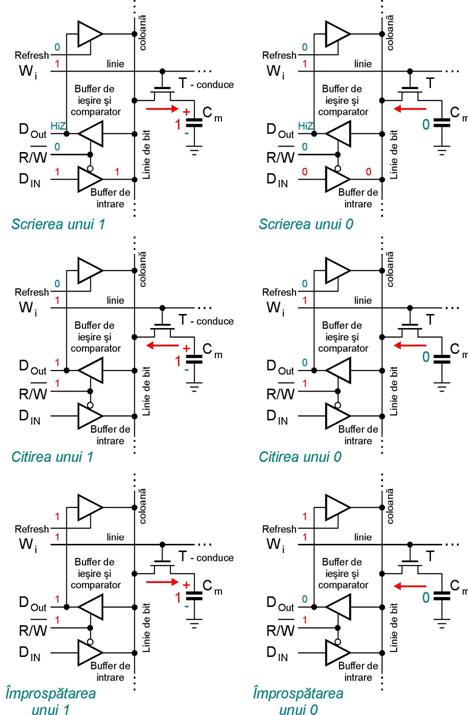

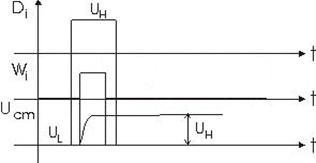

Descrierea functionarii

Scrierea

Inscrierea unui 1 in celula se face punand linia de bit LB la UH prin activarea bufferului B. In acest timp se aplica un impuls de inaltime tot UH liniei de cuvant Wi = 1 care determina intrarea in conductie a tranzistorului T si incarcarea lui Cm la UH

Pentru inscrierea unui 0 in celula, linia LB ramane pe UL (apropiat de 0). Liniei de cuvant i se da un impuls de inaltime UH, care si in acest caz pune in conductie tranzistorul T descarcand condensatorul Cm

Citirea

Comparatorului K va avea iesirea pe 0 care este memorat de bistabilul D-latch. Dupa fiecare operatie de citire, care altereaza nivelul de tensiune de la bornele Cm se efectueaza o operatie de reanscriere a bitului citit folosind iesirea bistabilului D-latch (reimprospatarea informatiei alterate prin citire). Nu numai prin citire are loc o alterare a informatiei inscrise in Cm ci si datorita descarcarii exponentiale in timp a acesteia datorita curentilor de pierdere. Din acest motiv, chiar daca nu se efectueaza citiri, este necesara reimprospatarea sarcinii acumulate in Cm la fiecare 2-4ms (depinde de tipul memoriei).

Timpul mediu necesar unei improspatari este in medie de 0.3 s si daca improspatarea s-ar face bit dupa bit in intervalul de 4 ms ar putea fi improspatate:

celule, neexistand timp pentru alte operatii

utile.

celule, neexistand timp pentru alte operatii

utile.

Pentru o memorie de 64kb (65536 biti) satisfacerea timpului disponibil de improspatare impune adaptarea unei structuri patrate a matricii de celule de memorie, corespunzatoare la 256/256 biti adica

o structura organizata pe 256 linii de

cuvant, fiecarui cuvant corespunzandu-i k = 256 biti.

In acest caz datorita improspatarii simultane a tuturor celulelor selectate de

o linie de cuvant timpul

necesar pentru improspatarea intregii memorii va fi de:

![]() , care constituie

, care constituie![]() din

timpul disponibil pentru reamprospatare. Deci 98% din intervalul de timp dintre

doua improspatari succesive poate fi folosit pentru efectuarea unor operatii

utile de citire si inscriere a informatiei.

din

timpul disponibil pentru reamprospatare. Deci 98% din intervalul de timp dintre

doua improspatari succesive poate fi folosit pentru efectuarea unor operatii

utile de citire si inscriere a informatiei.

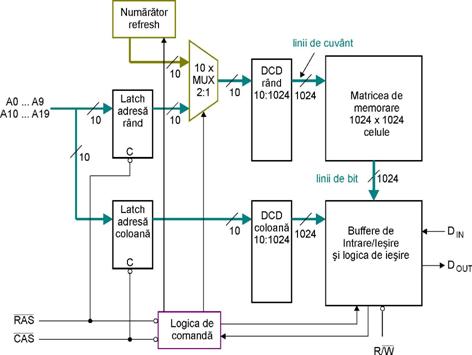

Pentru exemplificare, in figura 37 este prezentata schema bloc a unei memorii DRAM de 1024kbiti organizata pe cuvinte de cate 1 bit, a caror selectie se realizeaza prin coincidenta.

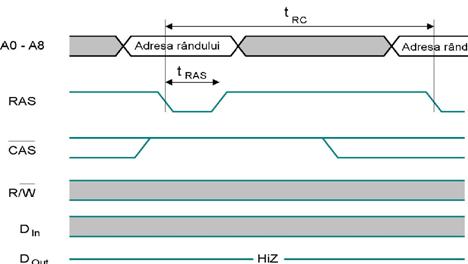

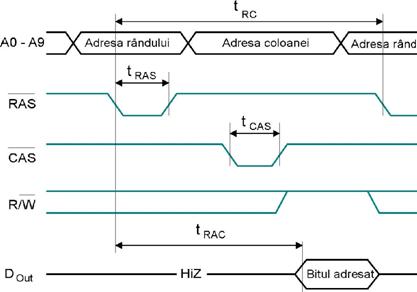

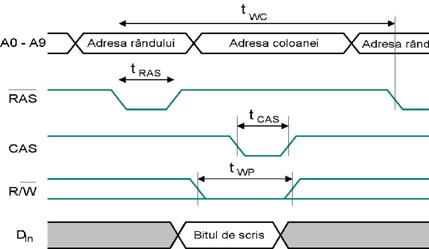

Terminalele circuitului sunt: A0A9, linii de adresa, /RAS - semnal de tip strobe pentru memorarea adreselor de linie, (Row Address Strobe); /CAS - semnal de tip strobe pentru memorarea adreselor de coloana (Column Address Strobe); R/nW - comanda citirii (= 1), respectiv a scrierii (= 0) Read / Write Enable; DIN, linia de date de intrare, DOUT. - linia de date de iesire.

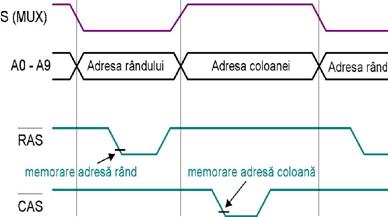

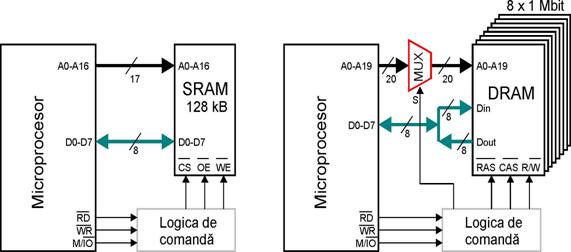

Pentru a accesa 220 = 1.048.567 locatii de memorie sunt necesare 20 de linii de memorie (A0 .. A19). Incepand cu primele circuite DRAM, in scopul reducerii numarului de pini ai capsulei, s-a utilizat o tehnica de multiplexare a adreselor, circuitul avand doar 10 pini de intrare pentru adrese si doua semnale specifice de comanda - nRAS pentru comanda adreselor corespunzatoare decodificatorului de linii, respectiv nCAS pentru comanda adreselor corespunzatoare decodificatorului de coloane. Deoarece un circuit tipic de memorie DRAM nu are nici o intrare nCS, economia este de 10 terminale, rezultand o capsula cu 18 terminale la o capacitate de stocare de 1 Mbit, ceea ce este remarcabil.

Intai se aplica prima jumatate a cuvantului de adresa A0.A9, apoi a doua jumatate A10.A19. Circuitul de comanda contine doua lacth-uri D de memorare a celor doua jumatati ale cuvantului de adresa. Prin intermediul liniilor A0.A9 se comanda decodificatorul care are rolul de a selecta o singura linie de cuvant. Incarcarea A0.A9 in registrul din circuitul de comanda se face prin activarea liniei /RAS. Cu liniile A10.A19 se comanda blocul MUX/DMUX prin care se selecteaza o singura linie de bit (la citire prin MUX, iar la inscriere prin DMUX). Incarcarea adreselor A10.A19 in registrul corespunzator din circuitul de comanda se face prin activare liniei /CAS (Column Address Strobe). Linia de control stabileste care dintre cele doua circuite (MUX sau DMUX) este activ. Evident la citire este activ MUX-ul, iar la scriere DMUX-ul.

Mai exista la iesirea magistralelor liniilor de bit un registru RLB cu 256 bistabile D-latch. Schimbul de informatie intre matrice si registru este bidirectional. In cazul operatiilor de citire este activata si linia ce valideaza in stare normala bufferul B pentru Dout.

Improspatarea

Pe frontal scazator al semnalului /RAS se inregistreaza adresa liniei de cuvant in registrul din circuitul de comanda. Se selecteaza o linie de cuvant ce corespunde acestei adrese si se inscrie continutul fiecarei celule ce corespunde lui LC selectat in RLB. Pe frontul crescator al semnalului /RAS se reanscrie informatia din registru regenerata in celulele apartinatoare liniei de cuvant selectata. In continuare se trece la urmatoarea linie de cuvant in vederea improspatarii tuturor celulelor. Generarea adreselor pentru improspatarea memoriei se face folosind un numarator pe 8 biti ce functioneaza continuu. Se constata ca nu intervine adresa ce stabileste linia de bit in care se face inscrierea sau citirea.

Citirea din memorie

Se aplica A0.A9 si se activeaza linia /RAS pentru incarcarea adresei liniei de cuvant in latch-ul din circuitul de comanda, fapt ce duce la selectia unei linii de cuvant si se scrie continutul celulelor de pe linia de cuvant in registrul RLB. Apoi intr-o alta secventa se aplica la intrare A10.A19. Semnalul /WE trebuie sa fie pe 1 (se executa o operatie de citire). Dupa aplicarea celei de-a doua jumatati a adresei se aplica semnalul /CAS activ pe "0". Pe frontul scazator al semnalului /CAS se memoreaza A10.A19 in latch-ul de 10 biti din circuitul de comanda. Se aplica acesti 10 biti MUX-ului, se selecteaza una dintre cele 1024 de iesiri ale registrului RLB si se transmite la bufferul B inspre iesire Dout. Simultan bufferul B este trecut in stare normala.

EXTINDEREA CAPACITATII DE MEMORARE

Extinderea

capacitatii de memorare este un caz des intalnit in practica, prin care se

doreste realizarea

unei memorii avand o capacitate mai mare decat cea a unui singur circuit

integrat, fie ca numar de biti

ai cuvantului memorat (extensia in latime), fie ca numar de cuvinte memorate

(extensia in adancime),

fie in ambele directii (extensia mixta).

In toate aceste situatii, etapele de proiectare sunt:

determinarea numarului de circuite de memorie necesare

determinarea schemei electrice a electronicii suplimentare, daca ea exista.

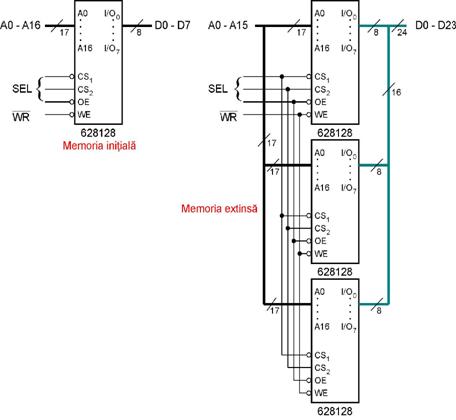

1. Extensia numarului de biti ai cuvantului adresat

Acesta este cel mai simplu caz - deoarece numarul de cuvinte memorate este suficient pentru aplicatia concreta. In exemplul urmator, presupunem ca se doreste modernizarea memorie operative a unui sistem de achizitie video prin trecerea de la imagini alb-negru in 256 de nuante de gri (codificate pe 8 biti) la imagini color codificate pe 24 de biti (16.77216 culori). Imaginea are o rezolutie de 320 x 240 de puncte (76.800 puncte), se achizitioneaza si prelucreaza o singura imagine si de aceea o memorie de 128 kbit x 8 era suficienta pentru cazul alb-negru. In acest exemplu determinarea numarului de circuite necesare este banal, fiind evident necesare 3 asemenea circuite (figura 41). Memoria initiala folosea un singur circuit, cea modernizata utilizeaza trei asemenea circuite. Conectarea se face legand in paralel linie cu linie toate intrarile celor trei memorii (adresele A0-A15, liniile de sectie SEL si linia de comanda a scrierii nWR). Liniile de iesire sunt separate si formeaza noua magistrala de 24 de biti.

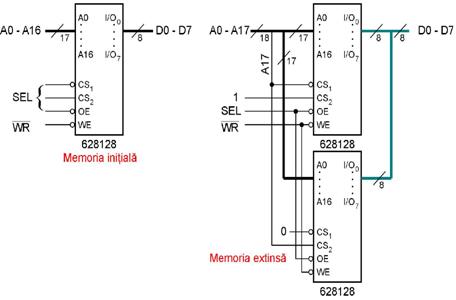

8.2. Extensia numarului de cuvinte adresate

In acest caz presupunem ca la sistemul de achizitie prezentat anterior se doreste marirea rezolutiei de la 320 x 240 de pixeli la 640 x 400 pixeli (256.000 de puncte), iar reprezentarea pe 8 biti cu niveluri de gri este suficienta. Numarul de circuite de memorie necesare este:

Capacitatea totala 256.000 pixeli

N = ![]() == 2 cipuri

== 2 cipuri

Capacitatea unui circuit 131.072 biti

In acest caz numarul de adrese necesare sistemului de achizitie este 17, intervenind suplimentar si A16, care va fi utilizata pentru selectarea alternativa a celor doua circuite de memorare. Daca memoria ar fi avut un singur pin nCS ar fi fost necesar un inversor intre A16 si intrarea celui de-al doilea cip de memorie, A16 fiind legata direct la intrarea nCS a primului circuit. Deoarece sunt disponibile doua intrari de selectie circuit, unul activ jos si altul sus, decodificarea este mult mai simpla (figura 42). Pretul platit pentru aceasta simplitate este reducerea numarului de linii de selectie de la 3 in cazul initial la 1 la memoria extinsa.

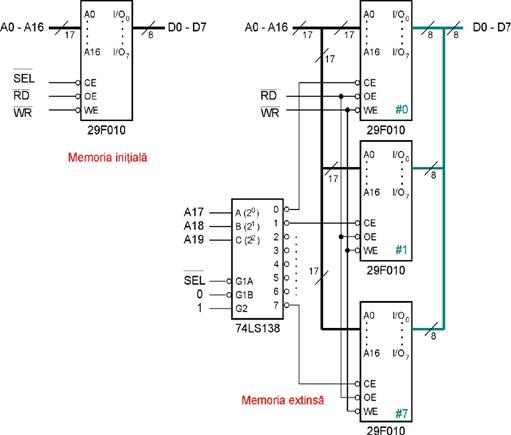

Exista situatii in care se doreste o extindere substantiala, de exemplu atunci cand se doreste realizarea unei memorii Flash de 1 Moctet utilizand 8 circuite 29F010 de 128 kocteti. In acest caz prezenta unui decodificator 3:8 este indispensabila. Pentru a dresa 1 Moctet sunt necesare 20 de linii de adresa, 17 mai putin semnificative fiind legate in paralel la cele 8 memorii Flash notate #0#7, cel 3 mai semnificative A17-A19 fiind intrari in DCD 3:8 74LS138. In acest caz memoria extinsa are aceleasi linii de control ca memoria initiala (nSEL, nOE, nWR, nRD) nemaifiind necesare alte modificari. Pentru schema electrica extinsa trebuie facute cateva comentarii:

a. Legarea liniei nRD la nOE este singura solutie posibila. Analizand diagramele de timp pentru memoria Flash rezulta ca mai intai uP emite o adresa pe liniile A0 - A19 care este decodificata. Datorita hazardului combinational propriu DCD, daca ar exista doar nCE, este posibil ca pentru intervale de timp scurte, de cativa tp, doua iesiri sau mai multe iesiri ale DCD sa fie simultan pe 0, validand accidental 2 sau multe memorii. Este putin probabil ca memoriile sa se distruga datorita unui singur conflict pe magistrala (bus contentition) de cateva zeci de ns, dar daca acest proces se repeta, el va conduce la incalzirea etajelor finale din memoriile Flash si in final la distrugerea lor. Prezenta celei de-a doua linie de selectie si legarea ei la nRD permite strobarea iesirii memoriilor la momente de timp bine definite si dupa stabilizarea iesirii DCD si memoriilor, ceea ce elimina complet problema mentionata.

b. In vederea reducerii in continuare a consumului, se poate inlocui circuitul 74LS138 cu varianta 74HCT138.

c. Linia nSEL poate fi legata la masa in cazul memoriei initiale, utilizarea ei reduce doar semnificativ consumul, aspect esential in cazul echipamentelor portabile, alimentate la baterii.

d. Linia nSEL poate fi utilizata similar in cazul memoriei extinse.

8.3. Extensia mixta

Cea mai complexa extindere este cea mixta. Pentru ilustrare vom considera doua implementari de memorii de 256 kcuvinte pe 12 biti, utilizand circuite SRAM de 1 Mb (organizare 128 kcuvinte de 8 biti, respectiv de 256 k cuvinte de 4 biti).

In ambele cazuri sunt necesare 3 circuite de memorie, iar al doilea caz este chiar simplu. Pentru primul caz se vor utiliza alternativ 128 kcuvinte de 8 biti din primul si 128 kcuvinte de 4 biti din al doilea circuit, respectiv 128 kcuvinte de 8 biti din al treilea circuit impreuna cu celelalte 128 kcuvinte de 4 biti din al doilea circuit. Cu alte cuvinte, al doilea circuit de memorie este divizat logic in doua jumatati, asociate celorlalte doua circuite (figura 44). Pentru a selecta care jumatate este utilizata, la iesirea memoriei #2 se foloseste un multiplexor cvadruplu 2:1, de tip 74LS15

La schema din figura 44 trebuie facute cateva observatii:

a. Inversorul de pe linia de adresa A17 poate lipsi daca se renunta la linia globala de selectie nCE.

b. Multiplexorul 74LS157 nu asigura transferul bidirectional al informatiei, el trebuie inlocuit cu circuite trei stari comandate de nRD si nWR pentru a putea asigura atat citirea cat si scrierea memoriei SRAM rezultate.

8. MEMORII SPECIALE

8.1. Memoria LIFO

8.2. Memoria FIFO

8.3. Memorii EEPROM seriale

8.4. Memorii SRAM pe magistrala I2C

9. APLICATII ALE MEMORIILOR

9.1. Memorii auxiliare

-Flash reader PC

9.2. Generatoare de functii (generatoare de semnal programabile)

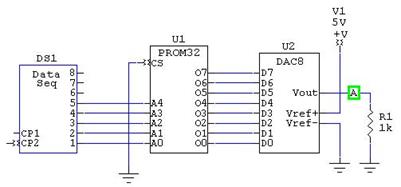

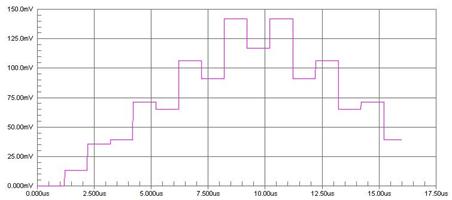

Descrierea functionarii

Figura 4x. Generator numeric de functii - schema de principiu.

Figura 4x. Generator numeric de functii - diagrame de semnal.

9.3. Implementarea functiilor logice

9.4. Automate programabile

9.5. Firmware

Memoriile ROM sunt cel mai adesea utilizate in microsisteme pentru stocarea programelor si a constantelor. Aceasta informatie se numeste firmware si este cea de-a trei componenta a unui sistem alaturi de hardware si software. Unele sisteme de calcul de dimensiuni reduse stocheaza in ROM interpretoare Basic (mai ales in cazul calculatoarelor de buzunar) sau sisteme de operare si aplicatii (WinCE, Word, Excel si altele in cazul dispozitivelor hand-held sau PDA). Sistemele cu microcontrolere moderne stocheaza codul firmware direct in memoria ROM a controlerului. Daca aceasta memorie este EEPROM sau Flash, reprogramarea ei este extrem de simpla si nu necesita extragerea circuitului din montaj (ce s-ar intampla daca la o revizie proprietarul unui autoturism scump ar vedea ca i se desface autoturismul pentru a extrage un circuit?). Tendinta prezenta este de a folosi memoria Flash interna a microcontrolerelor ca memorie de program, iar cea EEPROM ca memorie de date nevolatila. De obicei memoria EEPROM este de dimensiune mai mica decat cea Flash si uneori este necesara utilizarea unui EEPROM extern, de cele mai multe ori serial (de ce?)

9.6. Memoria bootstrap

Pentru majoritatea calculatoarelor sistemul de operare si aplicatiile se incarca in memoria RAM. Aceasta abordare permite alegerea sistemului de operare potrivit si a aplicatiilor dorite. Pentru incarcarea efectiva, calculatorul ruleaza un mic program aflat in memoria ROM, numit bootstrap (ceea ce in traducere libera inseamna a te trage in sus de propriile sireturi de la cizme). Este interesant de subliniat aici ca aceasta comportare o au si unele FPGA (cele produse de Xilinx sunt cel mai cunoscut exemplu), care la alimentare se configureaza conform unui cod exterior stocat intr-o memorie ROM.

9. Tabele de date

9.8. Convertoare de cod

Reprezinta un caz particular de implementare de functii.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 4405

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved