| CATEGORII DOCUMENTE |

Tehnici de detectie a erorilor

1. Introducere

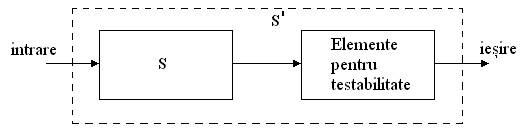

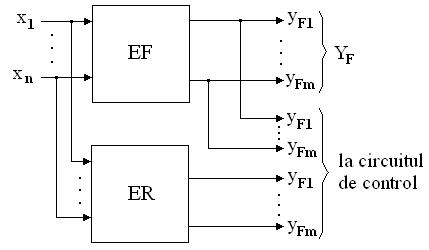

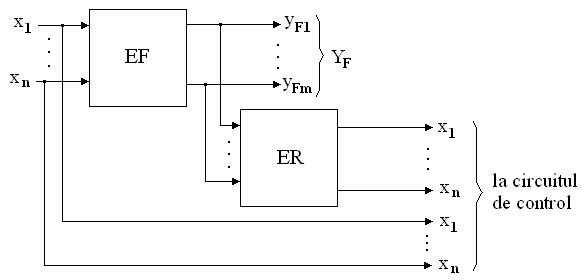

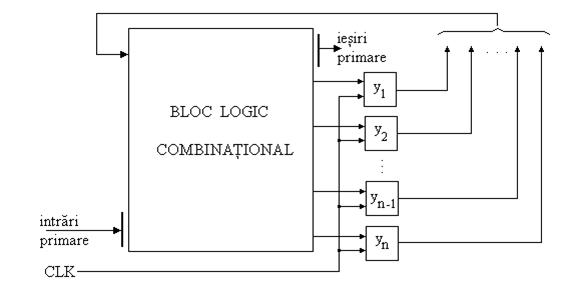

Evidentierea starii eronate a unui echipament, stare care se datoreaza fie erorilor de proiectare, fie defectarilor elementelor componente, se realizeaza prin introducerea in structura echipamentului a unor componente suplimentare (hardware sau software) urmand ca ulterior, celelalte faze ale tolerantei la defectare sa mascheze aceste erori sau defecte fizice. Astfel un echipament testabil contine pe langa elementele functionale de baza o serie de elemente pentru testabilitate (figura 1).

Fig. 1. Structura unui echipament testabil

In functie de scopul urmarit, testele aplicate echipamentelor se pot clasifica astfel:

Pentru realizarea in bune conditii a unei testari, elementele suplimentare introduse pentru asigurarea testabilitatii echipamentului, trebuie sa indeplineasca conditiile urmatoare:

In cazul echipamentelor tolerante la defectari detectia starilor eronate se poate face in doua moduri:

In functie de principiile care stau la baza generarii lor, aceste teste se pot clasifica astfel:

Teste sincrone, care se aplica atat modulelor hardware cat si software.

Teste de diagnostic, care se aplica de regula prin excitarea unei componente cu un set de semnale pentru care sunt cunoscute semnalele de iesire corecte, semnalele obtinute fiind comparate cu valorile asteptate.

Teste prin multiplicare, care constau in multiplicarea activitatii echipamentului testat. (Dublarea echipamentului original, copia functionand simultan. Rezultatul testului se obtine prin compararea iesirile obtinute).

Teste prin inversarea functiilor echipamentului. Acestea se pot utiliza pentru acele echipamente cu relatii intrare - iesire simple. (Ex. banda magnetica - se citesc apoi datele inscrise pe banda si se compara cu cele originale, codificatoare-decodificatoare).

Teste de paritate, utilizate pentru transmisii de date.

2. Metode de generare a secventelor de test utilizate

in diagnoza defectelor

Un test de diagnoza reprezinta succesiunea vectorilor (semnalelor) de intrare, aplicati la intrarile primare, impreuna cu vectorii (semnalele) de iesire, prezenti la iesirile primare ale echipamentului. Testele de diagnoza se pot clasifica in:

Testele functionale pot fi:

exhaustive - cand verifica toate combinatiile posibile;

partiale - verificarea facandu-se numai pentru combinatiile cele mai probabile in functionarea curenta a echipamentului;

statistice - secventele de test fiind date aleator cu o lege de repartitie uniforma.

Teste dinamice, care implica si verificarea timpului de raspuns si de comutatie in conditii reale de utilizare.

2.1. Metode de generare a secventelor de test

pentru circuite logice

In cazul echipamentelor compuse din module logice se pot utiliza urmatoarele tipuri de metode pentru generarea secventelor de test:

Metode deterministe: generarea secventelor de test prin analiza si simularea functiilor logice. Combinatia semnalelor de test la intrarile primare este impusa pe baza analizei structurii circuitului, iar prin schimbarea comportarii acestuia in prezenta anumitor defectari se determina defectarile susceptibile de a fi puse in evidenta cu secventa de test respectiva la intrarile primare.

A) Simularea deductiva. Aplicarea acestei metode consta in partitionarea echipamentul in circuite elementare si disjuncte functional, dezvoltand in continuare o combinatie de teste pentru fiecare dintre circuitele elementare, pe baza logicii circuitului. Metoda este utila pentru circuitele simple, dar nu este indicata pentru circuitele complexe.

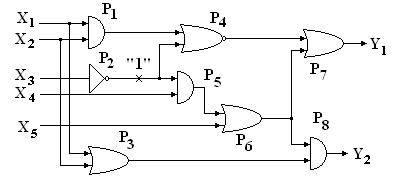

Exemplu: Metoda caii sensibile Aceasta metoda consta in alegerea catorva cai de propagare de la un punct de manifestare a defectului spre iesirile circuitului.

Fig. 2. Cale sensibila la propagarea unui defect

Daca se considera ca defectul se

manifesta la iesirea portii ![]() , atunci calea sensibila va fi formata din

portile

, atunci calea sensibila va fi formata din

portile ![]() , astfel stabilite incat semnalele de la iesirea

oricarei porti

, astfel stabilite incat semnalele de la iesirea

oricarei porti ![]() sa fie

determinate numai de catre semnalul de intrare care vine de la poarta

sa fie

determinate numai de catre semnalul de intrare care vine de la poarta ![]() (figura 2). In acest

fel, semnalul de la iesirea portii

(figura 2). In acest

fel, semnalul de la iesirea portii ![]() va fi dedus doar din

observarea semnalului de la iesirea portii

va fi dedus doar din

observarea semnalului de la iesirea portii ![]() . Semnalele de intrare pentru poarta

. Semnalele de intrare pentru poarta ![]() se deduc in

functie de semnalele impuse iesirii portii

se deduc in

functie de semnalele impuse iesirii portii ![]() .

.

Problema testarii in cazul in acestei metode se poate formula astfel: avand un set de cai sensibile trebuie gasita o combinatie de semnale la intrarile primare care va realiza toate intrarile necesare acestei cai de porti.

Se considera ca iesirea portii ![]() (figura 3) este

blocata, in "1". Semnalul

(figura 3) este

blocata, in "1". Semnalul ![]() va pune in evidenta

defectarea portii

va pune in evidenta

defectarea portii ![]() . Iesirea

. Iesirea ![]() daca defectul

este absent si

daca defectul

este absent si ![]() daca defectul

este prezent.

daca defectul

este prezent.

Fig.3.Circuit utilizat pentru exemplificarea metodei caii sensibile

In prima etapa se alege arbitrar calea de porti

logice ![]() de la

de la ![]() la iesire. Pentru

ca aceasta cale sa fie o cale sensibila la propagarea defectului

trebuie indeplinite conditiile:

la iesire. Pentru

ca aceasta cale sa fie o cale sensibila la propagarea defectului

trebuie indeplinite conditiile:

![]() , pentru a sensibiliza poarta

, pentru a sensibiliza poarta ![]() ;

;

![]() , pentru a sensibiliza poarta

, pentru a sensibiliza poarta ![]() ;

;

![]() , pentru a sensibiliza poarta

, pentru a sensibiliza poarta ![]() .

.

In etapa a doua se gaseste vectorul test la nivelul intrarilor primare, astfel:

- din etapa

I avem: ![]() si

si ![]() ;

;

- pentru ca ![]() trebuie ca x1=1

si x2=0, sau x1=0 si x2=1, sau x1=1

si x2=1.

trebuie ca x1=1

si x2=0, sau x1=0 si x2=1, sau x1=1

si x2=1.

Se obtine vectorul de test: ![]() , care identifica defectarea.

, care identifica defectarea.

Pentru ![]() defectul este prezent,

defectul este prezent,

![]() indicand absenta

defectarii considerate. Defectarea nu se observa la iesirea

indicand absenta

defectarii considerate. Defectarea nu se observa la iesirea ![]() , deoarece calea

, deoarece calea ![]() nu este sensibila

la propagarea defectarii considerate. Pentru

nu este sensibila

la propagarea defectarii considerate. Pentru ![]() si

si ![]() rezulta

rezulta ![]() atunci cand defectul este prezent si pentru

atunci cand defectul este prezent si pentru ![]() si

si ![]() rezulta

rezulta ![]() , cand defectul nu este

prezent.

, cand defectul nu este

prezent.

Metoda caii sensibile nu conduce intotdeauna si pentru orice tip de circuit logic la un test de diagnostic.

B) Generarea secventelor de test pe principii probabilistice

Detectarea erorilor/defectelor se bazeaza in acest caz pe natura aleatoare si pe numarul foarte mare al vectorilor de test.

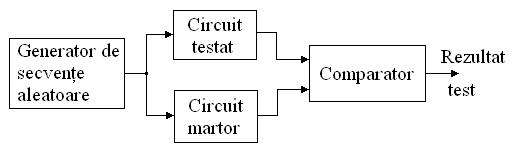

Metoda generarii aleatoare a testelor

Fig. 4. Structura utilizata pentru realizarea testarii cu secvente aleatoare.

Intrarile circuitului testat si cele ale unui circuit martor sunt baleiate in paralel in momentul efectiv al testarii de catre secventele de test generate aleator. Semnalele de iesire ale celor doua circuite sunt comparate: in caz de divergenta a celor doi vectori ai semnalelor de iesire, circuitul testat este considerat defect. Secventele de detectie obtinute permit stabilirea unui dictionar al defectarilor pentru circuitul respectiv si, de aceea, procedeul poate fi considerat autoinstruibil.

Metoda simularii Monte-Carlo

Metoda consta intr-o analiza cu ajutorul unei simulari a defectarilor de detectat. Semnalele de intrare sunt obtinute aleator, cu o subrutina de generare aleatoare a numerelor 0 si 1.

Se determina apoi, cu ajutorul unui simulator de circuite logice cu injectie de defectari, abilitatea fiecarui vector de test de a detecta diferitele defectari din circuit, conform unei liste de defectari. Se considera N circuite ce sunt simulate si care sunt comparate cu un circuit martor. La fiecare neconcordanta a semnalelor de iesire se evidentiaza combinatia semnalelor test necesara diagnosticarii unui defect.

Aceasta metoda de generare a secventelor de test poate consuma foarte mult timp atunci cand se cere detectarea tuturor defectarilor posibile intr-un echipament, iar in unele cazuri nu este posibila diagnosticarea tuturor defectarilor. De aceea este indicat sa se combine metodele aleatoare de generare a secventelor de test cu metodele deterministe.

2.2. Strategii de elaborare a secventelor de test

pentru echipamentele mari

In cazul echipamentelor mari, datorita volumului foarte mare de informatie ce trebuie prelucrat la un moment dat si eterogenitatii echipamentelor, nu se pot utiliza aceleasi teste ca in cazul circuitelor logice. Echipamentele mari au de regula o structura complexa, continand unitati diferite: electronice, electromecanice, unitati de adaptare etc.

Datorita eterogenitatii, in cazul echipamentelor mari se pot aplica doar teste de tip functional. Echipamentul complex este partitionat in module functionale, pentru fiecare modul se genereaza secventele de test si apoi se compun aceste secvente pentru ansamblul general.

Este necesar ca generarea testelor sa se realizeze la nivelul fiecarui modul si sa ia in considerare compunerea acestor module in structura echipamentului, deoarece nu este intotdeauna posibila propagarea spre iesire a oricarei secvente de semnale care contin o informatie in vederea diagnosticarii unui defect. Rezulta ca eficacitatea testului este determinata de modul alegerii modulelor componente ale echipamentului considerat.

Partitionarea unui echipament se poate face in doua moduri:

In generarea secventelor de test pot fi evidentiate strategiile de mai jos.

I. Elaborarea de teste dupa principiul start-small

|

In acest caz testarea incepe cu cel mai mic modul posibil din echipament, fiecare test suplimentar adaugand apoi un nou modul pentru testare (figura 5). Cu toate ca procedura stabilirii succesiunii testelor individuale este complexa, exista insa doua avantaje:

|

Fig. Principiul start-small |

Dificultatile care apar sunt legate de gasirea decupajului adecvat si de ordonarea circuitelor rezultate in vederea optimizarii testarii lor.

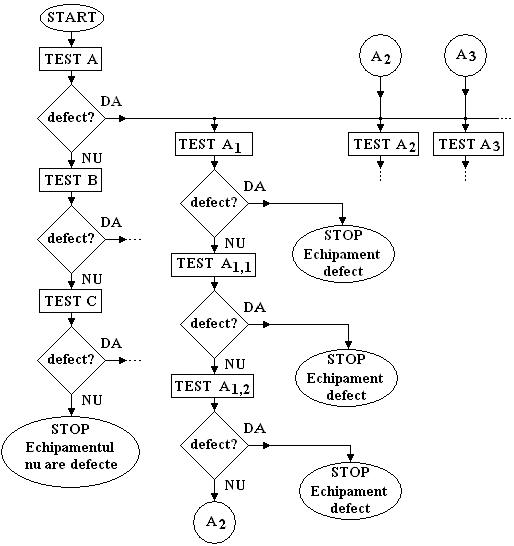

II. Elaborarea de teste dupa principiul start-big

Testul se aplica la inceput unei portiuni mari din echipament si in caz de buna functionare se continua cu o alta unitate mare. In caz de detectie a unei defectari se procedeaza la o ramificare a testelor pentru a se diagnostica module din ce in ce mai mici in scopul de a se putea ajunge la identificarea defectarii. Avantajul acestei abordari consta in aceea ca nu este necesar un decupaj strict al echipamentului, nici o ordonare precisa a testelor, insa algoritmii de diagnosticare sunt mai complicati. Ramificarea testelor se face pana se ajunge la cea mai mica parte sau componenta inlocuibila sau reparabila.

Fig. 6. Algoritmul de testare start-big

3. Metode de derulare a testelor

Metodele de derulare a testelor pentru echipamentele digitale se pot clasifica in secventiale si combinationale. In cazul metodei de testare secventiala, cel de-al i - lea vector de test este determinat pe baza raspunsurilor la cei i - 1 vectori de test anteriori. In cazul testarii combinationale, cel de-al i - lea vector de test este independent de vectorii test anteriori [2].

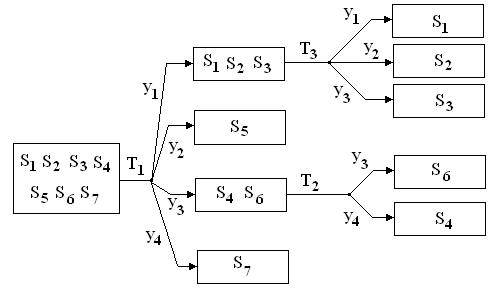

I. Metoda testarii secventiale

Se considera un echipament partitionat in

sapte module identice ![]() , carora li se aplica trei secvente de test

, carora li se aplica trei secvente de test ![]() rezultand patru tipuri

de semnale raspuns: y1, y2 , y3, y4

(tabelul 1).

rezultand patru tipuri

de semnale raspuns: y1, y2 , y3, y4

(tabelul 1).

Se obtine un arbore de diagnostic in care fiecare defectare corespunde unei ramuri, dar nu in mod necesar si invers, terminatiile ramurilor corespund locurilor unde s-a oprit testarea, cand s-a identificat o defectare (figura 7).

In cazul analizat s-a cunoscut apriori faptul ca modulul S1 este in stare buna de functionare si, prin conventie, a fost plasat pe ramura superioara a arborelui.

Tabelul 1

|

Test |

Raspuns | ||||

|

y1 |

y2 |

y3 |

y4 |

||

|

T1 |

S1S2S3 |

S5 |

S4S6 |

S7 |

|

|

T2 |

S1S2S3 |

S5S7 |

S6 |

S4 |

|

|

T3 |

S1 |

S2S4S5 S6S7 |

S3 | ||

Prin aplicarea testului ![]() s-a obtinut o

partitionare in patru clase a celor sapte module in functie de

semnalele de iesire

s-a obtinut o

partitionare in patru clase a celor sapte module in functie de

semnalele de iesire ![]() . Pentru repartizarea ulterioara a claselor

. Pentru repartizarea ulterioara a claselor ![]() si

si ![]() este necesar sa

se utilizeze testele

este necesar sa

se utilizeze testele ![]() si

si ![]() . Se ajunge astfel la identificarea intr-un mod unic a unui echipament,

deci la un procedeu de testare cu rezolutie de diagnosticare maxima. Dupa

fiecare test, aplicarea testului urmator se face in functie de

rezultatele obtinute anterior. In mod uzual se adopta testul care

furnizeaza cea mai mare cantitate de informatie.

. Se ajunge astfel la identificarea intr-un mod unic a unui echipament,

deci la un procedeu de testare cu rezolutie de diagnosticare maxima. Dupa

fiecare test, aplicarea testului urmator se face in functie de

rezultatele obtinute anterior. In mod uzual se adopta testul care

furnizeaza cea mai mare cantitate de informatie.

Fig. 7. Arborele de diagnostic in cazul testarii secventiale

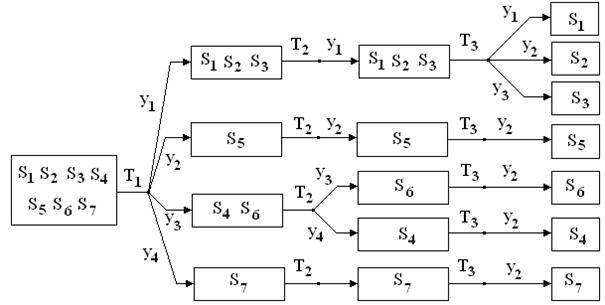

II. Metoda testarii combinationale

Aceasta metoda conduce la o crestere a numarului de teste, dar necesita o memorie mai redusa pentru stocarea datelor obtinute. Redundanta proprie acestei metode de testare poate conduce la detectarea unor defectari care nu au fost considerate printre defectarile posibile la generarea testelor, ceea ce compenseaza timpul mai mare necesar testarii.

Aplicarea testelor intr-o ordine prestabilita conduce

la un dictionar al defectarilor. Se considera exemplul anterior

si se aplica succesiv testele ![]() rezultand graful din

figura 8:

rezultand graful din

figura 8:

Fig. 8. Arborele de diagnostic in cazul testarii combinationale

In urma aplicarii tuturor testelor de diagnoza intr-o ordine prestabilita, se obtine un arbore de diagnoza, iar dictionarul de defectari rezultat este prezentat in tabelul 2.

Tabelul 2

|

Echipamente |

Raspunsuri la testele: |

Obs. |

||

|

T1 |

T2 |

T3 |

||

|

S1 |

y1 |

y1 |

y1 |

S1- bun |

|

S2 |

y1 |

y1 |

y2 |

S2- defect |

|

S3 |

y1 |

y1 |

y3 |

S3- defect |

|

S4 |

y3 |

|

y2 |

S4- defect |

|

S5 |

y2 |

y2 |

y2 |

S5- defect |

|

S6 |

y3 |

y3 |

y2 |

S6- defect |

|

S7 |

y4 |

y2 |

y2 |

S7- defect |

Deoarece numarul de combinatii ale semnalelor care detecteaza defectarile variaza de la o defectare la alta, prin ordonarea combinatiilor semnalelor de test in sensul descresterii numarului de defectari detectate, devine posibila terminarea testarii intr-un timp mai scurt.

Cu toate ca are inconvenientul necesitatii de a memora rezultatele intermediare, metoda testarii secventiale are avantajul de a fi mai rapida intrucat sunt aplicate numai combinatiile de test necesare. Metoda testarii combinationale nu necesita memorarea rezultatelor testelor insa este de durata mai lunga intrucat trebuie executate toate testele, chiar daca a fost identificata o defectare.

4. Echipamente autotestabile

Procedeul autotestarii constituie baza implementarii tolerarii dinamice a defectarilor. Functia de autotestabilitate trebuie sa fie inclusa atat in echipamentele autoreparabile, cat si in cele reconfigurabile [2].

Implementarea echipamentelor tolerante la defectari presupune realizarea unor structuri autotestabile cu o siguranta in functionare foarte ridicata. Se defineste echipamentul total autotestabil ca fiind echipamentul autotestabil si sigur in prezenta defectarilor.

Un echipament autotestabil total, relativ la o anumita multime de defectari are proprietatile urmatoare:

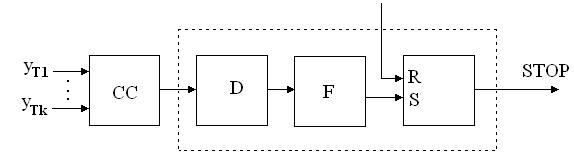

Supravegherea unui echipament autotestabil poate fi realizata de un echipament de detectie a defectarilor conectat la iesirile de test (figura 9).

Acest echipament de supraveghere va forma semnalul de alarma sau STOP si va actiona comutarea rezervelor echipamentului sau reconfigurarea sa, atunci cand echipamentul are o structura redundanta dinamica, sau va actiona asupra altui echipament de decizie.

|

|

Fig. 9. Echipament autotestabil |

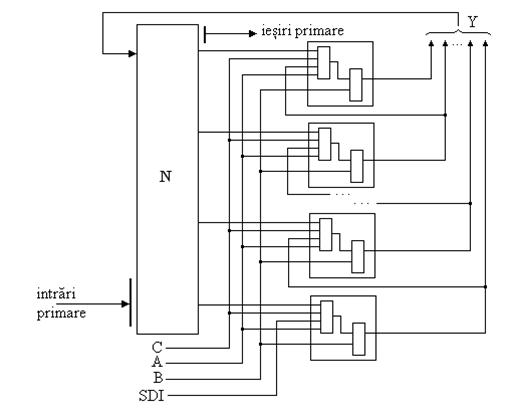

Structura unui circuit de detectie a defectarilor este

cu atat mai complicata cu cat numarul variabilelor de test ![]() este mai mare. Schema

bloc prezentata in figura 10 este compusa dintr-un circuit de control

(CC) si un circuit pentru formarea semnalelor de ALARMA sau STOP.

este mai mare. Schema

bloc prezentata in figura 10 este compusa dintr-un circuit de control

(CC) si un circuit pentru formarea semnalelor de ALARMA sau STOP.

Fig.10. Circuit de detectie a defectarilor

Circuitul de control trebuie sa indeplineasca conditiile urmatoare:

toate semnalele de test ale echipamentului autotestabil controlat trebuie sa fie observabile la iesirea sa;

orice defectare care apare in functionare trebuie sa fie detectata in cursul functionarii sale normale.

Circuitul de formare a semnalului de ALARMA sau STOP trebuie sa aiba in compunere urmatoarele elemente:

un circuit de detectie D, care sa detecteze configuratia semnalelor de test care nu apartin unei stari de buna functionare;

un filtru F, pentru a fi eliminate eventualele configuratii tranzitorii;

un circuit care sa asigure memorarea erorii detectate de circuitul D, de exemplu un circuit basculant bistabil de tip RS.

Utilizarea filtrului F nu mai este necesara atunci cand circuitul de detectie este sincronizat de un semnal de tact. Realizarea unui echipament autotestabil poate fi conditionata de aparitia anumitor tipuri de defectari apriori considerate, functie de tipul de aplicatie avut in vedere pentru echipamentul respectiv si tehnologia de fabricatie folosita.

Echipamentele total autotestabile pot fi clasificate dupa tipul redundantei utilizate, in:

A) Echipamentele total autotestabile cu structura redundanta separabila, se pot imparti la randul lor astfel:

a1) Echipamente autotestabile cu structura dublata (figura 11).

Fig. 11. Echipament autotestabil cu structura dublata

Modulul redundant este identic cu cel functional. Semnalele de iesire sunt trimise la circuitul de control, care in caz de necoincidenta va genera semnalul de ALARMA sau STOP. Structura este simpla si se poate aplica oricarui echipament. Pentru a evita erorile de proiectare care ar putea afecta in acelasi mod cele doua module este de preferat ca modulul redundant sa fie realizat cu o alta schema dar sa indeplineasca aceleasi functii ca modulul functional. Apar probleme de sincronizare intre cele doua module si probleme legate de costul ridicat al solutiei.

a2) Echipamente autotestabile cu inversarea functiei intrare/iesire (figura 12).

Fig. 12. Echipament autotestabil cu inversarea functiei intrare/iesire

Aceasta solutie nu se poate aplica decat pentru echipamente cu functii I/E simple, pentru care se poate determina functia inversa a modulului functional (ex. codificatoare - decodificatoare etc).

Costul unui astfel de echipament poate depasi dublul costului echipamentului de baza. Apar probleme de sincronizare, intrucat timpii de propagare prin cele doua module sunt diferiti.

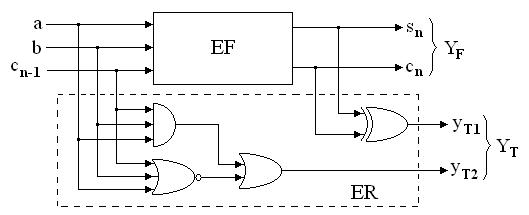

a3) Echipamente autotestabile cu coduri detectoare de erori (figura 13).

Fig. 13. Echipament autotestabil cu coduri detectoare de erori

Modulul redundant (reprezentat cu linie intrerupta) al echipamentului autotestabil considerat realizeaza o codare a semnalelor de intrare si iesire ale modulului functional.

In figura 13 este prezentat un echipament cu intrarile ![]() si iesirile

si iesirile ![]() . Blocul de formare a semnalelor de test formeaza

semnalele

. Blocul de formare a semnalelor de test formeaza

semnalele ![]() astfel incat

astfel incat ![]() pentru o

functionare normala si

pentru o

functionare normala si

![]() in prezenta unor

defectari in echipamentul functional.

in prezenta unor

defectari in echipamentul functional.

B) Echipamente autotestabile cu structura redundanta neseparabila. Acestea includ echipamentele autotestabile sintetizate pe baza utilizarii codurilor redundante de tip neseparabil pentru codarea informatiilor de intrare iesire. Exemplu: echipamentele ce utilizeaza codul k din n. Aceste echipamente vor avea un pret de cost mai redus fata de echipamentele autotestabile cu structura dubla.

Metode de asigurare a unei testabilitati facile

Testabilitatea unui echipament constituie aptitudinea acestuia de detectare si localizare usoara a defectarilor posibile. Aceasta inseamna ca echipamentul poseda o colectie de teste usor de generat, aplicat si evaluat, care permit obtinerea unei localizai precise a defectarilor. Testabilitatea se realizeaza in faza de proiectare, regulile de proiectare urmarind sa creasca controlabilitatea si observabilitatea echipamentelor respective.

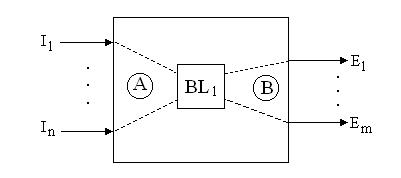

O metoda generala de a produce programe de test pentru circuitele electronice consta in a verifica functional fiecare bloc identificabil in circuitul respectiv. Fie un circuit logic complex de tip integrat, reprezentat in figura 14:

Fig. 14. Circuit integrat complex

Daca se considera blocul BL1, stabilirea unor configuratii de semnale pentru testare pe intrarile sale presupune posibilitatea controlarii valorilor logice ale nodurilor de retea din regiunea A prin intermediul vectorilor de test aplicati pe intrarile primare I1 In.

Masura in care este posibila asigurarea de valori logice bine definite unui nod al retelei, prin intermediul vectorilor aplicati pe intrarile primare, poarta numele de controlabilitate a nodului respectiv.

Daca se rezolva problema configuratiilor logice necesare pentru intrarile blocului logic testat, ramane in continuare sa se rezolve problema observarii iesirilor acestuia, intrucat nu intotdeauna acestea pot fi in contact direct cu iesirile primare. Rezolvarea acestei probleme presupune stabilirea unor cai de comunicatie prin zona B intre iesirile blocului testat si iesirile primare ale echipamentului.

Masura in care comportarea unui nod al retelei logice poate fi transmisa catre una dintre iesirile primare se numeste observabilitatea nodului respectiv.

Proiectarea circuitelor testabile se bazeaza pe doua metode:

Prima metoda porneste de la proiectarea existenta si introduce elemente logice aditionale, ceea ce conduce la o crestere a complexitatii circuitului, dar reduce numarul de teste necesare pentru diagnoza. Aceasta metoda se poate aplica pentru rezolvarea problemelor de testabilitate la nivelul de placi de circuite imprimate echipate cu componente si echipamente, prin introducerea unor puncte de test suplimentare.

A doua metoda consta in proiectarea circuitelor astfel incat sa fie usor testabile. Aceasta metoda poate introduce intarzieri mari in propagarea semnalelor si o crestere a numarului de porti logice.

In cazul circuitelor integrate, unde numarul terminalelor este limitat nu se pot introduce puncte de test suplimentare decat, cel mult, in faza de fabricatie.

Pentru implementarea primei metode in cazul circuitelor LSI sau VSLI se poate opta pentru generarea in circuit a unor secvente de test pseudoaleatoare [2].

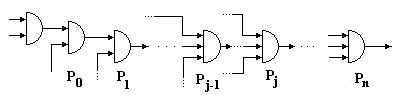

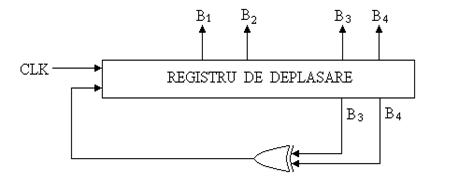

Generarea vectorilor de test poate fi facuta utilizand un registru de deplasare cu bucle de reactie ce extrag informatia din diferite puncte ale registrului si o transporta la intrarea acestuia, structura unui astfel de registru fiind prezentata in figura 1 (LFSR - Linear Feedback Shift Register).

Fig. 1 Generarea vectorilor de test utilizand registre de deplasare.

Metoda este simpla, usor de implementat si permite obtinerea prin metode nedeterministe a unui numar mare de vectori de test, de = 2n-1.

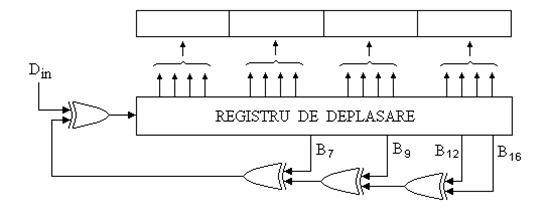

Metodele de analiza a rezultatelor aplicarii secventei de test constau fie in numararea tranzitiilor, fie in analiza de semnatura (figura 16).

Fig. 16. Implementarea metodei analizei de semnatura

utilizand un registru de tip LSFR

In cazul metodei analizei de semnatura, elementul

constructiv fundamental este un LFSR,

caruia i se aplica la intrare printr-o poarta SAU-EXCLUSIV doua surse de

informatie: sirul de m

biti rezultati in urma aplicarii secventei de test si

sirul de semnale de pe bucla de reactie realizata cu prize de

semnal in diferite puncte ale registrului.

Figura 3

La terminarea secventei de

test, LFSR contine un cuvant de n biti care poarta denumirea

de semnatura a

sirului de m biti prelucrati.

Cea de a doua metoda presupune utilizarea tehnicii de proiectare LSSD (Level Sensitive Scan Design), folosita cu precadere pentru circuitele electronice integrate de tip LSI sau VLSI. Implementarea acestei metode se bazeaza pe urmatoarele concepte:

Circuitul functioneaza sincron. Toate schimbarile de stare a circuitului sunt determinate de nivelul logic al semnalului de test si nu de fronturile acestuia. De asemenea, starile stabile aparute ca raspuns la modificarile semnalelor de intrare sunt independente de intrarile datorate propagarilor pe caile de transfer (interconexiuni, porti etc.).

Raspunsul este independent de ordinea in care se produc schimbarile semnalelor de intrare in cadrul aceleiasi perioade de tact. Aceasta proprietate de sensibilitate la nivel reduce dependenta circuitului de parametrii sai de curent alternativ: degradarea fronturilor, intarzieri de propagare etc.

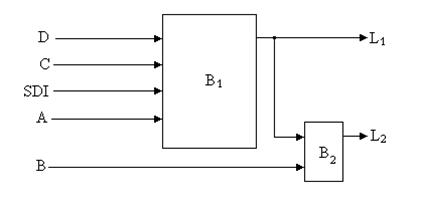

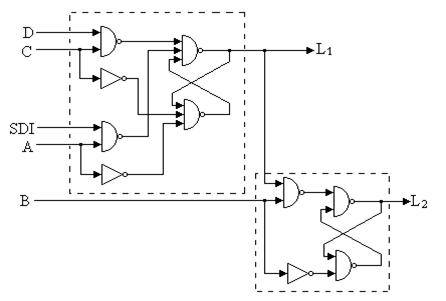

Circuitul trebuie sa posede cai de acces serial. Pentru aceasta se folosesc structuri logice special proiectate in acest scop, de tip SRL (polarity - Hold Shift Register Latch), a caror schema bloc este prezentata in figura 17, iar schema electrica la nivel de porti logice este data in figura 18.

Fig. 17. Schema bloc a unei structuri SRL

In figura 17, blocurile B1 si B2 reprezinta doua circuite bistabile conectate in configuratie master-slave.

Bistabilul B1 constituie dispozitivul de memorare a starii echipamentului in functionare normala, avand intrarea de date pe D, semnalul de tact al echipamentului pe intrarea C si iesirea pe L1. Pe perioada functionarii normale, semnalele "Scan Clock A" si semnalele de tact pe B sunt fixate in "0". Memorarea datelor din echipament se realizeaza la revenirea in "0" a semnalului de tact.

Pentru a configura aceasta structura ca element al unei cai de acces serial semnalul de tact pe intrarea C trebuie blocat in "0" actionandu-se asupra intrarii A. Ca urmare, valoarea logica existenta pe intrarea SDI se incarca in bistabilul L1, la revenirea in "0" a intrarii A. Transferarea acestei informatii in bistabilul L2 se realizeaza la revenirea in "0" a semnalului de tact aplicat pe intrarea B.

Fig. 18. Schema electrica a structurii SRL, la nivel de porti logice

Realizarea unei testari automate in tehnica LSSD presupune urmatoarele etape:

a) se testeaza registrele SRL, transferandu-se in mod serial o secventa logica cunoscuta.

b) se testeaza blocurile combinationale, transferandu-se la intrarea lor vectorii de test necesari prin intermediul unui registru de deplasare.

c) se citeste vectorul semnalelor rezultate la iesirea blocului combinational, extragandu-se informatia in mod serial prin intermediul registrului de deplasare.

d) se repeta actiunile de la punctele b si c pana la expirarea programului de test.

Exemplu de utilizare a tehnicii LSSD pentru implementarea autotestabilitatii. In figura 19 este prezentat modul in care se poate descompune un circuit complex in vederea testarii automate, iar in figura 20 este prezentata utilizarea structurilor de tip SRL.

Fig. 19. Structura unui circuit complex

Fig. 20. Utilizarea structurilor SRL pentru implementarea autotestabilitatii

Avantajele tehnicii de proiectare ce utilizeaza structuri LSSD:

Dezavantajele tehnicii de proiectare ce utilizeaza structuri LSSD:

Aceasta tehnica de proiectare permite cresterea observabilitatii si controlabilitatii circuitelor integrate de tip LSI si VLSI, ceea ce permite utilizarea acestor structuri in echipamentele de inalta fiabilitate si, in special, in echipamentele tolerante la defectari.

6. Probleme specifice ale tehnicilor de implementare a tolerantei la defectari

In implementarea tolerantei la defectari au fost prezentate doua strategii de baza: redundanta statica si redundanta dinamica.

Tehnicile de redundanta statica, aplicate la nivel hardware, se refera la utilizarea unor componente suplimentare care formeaza o parte permanenta a echipamentului si servesc la mascarea semnalelor eronate generate de prezenta unor defectari.

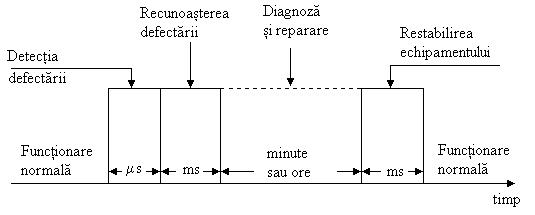

Tehnicile de redundanta dinamice tolereaza defectarile prin reorganizarea activa a echipamentului la aparitia acestora, astfel incat o componenta defecta este inlocuita efectiv de o componenta aflata in buna stare de functionare. Aceasta operatie este realizata in trei etape, asa cum rezulta si din diagrama din figura 21, [2].

In prima etapa se realizeaza detectia defectarii echipamentului. Procedeele de test folosite urmaresc sa detecteze defectul si sa-l izoleze la o unitate inlocuibila sau reparabila.

In etapa a doua se produce inlaturarea defectului prin repararea, inlocuirea modulului defect cu unul de rezerva sau reconfigurarea echipamentului in jurul modulului defect.

Fig. 21. Etapele tolerarii dinamice a defectarilor

In etapa a treia se realizeaza revenirea echipamentului la o stare functionala parcursa de acesta inainte de manifestarea defectului, dupa care operarea echipamentului este reluata din acel punct.

In general, orice procedeu de restabilire a functionarii unui echipament consta din urmatoarele etape:

De cele mai multe ori, detectia defectului / erorii este o functie realizata integral de o varietate de procedee implementate cu mijloace hardware. In toate cazurile, testele de detectie sunt examinate de programe care asigura validarea lor.

Obiectivul recunoasterii defectului / erorii consta in identificarea modulului functional la nivelul caruia s-a produs defectul / eroarea, precum si in discriminarea defectelor hardware permanente de cele tranzitorii.

Desfasurarea pasului urmator are in vedere existenta sau nu a unei rezerve a modulului functional identificat ca defect. In cazul in care nu exista o rezerva disponibila, se initializeaza actiunile de diagnosticare si reparare a modulului defect.

Operarea normala a echipamentului, intrerupta in momentul detectiei defectului / erorii, este suspendata si pe perioada de diagnoza si reparare. Dupa terminarea repararii se executa restabilirea functiilor echipamentului si se reia functionarea normala.

Evenimentele ce se deruleaza in acest caz sunt prezentate in diagrama din figura 22.

Fig. 22. Etapele procesului de restabilire a functionarii unui echipament

de calcul neredundant in cazul aparitiei unei defectari

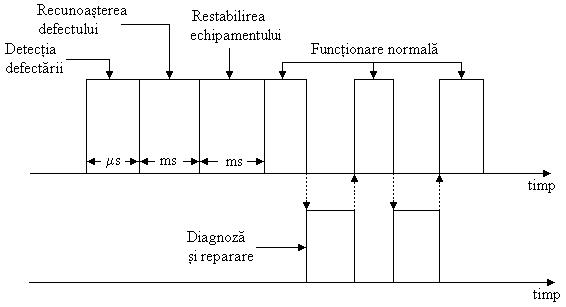

In cazul in care exista o rezerva disponibila, atunci dupa recunoasterea defectarii se procedeaza la reconfigurarea echipamentului prin inlocuirea modulului defect cu cel de rezerva si apoi se initiaza un procedeu de restabilire a functionarii echipamentului, reluandu-se functionarea normala.

Diagnoza si repararea modulelor functionale defecte se poate face mai tarziu, in timpul functionarii normale a echipamentului. Evenimentele ce se succed in acest caz sunt reprezentate in diagrama din figura 23.

O analiza a secventelor prezentate in figurile 22 si 23 pune in evidenta o serie de avantaje in ceea ce priveste mentenanta echipamentelor tolerante la defectari.

In primul rand, diagnosticarea unei defectari, care consuma mai mult timp decat toate etapele procedeului de restabilire a functionarii, poate fi amanata si intercalata cu functionarea normala a echipamentului. In al doilea rand, disponibilitatea unei rezerve permite abordarea unei metode de diagnosticare prin comparatie cu avantajul unui timp de diagnoza si cost scazut.

Fig. 23. Etapele procesului de restabilire a functionarii unui echipament

de calcul redundant in cazul aparitiei unei defectari

Fiind mai complexe decat metodele redundantei statice, procedeele redundantei dinamice prezinta avantajul ca modulele defecte, dupa ce au fost localizate sunt rapid eliminate, fiind inlocuite cu modulele bune, in timp ce in cazul redundantei statice, defectarile nedetectate se acumuleaza pana ce echipamentul se defecteaza complet.

Echipamentele de calcul moderne sunt proiectate ca echipamente distribuite, de tip multiprocesor, oferind performante superioare din punct de vedere al tolerarii defectarilor si al vitezei de calcul. In cazul defectarii unui calculator, calculatoarele ramase in echipamentul distribuit, detecteaza erorile cu ajutorul echipamentului software disponibil si reconfigureaza corespunzator echipamentul. Daca echipamentul este uniprocesor, detectia si restabilirea se realizeaza cu mijloace hardware auxiliare, intrucat nu este indicat ca astfel de operatii sa fie executate de software-ul calculatorului defect.

In cazul echipamentelor multiprocesor apar probleme legate de sincronizarea semnalelor, datorita intarzierilor diferite introduse.

Exemplu: Daca un procesor este deconectat datorita identificarii unei defectari, celelalte procesoare din structura echipamentului vor "sti" acest lucru numai dupa receptionarea mesajului de intrerupere de catre fiecare dintre ele, astfel incat in timpul tranzitiei mesajului respectiv celelalte procesoare pot trimite mesaje catre procesorul deja deconectat.

7. Tehnici de reconfigurare a echipamentelor

la aparitia defectarilor

Aceste tehnici au rolul de a asigura localizarea elementelor defecte, eliminarea sau izolarea acestora si introducerea automata a unor rezerve. De regula aceste tehnici sunt implementate hardware.

In cazul echipamentelor tolerante la defectari, localizarea defectarilor se face cel mai adesea utilizand teste de diagnoza.

Aceste teste implica aplicarea la intrarile primare a unor seturi de semnale pentru care sunt cunoscute seturile de semnale de iesire corecte. Neconcordanta dintre vectorul semnalelor de iesire obtinut si cel asteptat pune in evidenta un anume defect in echipament.

Testele de diagnoza se folosesc de regula pentru localizarea defectelor de tip hardware, dar se pot folosi si pentru produsele software.

In cazul unui echipament tolerant la defectari pentru comutatie electronica ESS No 1A (Electronic Switching System) realizat de firma Bell se utilizeaza doua procesoare, unul activ si unul de rezerva. Detectia initiala a unei defectari se face prin evidentierea unor neconcordante intre iesirile celor doua procesoare. In etapa urmatoare se determina care procesor este defect printr-un test de diagnoza, unitatea defecta fiind eliminata din echipament. Se aplica apoi teste de diagnoza unitatii defecte pana ce se izoleaza defectul la cea mai mica componenta inlocuibila, dupa care se trimite un mesaj catre operatorul uman care va efectua inlocuirea componentei / modulului specificate, cu una de rezerva [2].

In cazul altor echipamente tolerante la defectari, proiectarea a fost astfel facuta incat permite scoaterea unor componente din functionarea curenta, aplicarea unor teste de diagnoza si, in caz de buna functionare, reintroducerea lor in echipament.

Pentru a reduce costul realizarii testelor de diagnostic in echipamentele cu structura redundanta se pot folosi comparatiile intre semnalele de iesire ale diferitelor componente din structura echipamentului care realizeaza aceleasi functii. Rezultatele obtinute pentru un element al echipamentului suspectat a fi defect sunt comparate cu rezultatele elementului identic din alta copie a echipamentului considerat in buna stare de functionare.

In urma etapei de localizare a defectarilor, una sau mai multe componente ale echipamentului vor fi considerate ca defecte. Pentru a preveni ca aceste componente suspecte sa influenteze viitoarea functionare a echipamentului trebuie luate masuri de "reparare" a echipamentului. Se considera ca "repararea" echipamentului nu implica operatii de "reparare" propriu-zisa a componentelor (modulelor) defecte ci numai actiuni de reconfigurare a echipamentului care sa conduca la aducerea echipamentului intr-o stare de buna functionare.

Tehnicile de reconfigurare se pot clasifica in:

Reconfigurarea manuala consta din modificarea manuala a conexiunilor intre componente sau inlocuirea pe aceeasi cale a componentelor defecte.

Tehnicile de reconfigurare dinamica si spontana folosesc in acest scop retele de comutatie care au rolul de a modifica interconexiunile dintre componente.

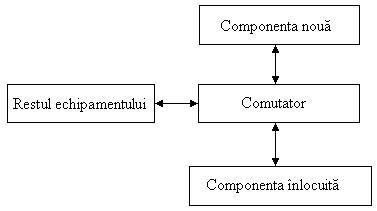

Cea mai simpla strategie de reconfigurare a echipamentului, facuta in general pentru echipamente hardware, este plasarea componentelor intr-o configuratie de tip stand-by ca in figura 24.

Fig. 24. Reconfigurarea unui echipament prin tehnici de comutatie

Comutatorul prezinta interfete cu ambele componente. Comutatia de la o componenta la alta modifica ansamblul de interactiuni ale echipamentului, dar echipamentul insusi ramane neschimbat.

Daca erorile de proiectare nu sunt considerate ca fiind esentiale, elementul de rezerva poate fi identic cu elementul functional. Daca se doreste eliminarea erorilor de proiectare, atunci elementul functional si cel de rezerva sunt proiectate in mod independent.

In unele echipamente tolerante la defectari, in scopul obtinerii unor avantaje din prezenta elementelor de rezerva, se adopta strategia urmatoare: din start toate componentele, active si de rezerva, sunt disponibile sa asigure servicii, iar in momentul identificarii unui defect, componenta suspecta este inlaturata. In acest mod echipamentul are o capacitate marita de a suporta suprasolicitari si un grad de tolerare a defectarilor superior celui specificat initial. Acest mod de operare conduce la o degradare lenta a serviciilor asigurate de echipament, datorita faptului ca serviciile componentelor defecte sunt preluate de cele ramase in stare de functionare.

Dimensiunile unitatilor inlocuibile influenteaza atat efortul necesar localizarii defectelor, cat si costul intregului echipament si depind de mai multi factori.

Unitatile mari permit o localizare mai usoara a defectarii dar impun in mod corespunzator o redundanta la nivel superior de unde poate rezulta un cost mai ridicat al echipamentului.

Unitatile mici contin mai putine componente, putand fi proiectate pentru a avea facilitati cat mai mari, dar in schimb necesita o retea de comutatie mai complexa.

Un alt factor care influenteaza marimea unitatilor inlocuibile il constituie nivelul la care este posibila reparatia.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2876

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved