| CATEGORII DOCUMENTE |

Bibliografie:

Gh. Puscasu, V. Nicolau, , "Procesoarele de Semnal TMS320C3X. Aplicatii".

Capitolul I: Familia Procesoarelor de semnal TMS320

Introducere

Generatia procesoarelor TMS320C3x

Capitolul II: Structura Hardware a Procesoruli de Semnal TMS320C32

2.1 Structura Interna

2.2 Unitatea Centrala de Prelucrare

2.2.1 Unitatea de inmultire

2.2.2 Unitatea aritmetico-logica

2.2.3 Unitati aritmetice auxiliare pentru adrese

2.2.4 Registrele unitatii centrale de prelucrare

2.2.5 Registrul de stare

2.3 Organizarea Memoriei Interne

2.3.1 Memoria cache

2.3.2 Harta de memorie a procesorului TMS320C32

2.3.3 Harta adreselor de memorie asignate porturilor I/O

2.4 Sistemul de Intreruperi

2.4.1 Registrul de validare a intreruperilor CPU/DMA (IE)

2.4.2 Registrul indicatorilor de intreruperi CPU(IF)

2.4.3 Tabela vectorilor de intreruperi si executie pas cu pas

FAMILIA PROCESOARELOR DE SEMNAL TMS320

1.1. Introducere

Procesoarele de semnal, numite in literatura de specialitate DSP-uri (DSP = Digital Signal Processor), sunt sisteme de calcul programabile de tip "single-chip", destinate prelucrarii complexe a semnalelor digitale. Desi se numesc procesoare, ele inglobeaza intr-un singur circuit integrat, principalele subsisteme componente ale unui sistem de calcul (unitate centrala, subsistem de memorie, subsistem de intrare/iesire etc.), realizand functii complexe de transfer si de prelucrare a datelor.

Pentru efectuarea unor prelucrari in timp real asupra datelor, procesoarele de semnal lucreaza la frecvente mari si dispun de un set complex de instructiuni, putand astfel executa zeci de milioane de operatii in virgula mobila pe secunda (MFLOPS = Million Floating-point Operations per Second). Totodata, structura interna paralela permite efectuarea mai multor operatii simultan, ceea ce creste considerabil puterea de calcul a DSP-ului.

Evolutia in timp a procesoarelor de semnal a fost conditionata de dezvoltarea tehnologiei de fabricatie a circuitelor integrate digitale. In general, tendintele dezvoltarii tehnologice au in vedere urmatoarele aspecte:

- marirea densitatii de integrare, prin cresterea numarului de tranzistoare pe unitatea de suprafata a chip-ului. Aceasta permite cresterea numarului unitatilor functionale integrate si a complexitatii acestora;

- cresterea frecventei interne de lucru a procesoarelor, ce se poate face explicit prin imbunatatirea calitatii tranzistoarelor si, implicit, prin micsorarea dimensiunii tranzistoarelor si a distantelor dintre ele;

- realizarea mai multor unitati paralele de prelucrare si de marire a dimensiunii cuvintelor prelucrate si memorate;

- micsorarea consumului energetic si a puterii disipate, ce tind sa creasca o data cu cresterea frecventei de lucru a procesoarelor;

- pastrarea compatibilitatii software cu modelele anterioare din aceeasi familie de procesoare.

Datorita performantelor in timp real si a capacitatii de prelucrare mare, procesoarele de semnal sunt utilizate intr-o gama larga de aplicatii, enumerate succint in tabelul 1.1.

Tab. 1.1. Domenii de utilizare a procesoarelor de semnal

|

Prelucrare de semnale |

Grafica/Imagini |

Instrumentatie |

|

Filtrare digitala |

Transformari 3D/ Renderizare |

Analiza Spectrala |

|

Convolutie |

Recunoastere de forme |

Generare de functii |

|

Corelatie |

Transmisie/Compresie imagini |

Potrivire de sabloane |

|

Transformari Hilbert |

Recunoasterea formelor |

Simulari seismice |

|

Transformari Fourier rapide |

Imbunatatire imagini |

Filtrare digitala |

|

Filtrare adaptiva |

Scanare cod de bare | |

|

Generare de semnale |

Statii de lucru grafice | |

|

Ferestre de timp | ||

|

Recunoastere voce |

Comanda |

Domeniul militar |

|

Voice mail |

Controlul discului |

Securitatea comunicatiilor |

|

Vocodere |

Comanda servo |

Procesare semnale radar |

|

Recunoastere vocala |

Comanda robotilor |

Procesare sonar |

|

Verificare amprenta vocala |

Imprimante laser |

Procesare imagini |

|

Imbunatatirea vorbirii |

Comanda motoarelor |

Instrumente de navigatie |

|

Sinteza vocala |

Filtre Kalman |

Ghidare rachete |

|

Text-to-speech |

Modemuri in radio-frecventa |

|

|

Retele neurale | ||

|

Telecomunicatii |

Locomotie |

|

|

Suprimarea ecoului |

FAX |

Securitatea comunicatiilor |

|

Transcodere ADPCM |

Telefonie celulara |

Analiza vibratiilor |

|

Multiplexarea canalelor |

Telefoane inteligente |

Sisteme anti-coliziune |

|

Modemuri |

Interpolare |

Control adaptiv al rularii |

|

Codare/Decodare DMTF |

Video conferinte |

GPS |

|

Criptare date |

Comenzi vocale |

|

|

Comunicatii in spectru larg |

Radio digital |

|

|

Bunuri de larg consum |

Industrie |

Domeniul medical |

|

Detectoare de radar |

Robotica |

Proteze auditive |

|

Instrumente de putere |

Comanda numerica |

Monitorizare pacienti |

|

Audio/TV digitale |

Securitatea accesului |

Echipamente cu ultrasunete |

|

Sintetizatoare muzicale |

Monitorizare surse de putere |

Echipamente de diagnostic |

|

Jucarii inteligente |

Inspectie vizuala |

Proteze |

|

Roboti telefonici |

CAM | |

Pentru obtinerea unei valori optime a raportului performanta/cost, structura interna a unui DSP trebuie adaptata specificului aplicatiei in care acesta se utilizeaza. In plus, performantele obtinute cu un anumit procesor de semnal depind esential de componentele software (programe utilitare si de aplicatii) oferite de fabricant.

De aceea, firmele producatoare au in vedere doua aspecte majore:

asigurarea unei game largi de produse si de solutii complete cu DSP-uri, adaptandu-se permanent la cerintele pietei;

crearea suportului software pentru dezvoltarea aplicatiilor cu DSP-uri.

De exemplu, firma Texas Instruments (TI) a devenit liderul pietei de procesoare de semnal digital, incepand cu anul 1982, cand a introdus pe piata procesorul TMS32010. In timp, firma a dezvoltat o gama foarte larga de produse, avand in productie mai mult de 100 de tipuri de DSP-uri, utilizate in domenii diverse, cum ar fi: comunicatii, calculatoare, produse de larg consum, conducerea proceselor industriale, instrumentatie, aplicatii militare etc. Pentru utilizarea eficienta a procesoarelor, firma TI ofera un pachet software amplu, sub forma de documentatii, aplicatii diverse si biblioteci de programe, colaborand cu peste 250 de firme producatoare de software si hardware.

Procesoarele de semnal digital din gama TMS320C3x produse de firma Texas Instruments sunt realizate in tehnologie CMOS si lucreaza cu numere in virgula mobila pe 32 de biti. Datorita unei magistrale interne extinse si a unui set puternic de instructiuni, DSP-ul poate executa pana la 60 MFLOPS. Procesorul dispune de un inalt grad de paralelism in executie, ce permite efectuarea simultana de pana la 11 operatii.

Procesoarele de semnal din familia TMS320 pot fi impartite in doua mari clase: procesoare de virgula fixa (cum sunt cele din generatiile 'C20x, 'C24x, 'C5x, 'C54x si 'C62x) si, respectiv, procesoare de virgula mobila (corespunzatoare generatiilor 'C3x, 'C4x, 'C67x).

1.3. Generatia procesoarelor TMS320C3x

Procesoarele TMS320C3x reprezinta prima generatia de procesoare in virgula mobila pe 32 de biti, avand performante de 33-60 MFLOPS si de 16.67-30 MIPS. Arhitectura C3x este proiectata pentru obtinerea unei platforme eficiente de tip compilator. Astfel, datorita compilatorului C optimizat si setului de instructiuni paralele, procesoarele din aceasta generatie sunt usor de utilizat si permit realizarea unor produse de inalta calitate intr-un timp scurt, fara un efort deosebit.

Unitatea centrala (UC) are o unitate aritmetica independenta de multiplicare in virgula fixa si mobila, precum si o unitate aritmetico-logica (UAL). Procesorul ofera o interfata de memorie flexibila, ce permite accesul pe 8, 16 si 32 de biti si poate adresa un spatiu de memorie de 16 Mcuvinte de 32 de biti.

Controlerul de acces direct la memorie (DMA = Direct Memory Access) poseda o magistrala proprie de date si functioneaza in paralel cu UC. Controlerul DMA poate accesa atat memoria interna a DSP-ului sau registrele periferice asignate la adrese de memorie, cat si memoria externa.

Procesoarele 'C3x, prin intermediul a 7 magistrale interne, pot transfera simultan patru cuvinte in fiecare ciclu masina: un cuvant de cod, doi operanzi pentru unitatea centrala si un transfer DMA de date.

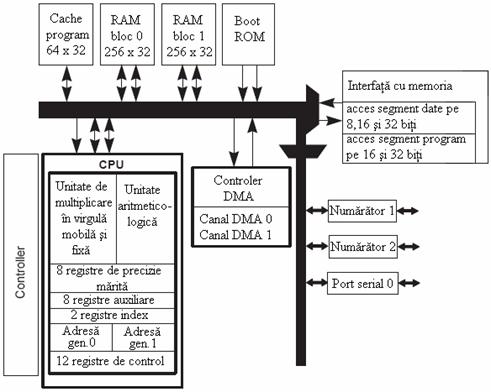

Cel mai reprezentativ DSP al acestei generatii este TMS320C32, a carui schema bloc este ilustrata in figura 1.2.

Fig. 1.2. Schema bloc a procesorului de semnal TMS320C32

Unul dintre avantajele acestui DSP este pretul, fiind cel mai ieftin procesor in virgula mobila pe 32 de biti. Codul masina este compatibil cu cel al procesoarelor 'C30 si 'C31.

De asemenea, 'C32 poate rula in regim de consum redus, in doua moduri. Primul mod reduce frecventa ceasului intern, permitand executia in continuare a instructiunilor, iar al doilea mod suspenda executia instructiunilor si pune procesorul in stare de asteptare.

Pe langa cele mentionate, procesorul TMS320C32 se caracterizeaza prin:

- ciclul instructiune de 33 ns, 40 ns si 50 ns;

- 2 canale DMA cu prioritati configurabile;

- moduri de functionare cu consum redus;

- memorie cache pentru program de 64 cuvinte;

- 2 numaratoare pe 32 de biti;

- port serial;

- boot ROM;

- 2 blocuri de memorie RAM cu dublu acces, de cate 256 cuvinte x 32 de biti.

Acest procesor poate fi utilizat intr-o gama larga de domenii, cum ar fi: industria automobilelor, procesare audio, control industrial, comunicatii de date, echipamente de birou (copiatoare, imprimate laser, echipamente multifunctionale) etc.

STRUCTURA HARDWARE A

PROCESORULUI DE SEMNAL TMS320C32

Structura interna

Familia de procesoare in virgula mobila pe 32 de biti TMS320C3x contine trei modele: 'C30, 'C31 si 'C32. Acestea pot efectua in paralel operatii aritmetico-logice si de inmultire cu numere intregi sau in virgula mobila, intr-un singur ciclu masina, atingand viteze de pana la 30 MIPS si 60 MFLOPS.

Din punct de vedere hardware, performantele procesoarelor TMS320C3x sunt date de urmatoarele elemente caracteristice, ce permit implementarea mai usoara a limbajelor de programare de nivel inalt:

- arhitectura bazata pe registre;

- memorii interne cu acces dual si memorie cache de program;

- spatiu mare de adresare si moduri de adresare puternice;

- interfata pentru conectarea in sisteme multiprocesor;

- sistem de intreruperi multiple;

- porturi seriale si numaratoare/temporizatoare;

- acces direct la memorie, prin controler DMA intern.

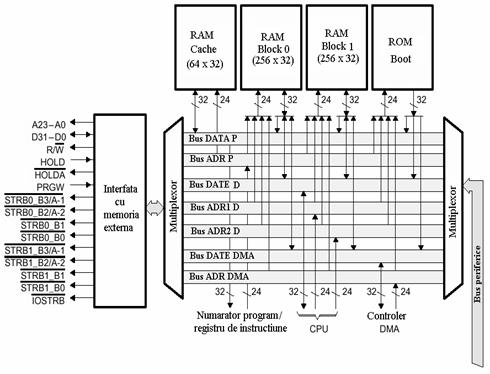

Procesorul de semnal TMS320C32 contine mai multe unitati, ce vor fi detaliate in subcapitolele urmatoare.

Schema bloc detaliata a procesorului de

semnal TMS320C32 este ilustrata in

figura 2.1.

Fig. 2.1. Schema bloc detaliata a procesorului TMS320C32

Din figura se observa ca procesorul contine urmatoarele elemente: o unitate centrala de prelucrare (UCP), cu 8 registre generale (R0-R7) si 8 registre auxiliare (AR0-AR7), o memorie cache pentru program cu capacitatea de 64 cuvinte de 32 de biti, doua blocuri de memorie interna RAM cu dublu acces, de cate 256 cuvinte de 32 de biti, doua numaratoare/ temporizatoare, utilizate la masurarea intervalelor de timp si la numararea trenurilor de impulsuri, un port serial, precum si un controler DMA intern cu 2 canale, ce suporta operatii concurente de intrare / iesire.

Procesorul are mai multe magistrale interne, pe care se pot transfera simultan pana la patru cuvinte in fiecare ciclu masina: un cuvant de cod, doi operanzi pentru unitatea centrala de la memoriile cu acces dual, precum si un transfer DMA de date.

O prezentare in detaliu a procesorului TMS320C32, in componentele sale hardware si software, depaseste spatiul acestei carti. Totusi, dezvoltarea aplicatiilor necesita o cunoastere aprofundata a componentei hardware si presupune consultarea permanenta a documentatiei complete a procesorului, pusa la dispozitia utilizatorilor de catre fabricant [29]

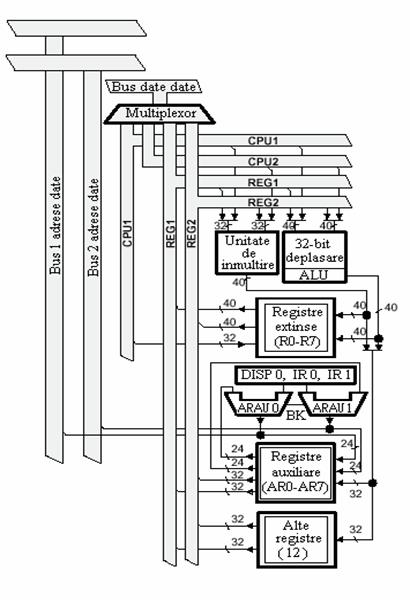

Unitatea centrala de prelucrare

Structura interna a unitatii centrale de prelucrare (UCP sau CPU = Central Processing Unit) este data in figura 2.2 si contine urmatoarele elemente:

unitati de inmultire numere intregi si numere reale in virgula mobila;

unitate aritmetico-logica (ALU = Arithmetic Logic Unit);

unitate de deplasare la stanga/dreapta pe 32 biti;

magistrale interne (CPU1/CPU2 si REG1/REG2);

unitati aritmetice auxiliare de adrese (ARAU = Auxiliary register arithmetic unit);

fisierul cu registre al CPU.

Cele patru magistrale de date interne ale UCP (CPU1, CPU2, REG1 si REG2) sunt conectate la magistrala de date a procesorului, prin intermediul unui multiplexor. Ele pot transfera doi operanzi de la memorii si doi operanzi de la registrele UCP, permitand intr-un singur ciclu, operatii paralele de inmultire si adunare/scadere.

Fig. 2.2. Structura unitatii centrale de prelucrare

Unitatea de inmultire

Unitatea de inmultire executa intr-un singur ciclu masina inmultiri cu numere intregi reprezentate pe 24 de biti si cu numere reale reprezentate pe 32 de biti. Implementarea paralela permite realizarea unei inmultiri si a unei operatii ALU intr-un singur ciclu instructiune, la o perioada a ceasului de 20 ns. Cand unitatea de inmultire realizeaza inmultiri in virgula mobila, intrarile sunt numere reale pe 32 de biti, iar rezultatul se reprezinta pe 40 de biti. Pentru inmultiri in virgula fixa, intrarile sunt numere intregi pe 24 de biti, iar rezultatul reprezinta numar intreg pe 32 de biti.

Unitatea aritmetico-logica

Unitatea aritmetico-logica (ALU) efectueaza, intr-un singur ciclu masina, operatii cu numere intregi reprezentate pe 32 de biti, operatii logice cu numere binare reprezentate pe 32 de biti si cu numere reale reprezentate pe 40 de biti. De asemenea, ALU realizeaza conversia numerelor intregi in numere reale si invers. Rezultatele operatiilor sunt intotdeauna pastrate pe 32 de biti pentru numere intregi si pe 40 de biti pentru numere reale. Tot intr-un singur ciclu masina se pot deplasa spre stanga sau spre dreapta bitii unui registru pe 32 de biti, cu un numar de pozitii predefinit.

Unitati aritmetice auxiliare pentru adrese

Unitatea centrala de prelucrare dispune de doua unitati aritmetice auxiliare (ARAU0 si ARAU1), ce pot genera doua adrese diferite intr-un singur ciclu. Unitatile ARAU lucreaza in paralel cu unitatea de inmultire si cu unitatea aritmetico-logica. Ele suporta adresari cu deplasamente, cu registrele index (IR0 si IR1), precum si adresarea circulara si adresarea in ordinea inversa a bitilor.

Registrele unitatii centrale de prelucrare

Procesorul TMS320C32 dispune de 28 de registre, numite registre primare, prezentate succint in continuare. Ele sunt grupate intr-un fisier de registre multiport, care este strans cuplat cu CPU. Toate registrele primare pot fi utilizate de unitatea de inmultire si de ALU si pot fi folosite ca registre generale de lucru.

De asemenea, registrele primare au si functii speciale. De exemplu, cele opt registre de precizie marita (R0 , R7) se pot utiliza la pastrarea rezultatului in virgula mobila cu precizie marita. Registrele auxiliare (AR0 , AR7) suporta o varietate de moduri de adresare indirecta si pot fi folosite ca registre generale pentru operatii cu numere intregi pe 32 de biti sau ca registre logice. Restul registrelor sunt utilizate pentru functii de sistem: adresare, managementul stivei, memorarea starilor procesorului, intreruperi, adrese si contor pentru bucle.

1. Registrele de precizie marita (R7 R0) sunt in numar de 8 si se utilizeaza la operatii cu numere intregi pe 32 de biti sau cu numere reale pe 40 de biti.

Cand se lucreaza cu operanzi in virgula mobila, registrele de precizie marita folosesc toti cei 40 de biti (bit39 bit0), dupa cum se poate observa in figura 2.3.

Fig. 2.3. Memorarea numerelor in virgula mobila, in registrele R7 R0

In acest caz, registrele de precizie marita au doua regiuni separate si distincte:

cei mai semnificativi 8 biti (bit39 bit32) sunt dedicati memorarii exponentului (e) corespunzator numarului in virgula mobila;

restul bitilor (bit31 bit0) sunt utilizati pentru memorarea mantisei numarului in virgula mobila, unde bit31 este bit de semn (S), iar bit30 bit0 reprezinta fractia (f).

Daca operanzii sunt numere intregi, cu sau fara semn, atunci se folosesc doar 32 de biti (bit31 bit0), restul bitilor ramanand nemodificati (figura 2.4). Acest lucru este valabil pentru toate operatiile de deplasare.

Fig. 2.4. Memorarea numerelor in virgula fixa, in registrele R7 R0

2. Registrele auxiliare (AR7 AR0) pe 32 de biti sunt in numar de 8 si pot fi accesate de CPU si modificate de cele doua unitati ARAU. Functia principala a registrelor auxiliare este de a genera adrese pe 24 de biti. De asemenea, ele pot fi folosite in adresarea indirecta, ca registre contor pentru ciclurile repetitive sau ca registre generale pe 32 de biti, putand fi modificate de unitatea de inmultire sau de ALU.

3. Registrul indicator pagina de date (DP) pe 32 de biti este utilizat la formarea adresei fizice de memorie. Registrul DP (DP = Data-page register) este incarcat cu instructiunea LDT. Cei mai putin semnificativi 8 biti (LSB = Least significant bit) ai indicatorului de pagina sunt folositi de modul de adresare direct. Ei indica pagina fizica de memorie utilizata la momentul curent. Paginile de memorie au lungimea de 64 Kcuvinte. Deoarece adresa este generata pe 24 de biti, rezulta ca procesorul TMS320C32 poate accesa in total 256 pagini de memorie.

4. Registrele de index (IR0, IR1) pe 32 de biti, contin valori index, ce pot fi utilizate de ARAU pentru calculul unei adrese de memorie indexate.

5. Registrul dimensiune bloc (BK) pe 32 de biti este folosit de ARAU in cazul adresarii circulare. Registrul BK (BK = Block-size register) specifica dimensiunea blocului de date utilizat ca registru circular.

6. Registrul indicator de stiva (SP) pe 32 de biti specifica adresa varfului stivei. Stiva functioneaza ca o memorie FIFO, iar registrul SP (SP = Stack pointer register) indica intotdeauna adresa ultimului element introdus in stiva. Orice operatie de adaugare in stiva este precedata de o incrementare a registrului SP, iar orice operatie de extragere din stiva este urmata de o decrementare a SP. Doar cei mai putin semnificativi 24 de biti sunt folositi ca adresa de memorie pentru varful stivei.

Registrul SP este utilizat de fiecare data cand se doreste salvarea contextului programului aflat in executie, la tratarea intreruperilor, in timpul executarii pas cu pas a programului, la apeluri de proceduri, la intoarceri din proceduri, precum si de instructiunile PUSH si POP.

7. Registrul de stare (ST) pe 32 de biti contine informatii globale despre starea UCP. In functie de rezultatul operatiilor (0, negativ etc.), unele instructiuni (cum ar fi cele de incarcare si de salvare a registrelor, cele aritmetice si logice etc.) modifica valoarea indicatorilor de conditie ai registrului ST (ST = Status register).

De asemenea, este permisa incarcarea acestui registru cu valoarea unui operand sursa, indiferent care ar fi starea bitilor din ST. In urma unei astfel de operatii, continutul registrului ST va fi identic cu cel al operandului sursa. Acest lucru permite salvarea si restaurarea registrului ST.

La initializarea sistemului, registrul ST are valoarea 00000000H.

8. Registrul de validare a intreruperilor CPU/DMA (IE) pe 32 de biti permite validarea sau invalidarea intreruperilor CPU sau DMA. Bitii de validare a intreruperilor CPU se afla pe pozitiile bit11 bit0, iar cei pentru validarea intreruperilor DMA se gasesc pe pozitiile bit31 bit16

Prin setarea bitilor registrului IE (IE = Interrupt-enable register), intreruperile respective sunt validate, iar prin resetarea lor (pozitionare pe 0), se indica faptul ca intreruperea corespunzatoare este invalidata.

9. Registrul indicatorilor de intreruperi (IF) pe 32 de biti semnaleaza care intreruperi au fost activate de catre unitatile slave. Daca un bit al registrului IF (IF = Interrupt flag register) are valoarea 1, atunci acesta indica aparitia unei intreruperi generate de perifericul corespunzator bitului setat. De asemenea, bitii pot fi setati prin program, pentru a provoca o intrerupere. Daca un bit al registrului IF este resetat (valoare 0), atunci intreruperea respectiva se anuleaza.

La initializarea procesorului, continutul bitilor registrului IF este 00000000H.

Cei mai semnificativi 16 biti ai registrului IF (bit31 bit16) reprezinta indicatorul tabelei vectorilor de intreruperi si de executie pas cu pas (ITTP = Interrupt-trap table pointer). Vectorul reset al procesorului TMS320C32, ca si in cazul celorlalte procesoare din familia lui, se afla la adresa 000000H. Totusi, tabela de vectori pentru intreruperi si executie pas cu pas a unui program se poate situa si la o alta adresa de memorie, aceasta fiind stabilita de utilizator prin ITTP.

10. Registrul indicatorilor de intrare/iesire (IOF) pe 32 de biti controleaza functiile pinilor externi: XF0 si XF1. Acesti pini pot fi configurati pentru operatii de intrare si iesire, putand fi scrisi si cititi. La initializarea procesorului, bitii corespunzatori din registrul IOF (I/O flag register) devin 0.

11. Registrul contor pentru bucle (RC) pe 32 de biti este utilizat pentru executia repetitiva a unui bloc de program. Registrul RC (RC = Repeat-counter register) specifica de cate ori se repeta un bloc de instructiuni intr-o bucla repetitiva.

Daca RC contine valoarea N, bucla va fi executata de (N+1) ori.

12. Registrele de adrese pentru structuri repetitive (RS, RE) sunt pe 32 de biti. RS (RS = Repeat start-address register) si RE (RE = Repeat end-address register) contin adresa de inceput, respectiv adresa de sfarsit ale blocului de memorie program care se executa in bucla. Daca RE < RS, atunci programul executa o singura data codul blocului de instructiuni dintre adresele indicate de RS si RE.

Procesorul mai are doua registre, care nu apartin unitatii centrale de prelucrare., ci unitatii de control. Ele sunt utilizate pentru citirea si decodificarea instructiunilor.

13. Registrul numarator de program (PC) pe 32 de biti contine adresa de memorie de unde se va citi opcodul urmatoarei instructiuni, in timpul ciclului de citire a instructiunii (fetch). Adresa este furnizata magistralei de adrese program pe 24 de biti.

Desi registrul PC (Program-counter register) nu face parte din registrele CPU, totusi acesta poate fi modificat prin instructiuni program.

14. Registrul instructiune (IR) pe 32 de biti memoreaza opcodul instructiunii curente, in timpul etapei de decodificare a instructiunii. Acest registru este folosit de unitatea de decodificare a instructiunii si nu este accesibil unitatii centrale de prelucrare.

Registrul de stare

Registrul de stare contine informatii globale despre starea unitatii centrale de prelucrare, sub forma indicatorilor de conditii si control.

De regula, operatiile aritmetice si logice, in functie de rezultatul obtinut, seteaza indicatorii de conditie ai registrului ST. De asemenea, setarea indicatorilor se face si in cazul instructiunilor de incarcare in registre si de salvare in memorie.

Asupra registrului de stare se pot efectua operatii de salvare si de restaurare. Prin operatiile de incarcare (restaurare) a registrului ST, bitii acestuia sunt inlocuiti de cei ai operandului sursa, indiferent de starea bitilor operandului sursa. Dupa o astfel de instructiune, continutul lui ST va fi identic cu continutul operandului sursa.

La initializarea sistemului, in registru ST se scrie valoarea 00000000H.

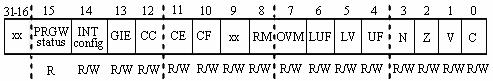

In figura 2.5. se prezinta structura registrului de stare ST. Toti bitii de interes (indicatorii de conditii si control) se pot citi (R = read) si scrie (W = write), cu exceptia bitului PRGW, care poate fi doar citit.

Fig. 2.5. Registrul de stare ST

Din figura, se poate observa ca cei mai putin semnificativi 8 biti sunt indicatori de conditii, iar bitii bit15 bit10 si bit8 reprezinta indicatori de control. Restul bitilor sunt rezervati, valorile citite fiind 0.

Semnificatia indicatorilor de conditii si de control, specificati in registrul de stare, este data in tabelul 2.1.

Tab. 2.1. Indicatorii registrului de stare

C |

Carry Flag - indicator de transport. |

V |

Overflow Flag - indicator care este setat daca numarul intreg rezultat este in afara intervalului de reprezentare (operand cu semn sau fara semn) sau daca numarul real obtinut are exponentul mai mare decat 127. Orice operatie care nu produce conditiile mentionate sterge indicatorul V. |

|

Z |

Zero Flag - indicator de zero. |

|

N |

Negative Flag - indicator de rezultat negativ. |

|

UF |

Underflow Flag - indicator ce semnaleaza faptul ca exponentul numarului real rezultat este mai mic sau egal cu -128. Indicatorul UF este sters daca operatia aritmetica nu genereaza un exponent mai mic sau egal cu -128. |

|

|

Latched Overflow Flag - indicator care este setat de fiecare data cand este setat si indicatorul V. |

|

LUF |

Latched Underflow Flag- indicator care este setat de fiecare data cand este setat si indicatorul UF. |

|

OVM |

Overflow Mode Flag - acest indicator este afectat doar de operatiile cu numere intregi. Daca OVM=0 (modul "overflow" este dezactivat), atunci rezultatele operatiilor care conduc la depasiri nu sunt tratate in mod special. Daca OVM=1, rezultatele operatiilor cu numere intregi care dau depasire in directia pozitiva sunt trunchiate la 7FFFFFFFh, iar cele care dau depasire in directie negativa sunt trunchiate la 80000000h. |

|

RM |

Repeat Mode Flag - Daca RM=1, atunci registrul PC este modificat de instructiunile de repetare bloc sau repetare instructiune. |

CE |

Cache Enable -activeaza sau dezactiveaza memoria cache de instructiuni. Daca CF=1, atunci memoria cache de instructiuni este validata si va functiona ca o stiva LRU (LRU = Least recently used). Daca CF=0, memoria cache este dezactivata si nu va fi nici modificata, nici actualizata. |

|

CF |

Cache Freeze - activeaza sau dezactiveaza cache-ul de instructiuni. Daca CF=1, se "ingheata" memoria cache (cache-ul nu mai este actualizat), inclusiv algoritmul LRU. Daca si CE=1, atunci se pot citi instructiuni din cache, insa nu se pot face modificari in cache. La reset, acest bit este pus in 0 si apoi, dupa reset, este trecut in 1. Daca CF=0, memoria cache este automat actualizata prin citiri din memoria externa. |

|

CC |

Cache Clear - sterge memoria cache. |

|

GIE |

Global Interrupt Enable - activeaza sau dezactiveaza intreruperile procesorului. |

|

INT config |

Interrupt Configuration - seteaza semnalele externe de intrerupere INT3-INT0 pentru activare pe palier sau pe front. INT config = 0 - semnalele de intrerupere externe INT3-INT0 sunt configurate pentru activare pe palier. INT config = 1 - intreruperile externe sunt active pe front. |

|

PRGW status |

Program Width Status - indica starea pinului extern PRGW. Daca pinul PRGW este in 1, atunci bitul PRGW trece in 1, indicand faptul ca memoria externa este organizata pe cuvinte de 16 biti. Procesorul va efectua 2 cicluri de fetch pentru incarcarea unei instructiuni pe 32 biti. Daca PRGW = 0, se indica organizarea memoriei in cuvinte pe 32 biti. |

Instructiunile procesorului pot testa indicatorii de conditii, in operatii cu numere fara semn sau cu semn, precum si individual, dupa cum se arata in tabele 2.2

Tab. 2.2. Compararea a doua numere fara semn

|

Conditie |

Cod |

Descriere |

Indicatori |

|

LO |

Mai mic |

C |

|

|

LS |

Mai mic sau egal |

C OR Z |

|

|

HI |

Mai mare |

~C AND ~Z |

|

|

HS |

Mai mare sau egal |

~C |

|

|

EQ |

Egal |

Z |

|

|

NE |

Diferit |

~Z |

Tab. 2.3. Compararea a doua numere cu semn

|

Conditie |

Cod |

Descriere |

Indicatori |

|

LT |

Mai mic |

N |

|

|

LE |

Mai mic sau egal |

N OR Z |

|

|

GT |

Mai mare |

~N AND ~Z |

|

|

GE |

Mai mare sau egal |

~N |

|

|

EQ |

Egal |

Z |

|

|

NE |

Diferit |

~Z |

Tab. 2.4. Compararea cu zero

|

Conditie |

Cod |

Descriere |

Indicatori |

|

Z |

Zero |

Z |

|

|

NZ |

Diferit de zero |

~Z |

|

|

P |

Pozitiv |

~N AND ~Z |

|

|

N |

Negativ |

N |

|

|

NN |

Non-negativ |

~N |

Tab. 2.5. Compararea raportata strict la indicatorii de conditii

|

Conditie |

Cod |

Descriere |

Indicator |

|

NN |

Non-negativ |

~N |

|

|

N |

Negativ |

N |

|

|

NZ |

Non-zero |

~Z |

|

|

Z |

Zero |

Z |

|

|

NV |

|

Non-overflow |

~V |

|

V |

Overflow |

V |

|

|

NUF |

Non-underflow |

~UF |

|

|

UF |

Underflow |

UF |

|

|

NC |

Non-carry |

~C |

|

|

C |

Carry |

C |

|

|

NLV |

Non-latched overflow |

~ |

|

|

|

Latched overflow |

|

|

|

NLUF |

Non-latched floating-point underflow |

~LUF |

|

|

LUF |

Latched floating-point underflow |

LUF |

|

|

ZUF |

Zero sau floating-point underflow |

Z sau UF |

Organizarea memoriei interne

Procesorul TMS320C32 poate adresa un spatiu total de memorie de 16 Mcuv. pe 32 de biti, ce poate fi utilizat pentru memorarea programelor, a datelor si a informatiilor despre unitatile I/O. Memoria interna a procesorului contine unitati RAM si ROM, in care se pot stoca programe sau date sub forma de tabele, coeficienti etc.

In figura 2.6 se arata modul de organizare a memoriei interne a procesorului TMS320C32. Blocurile 1 si 2 de memorie RAM au fiecare 256 cuvinte de 32 de biti si permit doua accesari intr-un singur ciclu masina. De aceea, ele se numesc memorii RAM cu acces dual (DARAM). Aceste memorii pot pastra si programe si date.

De asemenea, un program incarcator de programe ( numit boot-loader),

aflat in memoria ROM de 4Kcuvinte de 32 de biti, permite incarcarea unui program

sau a unor date dupa initializarea sistemului, de la un port serial sau de la o

memorie externa organizata pe 1, 2, 4, 8, 16 sau 32 de biti. Folosind un singur

pin extern (MCBL ![]() ),

se pot configura primele 1000H cuvinte de memorie pentru a accesa memoria ROM

interna a procesorului sau memoria RAM externa.

),

se pot configura primele 1000H cuvinte de memorie pentru a accesa memoria ROM

interna a procesorului sau memoria RAM externa.

Memoria ROM, la fel ca si memoria RAM interna, permite 2 accesari de catre CPU intr-un singur ciclu masina.

Fig. 2.6. Organizarea memoriei interne a procesorului TMS320C32

Multe dintre performantele procesorului TMS320C32 se datoreaza magistralelor interne multiple, ce permit paralelismul in executie. Astfel, magistralele interne separate pentru program, date si transfer DMA permit executarea in paralel a unor operatii de extragere cod instructiune, citire/scriere de date si transferuri pe canale DMA.

Procesorul are 7 magistrale interne: 2 magistrale de program (Bus DATA P si Bus ADR P), 3 magistrale de date (Bus DATE D, Bus ADR1 D si Bus ADR2 D) si 2 magistrale DMA (Bus DATE DMA si Bus ADR DMA).

Aceste magistrale conecteaza blocurile functionale ale procesorului si permit executarea mai multor operatii in paralel. De exemplu, intr-un singur ciclu masina, unitatea centrala de prelucrare poate accesa 2 date dintr-un bloc RAM si poate efectua o extragere cod instructiune din memoria externa, in timp ce controller-ul DMA poate realiza un transfer de date cu celalalt bloc de memorie RAM.

Registrul PC pe 32 de biti este conectat la magistrala de adrese program (Bus ADR P), prin cei mai putin semnificativi 24 de biti ai sai. Registrul instructiune IR este conectat la magistrala de date program de 32 de biti. Pe aceste magistrale se poate aduce, in fiecare ciclu masina, codul unei instructiuni pe 32 de biti din unitatile de memorie interna sau externa.

Magistralele de adrese pentru transferul datelor pe 24 de biti (Bus ADR1 D si Bus ADR2 D) si magistrala de date de 32 de biti (Bus DATE D) permit doua accesari la memoria de date, in fiecare ciclu masina. Magistrala Bus DATE D transporta date catre CPU, prin cele 4 magistrale ale CPU: magistralele CPU1 si CPU2 pot transporta, intr-un ciclu masina, doi operanzi de date la unitatea multiplicativa, respectiv la ALU, iar magistralele REG1 si REG2 pot transporta simultan, intr-un ciclu masina, doua date cu registrele din fisierul de registre.

Canalele DMA pot efectua transferuri folosind magistrala de adrese (Bus ADR DMA) pe 24 de biti si magistrala de date (Bus DATE DMA) pe 32 de biti. Aceste magistrale permit controller-ului DMA sa efectueze accesari la memorie in paralel cu transfer de informatii pe magistralele de date si de program.

Magistrala externa poate fi folosita pentru implementarea unui sistem de dezvoltare cu DSP, conectandu-se diverse componente in exteriorul procesorului. Interfata pentru memoria externa are posibilitatea de a adresa independent date din memorii externe, organizate pe 8, 16 sau 32 de biti.

Memoria cache

Procesorul TMS320C32 dispune de o memorie cache pentru instructiuni, de dimensiune 64 cuvinte de 32 de biti. Conceptul de memorie cache reduce mult numarul de accesari la memoria externa procesorului, care dureaza mai multe stari de ceas. Astfel, programele pot fi memorate si in memorii externe mai lente, dar mai ieftine. De asemenea, memoria cache elibereaza magistralele externe, ce pot fi astfel folosite de catre canalele DMA, pentru transferuri de date.

Memoria cache opereaza automat, fara interventia utilizatorului, folosindu-se un algoritm LRU pentru actualizarea continutului ei. Memoria cache este organizata in set asociativ pe 2 cai, fiind impartita in doua segmente de cate 32 de cuvinte.

Memoria externa va fi si ea impartita in segmente de cate 32 locatii de memorie. Corespunzator, adresa de memorie pe 24 de biti este impartita in 2 campuri: adresa de start a segmentului (SSA = Segment start address) pe 19 biti si, respectiv, numarul cuvantului in interiorul segmentului pe 5 biti, ca in figura 2.7.

Fig. 2.7. Campurile adresei de memorie pentru algoritmul memoriei cache

Campul SSA joaca rol de eticheta si va fi comparat cu valorile SSA (etichetele) memorate de cele doua segmente de memorie cache. De aceea, fiecare segment de memorie cache are propriul registru SSA pe 19 biti, ce indica segmentul de memorie care se gaseste deja memorat si in memoria cache.

Arhitectura memoriei cache este ilustrata in figura 2.8.

Fig. 2.8. Arhitectura memoriei cache

Din figura se observa ca, pentru fiecare cuvant din cele 2 segmente de memorie cache, se pastreaza cate un bit de prezenta, care indica daca acel cuvant din segmentul de memorie se gaseste deja memorat si in memoria cache.

Cand unitatea centrala de prelucrare doreste un cuvant instructiune din memoria externa, algoritmul memoriei cache verifica daca respectivul cuvant de instructiune se gaseste deja adus in memoria cache.

Pentru aceasta, algoritmul memoriei cache compara campul SSA din adresa de memorie cu valorile registrelor SSA ale memoriei cache. Daca exista o egalitate, se verifica bitul de prezenta corespunzator cuvantului dorit din segment (dat de campul numar cuvant din adresa) si, daca acesta este 1, inseamna ca data dorita se gaseste in memoria cache si va fi citita de aici. Daca una dintre conditii nu se respecta, inseamna ca instructiunea dorita nu se gaseste in memoria cache si va fi citita din memoria externa. Simultan, ea va fi scrisa si in memoria cache.

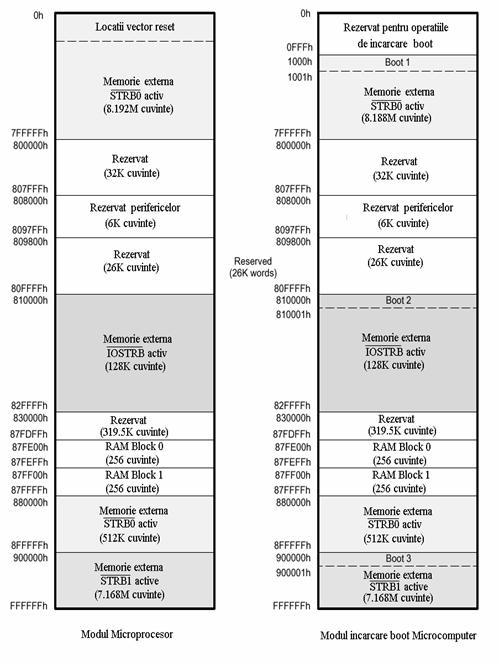

Harta de memorie a procesorului TMS320C32

Harta de

memorie depinde de modul de lucru al procesorului, determinat de semnalul MCBL/![]() :

"modul microprocesor" (MCBL/

:

"modul microprocesor" (MCBL/![]() =0), respectiv "modul microcalculator" (MCBL/

=0), respectiv "modul microcalculator" (MCBL/![]() =1).

Harta de memorie este similara pentru cele doua moduri, fiind ilustrata in

figura 2.9. Se observa ca, in ambele moduri de lucru ale procesorului, exista

mai multe zone de memorie rezervate. De asemenea, blocurile de memorie RAM 0 si

1 se gasesc mapate in aceleasi zone de memorie consecutive, incepand de la

adresele de memorie 87FE00H,

respectiv 87FF00H.

=1).

Harta de memorie este similara pentru cele doua moduri, fiind ilustrata in

figura 2.9. Se observa ca, in ambele moduri de lucru ale procesorului, exista

mai multe zone de memorie rezervate. De asemenea, blocurile de memorie RAM 0 si

1 se gasesc mapate in aceleasi zone de memorie consecutive, incepand de la

adresele de memorie 87FE00H,

respectiv 87FF00H.

Daca

procesorul lucreaza in "modul

microprocesor", programul incarcator de programe (boot-loader) nu se afla

mapat in harta de memorie a procesorului 'C32. Locatiile de adresa 0H-7FFFFFH sunt accesate prin portul

corespunzator memoriei externe (cu ![]() activ), la adresa 000000H fiind vectorul de intrerupere RESET.

activ), la adresa 000000H fiind vectorul de intrerupere RESET.

In cazul

cand se lucreaza in "modul

microcalculator", memoria ROM interna a procesorului, ce contine programul

boot-loader, este mapata in harta de memorie la adresele 0-0FFFH, iar locatiile 1000H-7FFFFFH

sunt accesate prin intermediul portului pentru memoria externa (![]() activ).

activ).

Fig. 2.9. Harta memoriei corespunzatoare procesorului TMS320C32

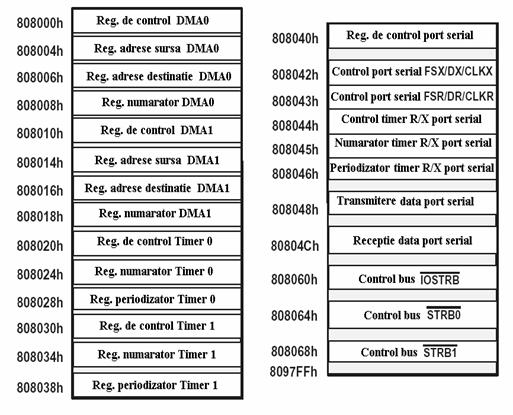

Harta adreselor de memorie asignate porturilor I/O

Pe langa harta spatiului de memorie, trebuie cunoscute si adresele de memorie asignate perifericelor si registrelor de control corespunzatoare magistralelor externe. Acestea formeaza harta adreselor de memorie asignate porturilor I/O si registrelor de control pentru magistralele externe, care este ilustrata in figura 2.10.

Fig. 2.10. Harta adreselor de memorie asignate perifericelor

Din figura se observa ca procesorul are rezervat un spatiu de memorie pentru registrele perifericelor, incepand de la adresa 808000H. Pentru fiecare registru de periferic este asignata o adresa de memorie, iar aceste adrese nu sunt consecutive.

Sistemul de intreruperi

Intreruperile pot fi validate sau invalidate prin intermediul registrului IE, iar starea intreruperilor validate poate fi monitorizata prin registrul IF.

Registrul IE este un registru pe 32 de biti utilizat atat la validarea intreruperilor CPU prin intermediul bitilor bit11 bit0, cat si pentru validarea intreruperilor generate catre cele doua canale DMA, folosind bitii bit31 bit16. Configuratia bitilor registrului IE este ilustrata in figura 2.11.

Daca un bit este incarcat cu valoarea 1, atunci intreruperea corespunzatoare bitului este validata, iar daca valoarea este 0, intreruperea este invalidata. La initializarea sistemului, registrul IE este incarcat cu valoarea 00000000H, toate intreruperile fiind invalidate.

|

EINT3 (DMA1) |

EINT2 (DMA1) |

EINT1 (DMA1) |

EINT0 (DMA1) |

EDINT0 (DMA1) |

EDINT (DMA) |

ETINT1 (DMA0) |

ETINT0 (DMA0) |

ETINT1 (DMA1) |

ETINT0 (DMA1) |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

ERINT0 (DMA1) |

EXINT0 (DMA0) |

EINT3 (DMA0) |

EINT2 (DMA0) |

EINT1 (DMA0) |

EINT0 (DMA0) |

XX |

XX |

XX |

XX |

EDINT1 (CPU) |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

EDINT0 (CPU) |

ETINT1 (CPU) |

ETINT0 (CPU) |

XX |

XX |

ERINT0 (CPU) |

EXINT0 (CPU) |

EINT3 (CPU) |

EINT2 (CPU) |

EINT1 (CPU) |

EINT0 (CPU) |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Fig. 2.11. Registrul de validare a intreruperilor

Semnificatiile indicatorilor registrului IE sunt date in tabelul 2.6.

Tab. 2.6. Indicatorii registrului de activare a intreruperilor

|

Bit |

Denumire |

Semnificatie |

|

EINT0 (CPU) |

Validare intrerupere externa 0 a CPU |

|

|

EINT1 (CPU) |

Validare intrerupere externa 1 a CPU |

|

|

EINT2 (CPU) |

Validare intrerupere externa 2 a CPU |

|

|

EINT3 (CPU) |

Validare intrerupere externa 3 a CPU |

|

|

EXINT0 (CPU) |

Validare intreruperea transmisie seriala |

|

|

ERINT0 (CPU) |

Validare intrerupere receptie seriala |

|

|

xx |

Utilizat numai de procesorul TMS320C30 |

|

|

xx |

Utilizat numai de procesorul TMS320C30 |

|

|

ETINT0 (CPU) |

Validare intrerupere timer 0 catre CPU |

|

|

ETINT1 (CPU) |

Validare intrerupere timer 1 catre CPU |

|

|

EDINT0 (CPU) |

Validare intrerup. controller DMA0 catre CPU |

|

|

EDINT1 (CPU) |

Validare intrerup. controller DMA1 catre CPU |

|

|

EINT0 (DMA0) |

Validare intrerupere externa 0 catre DMA0 |

|

|

EINT1 (DMA0) |

Validare intrerupere externa 1 catre DMA0 |

|

|

EINT2 (DMA0) |

Validare intrerupere externa 2 catre DMA0 |

|

|

EINT3 (DMA0) |

Validare intrerupere externa 3 catre DMA0 |

|

|

EXINT0 (DMA0) |

Valid. intrerup. de transmisie seriala prin DMA0 |

|

|

ERINT0 (DMA1) |

Valid. intrerup. de receptie seriala prin DMA1 |

|

|

ETINT0 (DMA1) |

Validare intrerupere timer 0 catre DMA1 |

|

|

ETINT1 (DMA1) |

Validare intrerupere timer 1 catre DMA1 |

|

|

ETINT0 (DMA0) |

Validare intrerupere timer 0 catre DMA0 |

|

|

ETINT1 (DMA0) |

Validare intrerupere timer 1 catre DMA0 |

|

|

EDINT1 (DMA0) |

Validare intrerupere contr. DMA1 catre DMA0 |

|

|

EDINT0 (DMA1) |

Validare intrerupere contr. DMA0 catre DMA1 |

|

|

EINT0 (DMA1) |

Validare intrerupere externa 0 catre DMA1 |

|

|

EINT1 (DMA1) |

Validare intrerupere externa 1 catre DMA1 |

|

|

EINT2 (DMA1) |

Validare intrerupere externa 2 catre DMA1 |

|

|

EINT3 (DMA1) |

Validare intrerupere externa 3 catre DMA1 |

Intreruperile validate pentru canalele DMA permit sincronizarea transferului de date intre periferice si memoria DSP-ului, fara interventia unitatii centrale. De asemenea, se poate observa faptul ca si cele doua canale DMA pot sa-si sincronizeze activitatea, prin setarea adecvata a bitilor 26 si 27.

Multiplele variante de intreruperi, de la un periferic spre toate unitatile master, permit implementarea unui sistem foarte flexibil si dinamic, optimizandu-se astfel transferurile de date intre periferice si memorie.

Registrul indicatorilor de intreruperi CPU (IF)

Registrul indicatorilor de intreruperi CPU (IF) pe 32 de biti semnaleaza care intreruperi au fost activate de catre unitatile slave. Bitii acestui registru se seteaza in momentul in care un periferic intern sau extern genereaza o intrerupere deja validata. De asemenea, un bit se poate seta si prin program, cauzand o intrerupere care apoi se trateaza, ca si cum aceasta intrerupere ar fi declansata de un periferic.

Daca un bit al registrului IF are valoarea 1, atunci acesta indica aparitia unei intreruperi CPU generate de perifericul corespunzator bitului setat. Daca intr-un bit al registrului IF se inscrie valoarea zero, atunci intreruperea corespunzatoare este stearsa. La initializarea procesorului, continutul bitilor registrului IF este 00000000H.

Registrul indicatorilor de intreruperi CPU este ilustrat in figura 2.12, iar semnificatia bitilor acestuia este data in tabelul 2.7.

|

ITTP |

XX |

DINT1 |

DINT0 |

TINT1 |

TINT0 |

XX |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

XX |

RINT0 |

XINT0 |

INT3 |

INT2 |

INT1 |

INT0 |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Fig. 2.12. Registrul indicatorilor de intreruperi CPU

Tab. 2.7. Semnificatia indicatorilor de intreruperi

|

INT0 |

Indicator pentru intreruperea externa 0 |

|

INT1 |

Indicator pentru intreruperea externa 1 |

|

INT2 |

Indicator pentru intreruperea externa 2 |

|

INT3 |

Indicator pentru intreruperea externa 3 |

|

XINT0 |

Indicator pentru intreruperea de transmisie seriala |

|

RINT0 |

Indicator pentru intreruperea de receptie seriala |

|

TINT0 |

Indicator pentru intreruperea generata de timer 0 |

|

TINT1 |

Indicator pentru intreruperea generata de timer 1 |

|

DINT0 |

Indicator pentru intreruperea generata de DMA0 |

|

DINT1 |

Indicator pentru intrerupere generata de DMA1 |

|

ITTP |

Indicatorul tabelei de intreruperi si executie pas cu pas |

Tabela vectorilor de intreruperi si executie pas cu pas

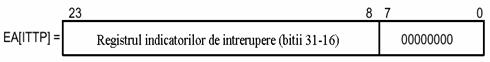

Cei mai semnificativi 16 biti ai registrului IF (bit31 bit16) reprezinta indicatorul tabelei vectorilor de intreruperi si de executie pas cu pas (ITTP). Acesta permite realocarea in memorie a tabelei vectorilor.

Vectorul RESET al procesorului TMS320C32, ca si in cazul celorlalte procesoare din familia lui, se afla la adresa 000000H. Totusi, tabela de vectori pentru intreruperi si de executie pas cu pas (trap) a unui program se poate situa si la o alta adresa de memorie, fiind stabilita de utilizator prin ITTP.

Grupul de 16 biti ITTP stabileste adresa de start a tabelei vectorilor de intreruperi si de executie pas cu pas. Adresa de baza pe 24 de biti a tabelei este calculata prin deplasare la stanga cu 8 pozitii binare, a bitilor dati de ITTP. Valoarea obtinuta se numeste adresa de baza efectiva si se noteaza cu EA [ ITTP ].

In figura 2.13 se prezinta modul de calcul al adresei de baza efectiva a tabelei vectorilor de intreruperi si de executie pas cu pas.

Fig. 2.13. Calculul adresei de baza efectiva a tabelei ITTP

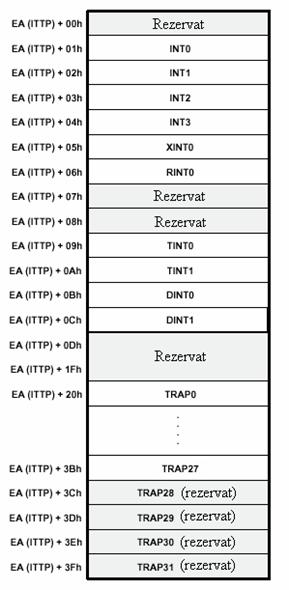

Adresa unei anumite intrari in tabela este data prin adunarea offset-ului vectorului de intrerupere respectiv, la adresa de baza efectiva. La aceasta intrare se gaseste memorata adresa de inceput a subrutinei de tratare a intreruperii respective sau de executie pas cu pas. De asemenea, cunoscand valoarea offset-ului, intrarea in tabela se poate calcula si prin concatenarea campului ITTP cu valoarea offset-ului pe 8 biti.

In figura 2.14 este ilustrat modul de ocupare a tabelei cu vectorii de intreruperi si de executie pas cu pas. Se observa ca adresele de memorie pentru fiecare intrare in tabela sunt calculate in functie de adresa de baza efectiva a tabelei si de offset-ul vectorului respectiv, in interiorul tabelei.

Pentru intreruperile vectorizate, offset-ul unei intreruperi este dat de numarul vectorului de intrerupere. Cand o intrerupere CPU validata in registrul IE este generata de catre un periferic, procesorul determina vectorul de intrerupere corespunzator si calculeaza intrarea in tabela vectorilor de intreruperi. De la aceasta locatie de memorie se citeste adresa de inceput a subrutinei de tratare a intreruperii respective.

Fig. 2.14. Tabela vectorilor de intreruperi si de executie pas cu pas

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2199

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2024 . All rights reserved