| CATEGORII DOCUMENTE |

| Bulgara | Ceha slovaca | Croata | Engleza | Estona | Finlandeza | Franceza |

| Germana | Italiana | Letona | Lituaniana | Maghiara | Olandeza | Poloneza |

| Sarba | Slovena | Spaniola | Suedeza | Turca | Ucraineana |

DOCUMENTE SIMILARE |

|

Etude simplifi�e du modulateur FM a boucle à verrouillage de phase

I � Structure fonctionnelle du modulateur.

II � Remarques pr�liminaires à l��tude du modulateur.

1) La boucle à verrouillage de phase (ou PLL � Phase locked loop �) est un systÈme asservi (contre-r�action).

Nous verrons successivement :

Le principe de la PLL

L�application de la PLL à la synthÈse de fr�quence.

L�application du synth�tiseur de fr�quence à PLL à la modulation FM.

Les propri�t�s particuliÈres du montage utilis� dans le thÈme.

2) Parmi les signaux ci-dessus :

VVCO est une tension sinusoÏdale (avec composante continue de polarisation).

Vout est une tension sinusoÏdale (la composante continue est supprim�e par le transformateur) ; la sinusoÏde convient bien aux oscillations dans les antennes (�mission-r�ception) et à la propagation dans l�air.

Vr�f est interm�diaire entre une sinusoÏde (avec composante continue) et un signal rectangulaire ; il s�agit d�une sinusoÏde �crÊt�e, produite par l�oscillateur à quartz.

VPLL est une tension continue, à variation lente devant la p�riode des autres signaux (t = 10 ms)

Les autres signaux (VR , VV , FR FV et Vmod) sont rectangulaires.

Le terme � d�phasage � ne concerne en toute rigueur que les signaux sinusoÏdaux (la phase est un angle) ; pour les autres signaux le terme exact est � d�calage (temps) � ; mais quand on �tudie le fonctionnement des PLL, on a coutume par simplification d�utiliser le terme � d�phasage � quelle que soit la forme des signaux :

d�calage des deux signaux p�riodiques non sinusoÏdaux : Dt (une fraction de p�riode : - T < Dt < T )

� d�phasage � de ces deux signaux :

DF = ![]() 2p < DF < +2p

2p < DF < +2p

Remarque : les comparateurs de phase simples (envisag�s au d�but de ce document) ont une �chelle - p/2 < DF < +p/2 ou une �chelle - p < DF < +p selon leur technologie. Seuls les comparateurs phase-fr�quence ont une �chelle - 2p < DF < +2p . Pour r�duire le nombre de courbes nous prendrons toujours l��chelle - 2p < DF < +2p

3) Les circuits d�un systÈme à PLL peuvent Être aliment�s de deux fa�ons :

Alimentation bipolaire (sym�trique) : les tensions peuvent Être positives ou n�gatives, et le point de repos est à 0V, les caract�ristiques sont centr�es sur 0.

Alimentation unipolaire : c�est le cas pour le montage du thÈme et c�est l�exemple que nous utiliserons pour cette �tude ; toutes les tensions sont positives (ex. de 0 à 8V), les caract�ristiques sont centr�es sur un point de repos correspondant à 4V par exemple.

III � Principe de la boucle à verrouillage de phase.

Structure.

Les �l�ments de base de la PLL sont :

Un comparateur de phase.

Un filtre passe-bas.

Un oscillateur command� en tension (OCT ou VCO � Voltage Controlled Oscillator �).

2) Comparateur de phase.

Ce circuit compare la phase de ces deux signaux, et fournit une tension d�erreur uDF(t) dont la valeur moyenne est proportionnelle au d�phasage DF (ou � erreur de phase �) entre ve et vs :

ve (t) = ve sin (we t + je vs (t) = vs sin (ws t + js

DF we t + je ws t + js we ws) t + (je js

a) Premier cas : la boucle est � verrouill�e �, nous verrons que cela se traduit par Fs = Fe :

DF je js

b) Second cas : la boucle n�est pas verrouill�e : DF et la tension uDF(t) varient à la fr�quence (Fe � Fs) qui est la fr�quence des � battements � de ve et vs .

La forme de la tension uDF(t) peut varier en fonction de la technologie du comparateur de phase (analogique, num�rique) et en fonction de la valeur du d�phasage ; l�important est que sa valeur moyenne varie lin�airement en fonction de DF

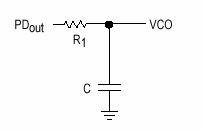

Filtre passe-bas.

Le r�le de ce filtre est d�extraire la valeur moyenne de la tension uDF(t), en rejetant les harmoniques. On obtient en sortie une tension u continue �gale à < uDF(t)> + 4 V (voir la caract�ristique de transfert page pr�c�dente, les 4 V repr�sentent le point de repos).

Quand la boucle est verrouill�e, les fr�quences Fs et Fe sont �gales, donc l�erreur de phase DF et la tension u sont constantes (aux perturbations prÈs).

Remarque : les paramÈtres du filtre (fr�quence de coupure, pente, amplification pour les filtres actifs) sont d�terminants pour les caractÈres de l�asservissement : stabilit�, pr�cision, temps de r�ponse, plages de capture et de verrouillage.

Oscillateur command� en tension (VCO).

Un oscillateur est un dip�le actif (sans compter les bornes

d�alimentations) qui produit un signal p�riodique. Un VCO est un

quadrip�le, il possÈde une entr�e pour une tension de commande u qui

permet de faire varier, lin�airement de pr�f�rence, la fr�quence Fs de l�oscillateur.

Dans le montage du thÈme, l�oscillation vs (t) produite est sinusoÏdale. La fr�quence

du VCO seul (non boucl� par la PLL) n�est ni pr�cise ni stable.

La fr�quence Fs de travail doit Être choisie entre Fs min et Fs max , et de pr�f�rence au voisinage de la � fr�quence centrale � du VCO : FS0 , qui correspond au point de repos u = 4V.

La valeur d�sir�e de la fr�quence centrale FS0 du VCO est obtenue par le choix des �l�ments (L , C) de l�oscillateur.

SynthÈse : caract�ristique de transfert � comparateur de phase + filtre + VCO �.

La synthÈse des deux caract�ristiques pr�c�dentes donne la caract�ristique de transfert ci-dessous :

Etude simplifi�e du fonctionnement de la PLL.

Envisageons le montage exp�rimental ci-dessous : la PLL est attaqu�e par un g�n�rateur de signal sinusoÏdal de fr�quence variable Fe .

Supposons (voir courbes pr�c�dentes) les valeurs suivantes pour le VCO :

fr�quence centrale FS0 = 1 kHz (pour u = 4 V) (valeurs du point de repos)

Fs min = 600 Hz (pour u = 0 V)

Fs max = 1400 Hz (pour u = 8 V)

Supposons que le filtre passe-bas est parfait et ne laisse passer que les signaux de fr�quence < 100 Hz

a) PLL verrouill�e (Fs = Fe) :

Si Fe = Fs = FS0 (cas id�al) alors u = 4V = cte (tension de repos du moyenneur) et DF =0 = cte ; vs et ve ont mÊme fr�quence et mÊme phase.

Si Fe = Fs = 900 Hz alors u = 3 V = cte et DF p/2 = cte ; vs est en avance de T/4 sur ve .

Si Fe = Fs = 1100 Hz alors u = 5 V = cte et DF p/2 = cte ; vs est en retard de T/4 sur ve .

Dans ces 3 cas DF = cte donc u = <uDF(t)> = cte ; mais en fait il y a toujours des perturbations : si Fs tend à augmenter, alors l��cart de phase DF je js diminue, donc <uDF(t)> et u diminuent, ce qui ramÈne Fs à la mÊme valeur que Fe ; de mÊme si Fs tend à diminuer ; il s�agit donc d�un �quilibre stable.

b) PLL non verrouill�e (Fs ¹ Fe) :

Le comparateur de phase fournit un signal uDF(t) form� de deux composantes :

l�une de fr�quence basse (Fe � Fs) qui pourra Être dans certains cas dans la bande passante du filtre (0<F<100Hz)

l�autre de fr�quence haute (Fe + Fs) qui est toujours >> 100 Hz donc rejet�e par le filtre.

Faisons varier Fe à partir de 500 Hz :

Fe = 500 Hz ; le comparateur de phase fournit une fr�quence haute 1500 Hz et une fr�quence basse 500 Hz ; les deux sont rejet�es par le filtre ; u reste à sa valeur de repos 4 V et Fs reste �gale à sa valeur de repos FS0 = 1kHz ; la PLL n�est pas verrouill�e.

Fe = 900 Hz : la fr�quence basse atteint 100 Hz et est transmise par le filtre. La fr�quence Fs se met à osciller à 100 Hz (autour de FS0 = 1000 Hz) mais en se rapprochant de 900 Hz (* voir page suivante), donc u diminue. C�est la phase de capture. Quand Fs atteint Fe = 900 Hz, la PLL se verrouille, alors u = cte = 3 V et DF p/2 = cte .

900 Hz < Fe < 1400 Hz : la PLL reste verrouill�e, avec Fs = Fe ; le d�phasage varie de - p/2 à 2p et u varie de 3V à 8V.

Fe = 1400 Hz et au-delà ; Fs ne peut plus augmenter ; la boucle se d�verrouille (Fs ¹ Fe), fs retombe à FS0 = 1000Hz, l��cart de fr�quence (Fe � Fs) = 400 Hz puis croit, cet �cart est de fr�quence sup�rieure à la bande passante du filtre passe-bas, donc u = 4 V = cte .

MÊme principe pour Fe d�croissante de 1500 Hz à 500 Hz : verrouillage à 1100 Hz et d�crochage à 600 Hz.

Pour cette PLL on dira que :

La plage de capture est de 900 Hz à 1100 Hz.

La plage de verrouillage est de 600 Hz à 1400 Hz.

L�exp�rience peut se r�sumer par les courbes suivantes :

Fe < 900 Hz : PLL non verrouill�e

Fe = 900 Hz : capture

900 Hz < Fe < 1400 Hz : verrouillage

Fe = 1400 Hz : d�crochage

Fe > 1400 Hz : PLL non verrouill�e

Fe > 1100 Hz : PLL non verrouill�e

Fe = 1100 Hz : capture

1100 Hz > Fe > 600 Hz : verrouillage

Fe = 600 Hz : d�crochage

Fe < 600 Hz : PLL non verrouill�e

En simplifiant on peut dire que :

la plage de capture d�pend plut�t de la bande passante du filtre.

la plage de verrouillage d�pend plut�t des fr�quences extrÊmes du VCO

la plage de verrouillage est plus large que la plage de capture.

(*) Le ph�nomÈne de capture est trÈs complexe ; on peut donner une premiÈre explication simple (mais � sch�matique � !) au fait que Fs se rapproche de Fe en disant que dÈs que Fe entre dans la plage de capture le filtre est � passant � donc la contre-r�action intervient et r�agit à la situation Fs > Fe en diminuant Fs .

Pour comprendre qualitativement le principe de la capture, imaginons un modÈle m�canique form� de deux disques tournant l�un face à l�autre sur deux axes colin�aires (comme les deux plateaux d�un embrayage), l�un entrain� à la vitesse Fe (fr�quence de rotation en tours/s) par un moteur puissant et l�autre entrain� dans le mÊme sens à la vitesse FS0 = 1000 tr/s = 1000 Hz par un trÈs petit moteur de couple faible ; un ressort de torsion se trouve entre les deux disques, il est fix� en permanence au disque Fe , et pour le moment il n�est pas fix� au disque FS0 donc les deux disques sont ind�pendants au d�part.

On part de Fe = 600 Hz (disques ind�pendants) et l�on augmente Fe : à la vitesse Fe = 900 Hz on entre dans la plage de capture (Bande passante du filtre) : dans notre modÈle, traduisons cela par l�apparition d�une liaison �lastique tendant à accoupler les deux disques (le ressort de torsion s�accroche au disque FS). Alors le disque Fs est � attir� � par le disque Fe à travers la liaison �lastique ; en raison de cette liaison et de son inertie, sa vitesse commence à osciller autour de sa vitesse initiale de 1000 Hz, mais quand le disque oscille vers Fe = 900 Hz , il oscille plus loin car il est attir�, et au contraire quand il oscille en s��loignant de 900 Hz, il oscille moins loin (voir courbe ci-dessus) car c�est simplement un � rebond � de la liaison �lastique et car le disque Fe est en train de � s��loigner � donc le ressort est en train de se tendre !

Donc petit à petit la fr�quence de rotation Fs se rapproche de Fe , les oscillations de la vitesse Fs s�arrÊtent et c�est le verrouillage : Fs = Fe les deux disques tournent à la mÊme vitesse 900 Hz avec un d�phasage constant car le ressort de torsion doit vaincre le couple moteur du petit moteur qui cherche à tourner à 1 kHz.

Une application des PLL : la d�modulation FM.

Le signal modul� FM capt� par le r�cepteur est appliqu� à l�entr�e de la PLL ; celle-ci se verrouille et suit les variations de fr�quence dues à la modulation. Le filtre passe bas est calcul� pour laisser passer les fr�quences du signal modulant (ex. : audiofr�quences), ainsi on recueille le signal u(t) (sortie du filtre et commande du VCO) qui est l�image du signal modulant de d�part (il existe d�autres fa�ons de d�moduler la FM).

IV � L�application de la PLL à la synthÈse de fr�quence.

Multiplicateur de fr�quence.

Dans cette application des PLL la fr�quence d�entr�e Fe est fixe, pr�cise et trÈs stable : c�est une fr�quence de r�f�rence (Fe = Fr�f).

Un diviseur de fr�quence par N (variable par programmation ou roues codeuses) est ins�r� dans le retour de la boucle. La boucle une fois verrouill�e la fr�quence Fs / N est �gale à Fr�f , donc le VCO oscille à une fr�quence Fs = N Fr�f (le VCO est r�alis� de fa�on que les fr�quences Fs que l�on veut produire soient comprises dans sa plage de fonctionnement).

Un des avantages de cette m�thode est que les fr�quences produites b�n�ficient de la pr�cision et de la stabilit� de la fr�quence de r�f�rence.

Ce principe est surtout utilis� dans les � synth�tiseurs de fr�quence � (voir page suivante), qui permettent d�utiliser des oscillateurs de r�f�rence à quartz (fr�quence �l�v�e) et qui produisent des fr�quences plus facilement variables avec des pas quelconques.

Synth�tiseur de fr�quences.

Objectif : pour le moment l�objectif est seulement de produire une porteuse,

c�est à dire une tension sinusoÏdale de fr�quence fixe pr�cise,

trÈs stable et programmable par pas de 5kHz dans la bande autoris�e de

41,110 MHz à 41,200 MHz. Il ne s�agit pas encore de moduler la porteuse,

ceci sera �tudi� par la suite (par. V).

Pour correspondre aux notations du thÈme :

La tension u des sch�mas pr�c�dents (sortie du filtre, commande du VCO) sera maintenant appel�e VPLL

La fr�quence d�entr�e de la PLL (Fe) sera appel�e FR

� � de sortie � � (FS) � � Fmes

Par rapport au multiplicateur de fr�quence �tudi� page pr�c�dente, on ajoute :

Un second diviseur de fr�quence (/ R) en cascade avec l�oscillateur de r�f�rence, qui permet d�obtenir le � pas � (FR = Fr�f / R), c�est à dire la variation �l�mentaire de fr�quence que l�on pourra obtenir pour la porteuse.

Un amplificateur qui permet :

d�obtenir une puissance d��mission suffisante.

d�adapter l�imp�dance de sortie du synth�tiseur à l�imp�dance de l�antenne et du cable de liaison.

Une fois que le pas d�sir� FR d�sir� est obtenu, il suffit de multiplier la fr�quence du pas par un nombre entier N pour obtenir toute fr�quence de sortie Fmes multiple du pas situ�e dans la plage de travail du VCO.

En effet, la boucle �tant verrouill�e :

FV = FR = 5 kHz

Fmes = N Fv = N x 5 kHz

Ici l�oscillateur à quartz oscille à la fr�quence Fr�f = 10 245 kHz, donc le diviseur doit Être �gal à :

R = 10 245 / 5 = 2049

Le diviseur N (que l�on devrait appeler � multiplicateur �) varie de 2 en 2 car il y a un canal tous les 10 kHz, ses valeurs extrÊmes sont :

8222 pour une porteuse à 5 kHz x 8222 = 41,110 MHz

8240 � � � � 5 kHz x 8240 = 41,200 MHz

V � Application du synthÈtiseur de fr�quence à PLL à la modulation FM.

Nous n�envisagerons que le cas du thÈme, dans lequel le signal modulant est un simple signal logique TTL ; la porteuse modul�e n�aura donc que deux fr�quences possibles, et il s�agit plut�t d�une modulation FSK (Frequency shift keying) (trÈs utilis�e en BF pour les modems).

Le circuit de modulation, qui commande le VCO, est symbolis� ici par le symbole ci-dessous :

Ce circuit utilise deux capacit�s variables (diodes varicap) command�es par les tensions VPLL et Vmod .

L�entr�e VPLL est con�ue pour produire une variation assez importante de la fr�quence Fmes du VCO, de fa�on à pouvoir r�gler la fr�quence d�oscillation libre Fmes 0 (fr�quence centrale FS0) sur toute la bande FM autoris�e : Fmes min < 41,110 MHz et Fmes max > 41,200 MHz .

En revanche l�entr�e Vmod est con�ue pour ne produire qu�une variation limit�e, de fa�on à ne pas empi�ter sur les canaux d��mission voisins :

Vmod = 0 Fmes = N FR

Vmod = 5V Fmes = N FR + DFmes = N FR + 5 kHz

Le principe de ce modulateur est trÈs simple : il suffit d�empÊcher la PLL de r�agir aux variations de fr�quence Fmes caus�es par le signal modulant ; pour cela il faut choisir le filtre pour que la PLL soit lente devant la dur�e des impulsions positives de Vmod . A chaque impulsion, Fmes augmente d�environ 5 kHz, donc la PLL d�verrouille durant 300 �s ; mais la tension VPLL n�a pas le temps de varier, et dÈs la fin de l�impulsion la fr�quence Fmes reprend la valeur normale (porteuse) et la PLL reverrouille.

En revanche, si le filtre de la PLL �tait trop rapide, la modulation ne pourrait avoir lieu car à l�instant oÙ Vmod passerait à 5V, la fr�quence Fmes tendrait à augmenter, mais la PLL verrouill�e r�agirait trÈs vite et la maintiendrait �gale à N FR .

Il faut donc concevoir le filtre pour :

que la PLL ne r�agisse pas ou trÈs peu durant l��tat haut de chaque impulsion de Vmod (300 �s).

que la PLL r�agisse faiblement en qqes ms aux petites perturbations de la fr�quence de la porteuse Fmes.

que la PLL r�agisse fort en qqes dizaines de ms à l��cart entre Fmes et FR durant la phase de capture jusqu�au verrouillage.

Nous ferons une �tude plus d�taill�e de l�ensemble � comparateur de phase + filtre � dans le paragraphe suivant (� Propri�t�s particuliÈres du montage utilis� dans le thÈme �), mais il suffit pour le moment de v�rifier que la constante de temps du filtre choisie par le constructeur satisfait bien aux trois imp�ratifs pr�c�dents :

![]()

Cette valeur est donc correcte tant pour la modulation FM que pour le fonctionnement de la boucle.

V�rifions (calcul approch�) que la plage de capture est assez large ; on a vu qu�elle d�pend principalement de la bande passante du filtre passe-bas, dont la fr�quence de coupure est :

![]()

Une diff�rence de fr�quence de 16 Hz de FV sur FR correspond sur Fmes à une diff�rence de fr�quence :

DFmes = ( 16 Hz) x N = ( 16 Hz) x 8200 = 131,2 kHz

Si l�on rÈgle la fr�quence centrale du VCO aux environs (ce r�glage est d�licat !) du milieu de la bande autoris�e ( Fmes0 = 41,155 Mhz) alors la capture pourra s�effectuer approximativement de Fmes 0 - DFmes = 41,024 MHz à Fmes 0 + DFmes = 41331 MHz, donc toute la bande sera bien couverte.

VI � Les propri�t�s particuliÈres du montage utilis� dans le thÈme.

La particularit� la plus importante est l�utilisation d�un � comparateur phase-fr�quence � à la place d�un simple comparateur de phase.

Ecart de phase et �cart de fr�quence.

Les chronogrammes ci-dessus donnent un exemple de PLL verrouill�e, avec vV en retard sur vR. Le troisiÈme signal nomm� � uDF � donne un exemple simplifi� de tension dont la valeur moyenne est l�image du d�phasage.

Ici le d�phasage est positif, donc la fr�quence Fmes = N FV est sup�rieure à FS0 et la tension u = VPLL est sup�rieure à sa valeur de repos (4 V dans l�exemple pr�c�dent).

Les chronogrammes ci-dessus donnent un exemple de PLL non verrouill�e, en phase de capture avec FV < FR.

On voit que la diff�rence des deux fr�quences se traduit par une sorte de � d�phasage � DF, mais ce � d�phasage � est variable à la fr�quence (FR � FV) ; le signal � uDF � (simplifi�) pr�sente une valeur moyenne proportionnelle à l��cart de fr�quence (FR � FV). Cette valeur moyenne est �lev�e et agit sur le VCO de telle fa�on que FV augmente jusqu�au verrouillage FV = FR .

En conclusion un �cart de fr�quence peut toujours s�interpr�ter comme un �cart de phase.

Principe du comparateur de phase simple.

Avec un comparateur de phase simple nous avons vu que si la PLL est verrouill�e, les fr�quences FR et FV sont �gales, mais qu�il y a obligatoirement une diff�rence de phase constante entre vR et vV (sauf dans le cas trÈs particulier ou Fmes = N FV = FS0 fr�quence centrale du VCO) ; en effet c�est cette diff�rence de phase qui permet d�obtenir la valeur de u = VPLL qui fait osciller le VCO à la bonne fr�quence (revoir les exemples (III, 5 ,a) page 4 et revoir les caract�ristiques pages 2, 3 et 4).

Principe du comparateur phase-fr�quence.

L�avantage du comparateur phase-fr�quence est de permettre, une fois la PLL verrouill�e, d�obtenir non seulement que vV ait la mÊme fr�quence que vR , mais aussi la mÊme phase.

Nous avons vu qu�avec le comparateur simple, un d�phasage est n�cessaire pour produire la tension u = VPLL de commande du VCO. Le comparateur phase-fr�quence n�a pas besoin de ce d�phasage, car il est capable de produire une tension d��quilibre u = VPLL , �labor�e pendant la capture et m�moris�e par le filtre (condensateur). Il n�y a plus besoin de point de repos (4 V pr�c�demment) et une fois la boucle verrouill�e il n�y a plus besoin de d�phasage. La tension d��quilibre VPLL produite va de 0 à 8 V selon la fr�quence Fmes d�sir�e.

a) Exemple avec utilisation de la sortie 13 (PD out) du Motorola MC145170.

V PLL (u)

![]() Commen�ons par cet exemple, qui n�est pas le montage du thÈme

mais qui est d�approche plus simple.

Commen�ons par cet exemple, qui n�est pas le montage du thÈme

mais qui est d�approche plus simple.

La sortie PD out fonctionne de la fa�on suivante (voir doc

Motorola) :

PLL verrouill�e vs et ve mÊme fr�quence et mÊme phase : PD out est à haute imp�dance.

PLL verrouill�e, si une perturbation cr�e une petite avance de phase de vV sur ve : impulsions trÈs courtes de valeur 0 sur PD out puis retour à haute imp�dance.

PLL verrouill�e, si une perturbation cr�e un petit retard de phase de vV sur vR : impulsions trÈs courte de valeur 5V sur PD out puis retour à haute imp�dance.

PLL non verrouill�e (capture) si FV > FR impulsions de valeur 0 sur PD out, de dur�e proportionnelle à l��cart de fr�quence, puis retour à haute imp�dance.

PLL non verrouill�e (capture) si FV < FR impulsions de valeur 5V sur PD out, de dur�e proportionnelle à l��cart de fr�quence, puis retour à haute imp�dance .

Toutes ces impulsions sont à la fr�quence du pas FR = FV = 5kHz. Avec ce montage supposons que le VCO est aliment� entre 0 et 5V.

Imaginons que la fr�quence centrale du VCO est 41,12 MHz pour une tension u =V PLL de 2,5 V, et que la fr�quence du � canal � que nous voulons obtenir est 41,18 MHz , correspondant par exemple à u =V PLL = 4V.

A la mise en route, le condensateur C est d�charg�, donc u = V PLL part de 0. Cela impose au VCO d�osciller à la fr�quence minimale (exemple Fs = 40,8 MHz). La fr�quence FV = Fs / 8200 = 4,97 kHz est inf�rieure à FR = 5 kHz, donc PD out pr�sente de larges impulsions 5V.

A chaque impulsion 5 V, C se charge, et aprÈs chaque impulsion C garde sa charge car PD out revient à haute imp�dance et la r�sistance d�entr�e du VCO est trÈs grande. Progressivement u = V PLL augmente, ce qui augmente les fr�quences Fmes et FV = Fmes / N ; par suite l��cart de fr�quence entre FV et FR diminue, donc les impulsions de PD out sont de plus en plus courtes. A un moment l��quilibre est atteint et la PLL se verrouille avec u = V PLL = 4 V = cte (tension d��quilibre) et Fmes = 41,18 MHz = cte ; VV et VR ont alors mÊme fr�quence et mÊme phase.

Ensuite en th�orie la sortie PD out reste en permanence à haute imp�dance (à part de trÈs courtes impulsions non op�rantes, voir doc Motorola). En pratique les perturbations provoquent de petites corrections en plus ou en moins (impulsions PD out vers 5V ou vers 0).

On peut dire que la tension d��quilibre u = V PLL = 4 V a �t� fabriqu�e par l�ensemble � comparateur phase-fr�quence + filtre � pendant la capture, puis a �t� m�moris� par le condensateur. Ainsi les phases de VV et VR peuvent Être �gales, car il n�y a pas besoin de d�phasage pour entretenir la valeur de u = V PLL.

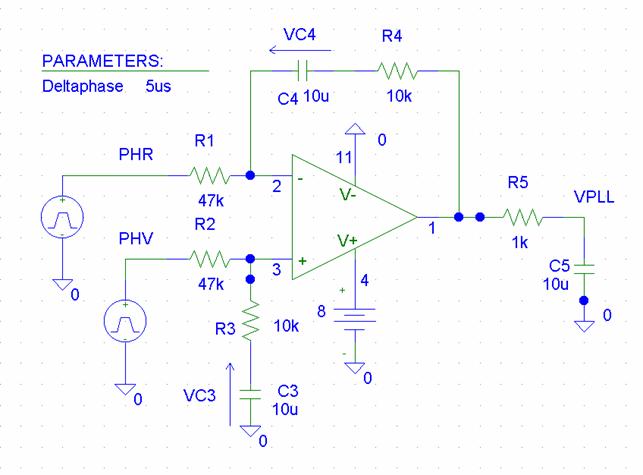

b)

Exemple avec le montage du

thÈme : sorties 14 (FR) et 15 (FV) du MC145170.

Revenons à l�alimentation r�elle du VCO entre 0 et 8V.

Les sorties PHR (14) et PHV (15) sont configur�es de la fa�on suivante (voir doc Motorola) :

PLL verrouill�e vV et vR mÊme fr�quence et mÊme phase : PHR et PHV restent à 5V.

PLL verrouill�e, si une perturbation cr�e une petite avance de phase de vV sur vR : impulsions trÈs courtes de valeur 0 sur PHV (le reste du temps à 5V).

PLL verrouill�e, si une perturbation cr�e un petit retard de phase de vV sur vR : impulsions trÈs courtes de valeur 0 sur PHR (le reste du temps à 5V).

PLL non verrouill�e (capture) si FV > FR impulsions de valeur 0 sur PHVR de dur�e proportionnelle à l��cart de fr�quence, puis retour à 5V.

PLL non verrouill�e (capture) si FV < FR impulsions de valeur 0 sur PHR de dur�e proportionnelle à l��cart de fr�quence, puis retour à 5V.

La fr�quence des impulsions est celle de FR = 5 kHz ; quand les sorties � restent à 5V � elles pr�sentent à chaque p�riode (200 �s) une trÈs courte impulsion vers 0. Ces impulsions sont inop�rantes, dans nos simulations nous leur avons donn� une dur�e de 1 �s.

Imaginons que la fr�quence centrale du VCO est 41,12 MHz pour une tension u =V PLL de 4 V, et que la fr�quence du � canal � que nous voulons obtenir est 41,18 MHz , correspondant par exemple à u =V PLL = 4,5V.

A la mise en route les condensateurs sont vides et VPLL = 0. Donc Fmes part de Fmes min (exemple 41 MHz) et FV < FR ; par suite :

PHV � reste � à 5V (C3 se charge, Vc4 et V+ tendent vers 5V).

PHR pr�sente des impulsions (0 V) assez larges au d�part ; la valeur moyenne de V- est inf�rieure à V+, donc la tension d�entr�e diff�rentielle moyenne de l�AOP est positive, sa tension de sortie moyenne est positive et C5 se charge, donc VPLL augmente, ce qui augmente la fr�quence Fmes produite par le VCO.

Quand Fmes atteint la valeur souhait�e 41,18 MHz, alors FV = FR et la PLL se verrouille. On a alors aux bornes de C5 VPLL = 4,5V. Comme Vv est en phase avec VR il n�y a plus d�impulsions sur PHR et PHV, qui restent à 5V. Les tensions aux bornes des condensateurs VPLL , Vc3 et Vc4 sont constantes, il n�y a pas de courant à travers les r�sistances, et l�on a :

V+ = Vc3 = 5V

V- = V+ = 5 V (l�AOP est en r�gime lin�aire car Vs de l�AOP = VPLL = 4,5V).

Vc4 = 0,5 V(5V � 4,5V).

Ces valeurs sont les valeurs d��quilibre de la PLL pour Fmes = 41,18 MHz. La tension VPLL d��quilibre est m�moris�e par le condensateur C5 .

Pour examiner la r�action de la PLL aux perturbations de Fmes autour de cet �quilibre, il faut reproduire artificiellement les potentiels d��quilibre car la simulation est en boucle ouverte.

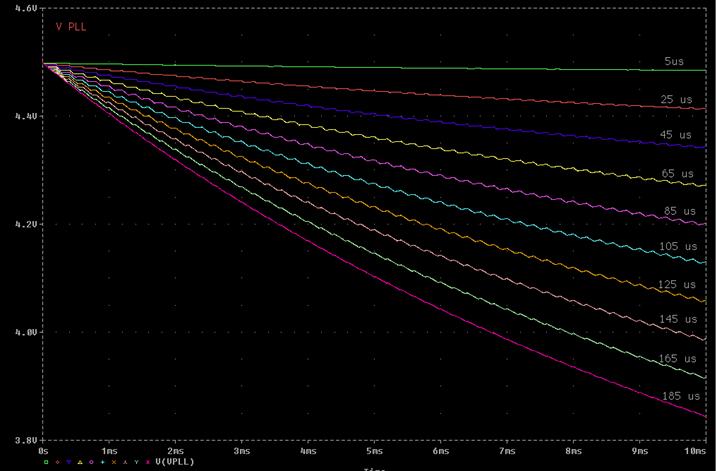

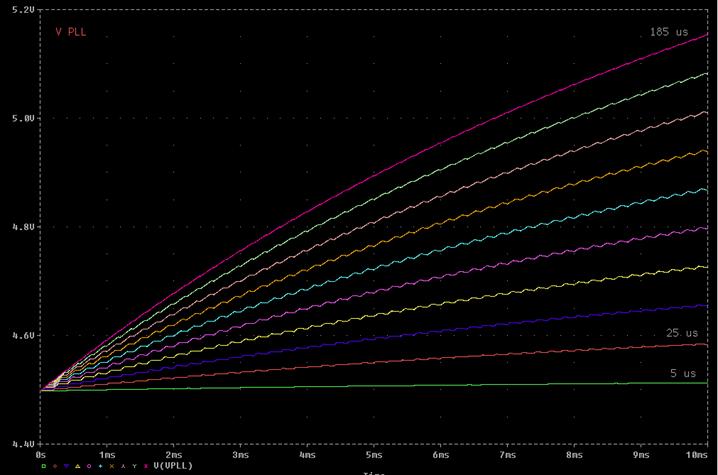

Donc on prendra comme conditions initiales des condensateurs (IC) les valeurs Vc5 = 4.5 V, Vc4 = 0.5V et Vc3 = 5V. La simulation est à la fois temporelle et param�trique :

Fr�quence des sources PHR et PHV 5 kHz (p�riode 200 �s)

Temps final 10 ms

ParamÈtre � Deltaphase � qui repr�sente la dur�e des �tats bas de PHV ou PHR ; on fait varier Deltaphase de 5�s à 185 �s pour tester la r�action de la PLL à diff�rents �carts , d�abord dans le sens FV > FR puis Fv < FR .

La premiÈre simulation montre qu�en l�absence d��cart VPLL reste stable (�quilibre), et que si FV tend à augmenter la boucle contre-r�agit en diminuant VPLL (cte de temps 10 ms), ce qui ramÈne Fmes à la valeur correcte.

La seconde simulation montre que si FV tend à diminuer la boucle contre-r�agit en augmentant VPLL .

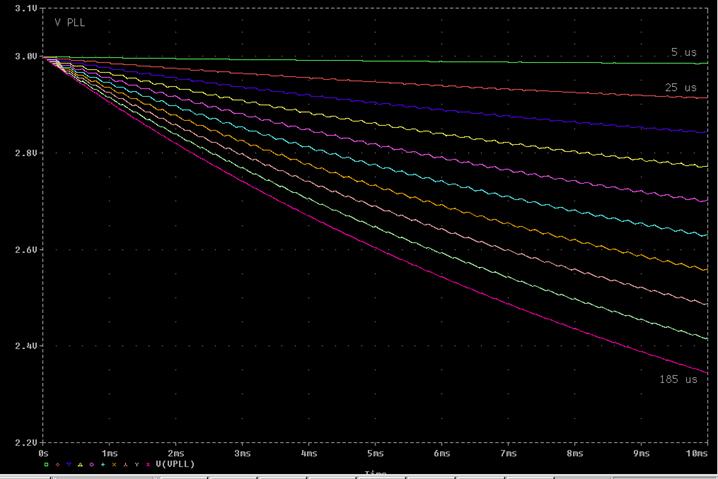

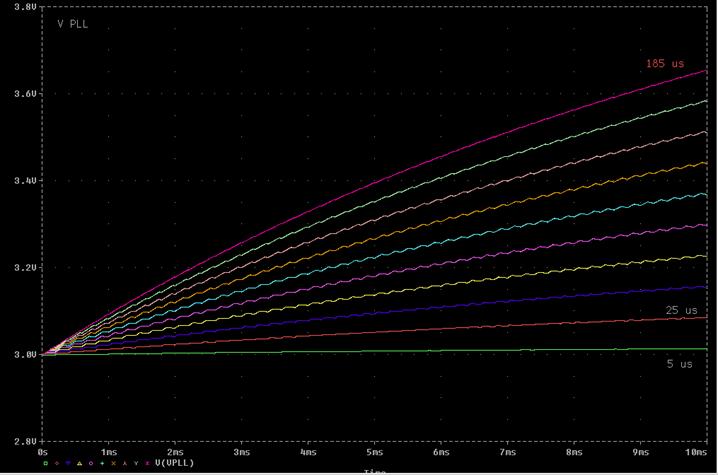

La derniÈre page reproduit les mÊmes simulations avec un point d��quilibre Fmes diff�rent (ex. Fmes = 41,12 MHz pour VPLL = 3 V donc on initialise Vc5 = 3 V, Vc4 = 2 V et Vc3 = 5 V).

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 4869

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved