| CATEGORII DOCUMENTE |

| Bulgara | Ceha slovaca | Croata | Engleza | Estona | Finlandeza | Franceza |

| Germana | Italiana | Letona | Lituaniana | Maghiara | Olandeza | Poloneza |

| Sarba | Slovena | Spaniola | Suedeza | Turca | Ucraineana |

DOCUMENTE SIMILARE |

|

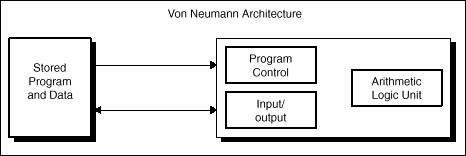

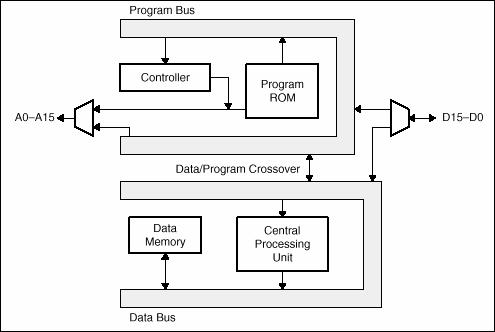

La structure de VON NEUMAN, utilisée par les microprocesseurs

(architecture des x86) depuis 40 ans, consiste à placer les données et le

programme sur un bus commun. Inconvénient

majeur de cette structure : on ne peut lire

une donnée ou une instruction qu’en un

seul cycle.

Fig. 3 Architecture de Von Neuman.

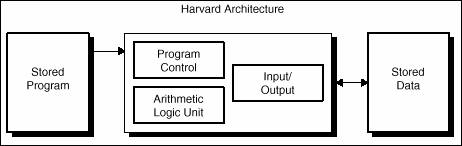

Lorsque la vitesse d’exécution d’un programme est importante, il

est préférable d’utiliser la structure de HARVARD ou mémoire programme et mémoire données sont séparées. Ainsi en un seul cycle, le processeur

pourra lire l’instruction et la donnée.

Fig. 4 : Architecture de Harvard .

La structure de HARVARD est cependant pénalisante par le nombre de

broches utilisées et le nombre de boitiers mémoires utilisés. T.I. comme de

nombreux autres constructeurs (INTEL avec le MCS 51, MICROCHIP avec les

microcôntroleurs PIC) utilise une structure de HARVARD modifiée, qui

consiste à n’utiliser qu’un bus commun pour les accès en mémoire externe

(architecture de VON NEUMAN) et à utiliser une structure de HARVARD pour

les accès en mémoire interne. Charge ensuite au programmeur, si la taille de

la mémoire programme ou de la mémoire données est trop importante, de

placer en mémoire interne le bout de programme et de données qui demande

une rapidité optimale d’exécution.

Fig. 5 : Structure de Harvard modifiée.

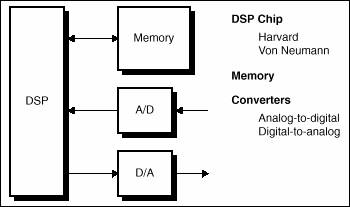

Le DSP utilise de la mémoire externe sur un bus commun.

Certaines applications nécessitent des calculs en temps réel sur des échantillons :

filtrage numérique,

contrôle moteur,

reconnaissance vocale,

modems, fax, etc

Pour ces applications il est nécessaire de faire des multiplications et additions (Y=BC+A), instruction MAC (Muliply And Accumulate), en un cycle d’horloge. Ces applications nécessitent des microcôntroleurs spécifiques dédiés au traitement du signal : les DSP (Digital Signal Processor).

Cœur d’un DSP : (Cf figure 6)

le DSP doit être capable de traiter une somme de produits en un cycle machine, ce qui implique d’avoir 2 bus (un pour les coefficients et un pour les échantillons), un multiplieur, une ALU (pour l’addition) et un Accumulateur.

N

![]()

i=0

![]()

Fig. 6 : Cœur d’un DSP.

Fig. 7 : Schéma de principe de la structure interne du TMS320C5X.

Le bus de programme véhicule l’instruction et la constante associée (coefficient a(i)) et le bus de données véhicule l’échantillon. Le DSP utilise, en plus, une architecture parallèle, puisque en un seul cycle il est possible de faire une multiplication de 16*16 bits, un décalage du résultat, une addition et une manipulation de la mémoire programme.

Vue d’ensemble de la famille TMS320 : (pour plus de détails, se reporter aux annexes)

Cette famille est constituée de processeurs à virgules fixes 16 bits (processeurs C1X, C2X et C5X) et de processeurs à virgules flottantes 32 bits (C3X et C4X) et 64 bits (C8X). Ces processeurs concurrencent directement les applications spécifiques à base d’ASIC.

Les DSP à virgules fixes : moins chers mais erreurs de calcul constantes, ce sont les plus utilisés.

Les DSP à virgules flottantes : on fait intervenir une mantisse et un exposant. Dans ce cas, l’erreur par overflow est limitée puisque on bénéficie d’une dynamique plus importante. Ces DSP sont utilisés pour les applications audio.

le DSP TMS320C80, processeur à virgules flottantes, est utilisé en parallèle avec d’autres C80, pour les applications vidéo.

Il existe 3 principaux outils de développement proposés par Texas Instrument :

Le Starter Kit (noté DSK), prix inférieur à 1000,00 F,

Le TMS320C50 EVM (module d’évaluation),

l’émulateur (noté XDS), prix supérieur à 10.000,00 F.

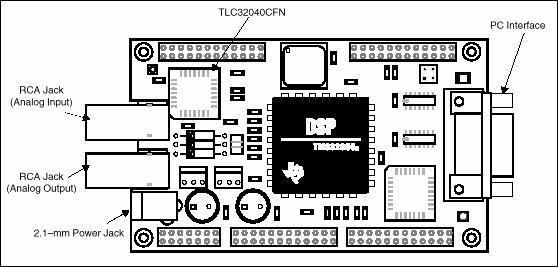

Le Starter Kit (DSK) permet une évaluation du DSP dans les domaines du contrôle et du traitement du signal audio. Le Starter Kit comporte : ( Cf figure 8)

une carte composée d’un TMS320C50 (40 MHz) , d’un CAN, CNA (le TLC32040), de 10 Kmots de mémoire interne, d’une PROM et d’une liaison RS232 pour télécharger le programme via un PC.

un assembleur-linker et un debugger.

Fig. 8 : carte du Starter Kit.

Le TMS320C50 EVM : ce module d’évaluation reprend le même principe que le Starter Kit mais est plus complet et donc plus cher. Ce kit possède une mémoire de 64 Kmots de SRAM sur la carte que l’on connecte sur le bus ISA du PC.

Fig. 9 : Kit EVM.

L’émulateur XDS utilise la liaison JTAG avec le DSP pour lire la mémoire, placer des points d’arrêt, faire du mode pas à pas, etc

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 1617

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2026 . All rights reserved