| CATEGORII DOCUMENTE |

| Bulgara | Ceha slovaca | Croata | Engleza | Estona | Finlandeza | Franceza |

| Germana | Italiana | Letona | Lituaniana | Maghiara | Olandeza | Poloneza |

| Sarba | Slovena | Spaniola | Suedeza | Turca | Ucraineana |

DOCUMENTE SIMILARE |

|

Le port série synchrone est constitué de 6 broches :

3 broches pour l’émission :DX (données en émission), CLKX (horloge bit en émission)

et FSX (horloge trame en émission),

3 broches pour la réception :DR (données en réception), CLKR (horloge bit en réception)

et FSR (horloge trame en réception).

Ce port est full duplex (envoie et réception de données possibles en même temps). La vitesse de transmission maximale lorsqu’on utilise la fréquence interne du processeur est de 5 Mbits/s (pour Fclk = 40 MHz).

Ce port permet une communication bidirectionnelle avec un autre DSP (Cf figure 54) ou bien peut être utilisé pour communiquer avec un CAN-CNA série fonctionnant sur le même principe (série TLC 320C4X).

Fig.54 : Exemple de communication full duplex entre 2 DSP à l’aide du port série.

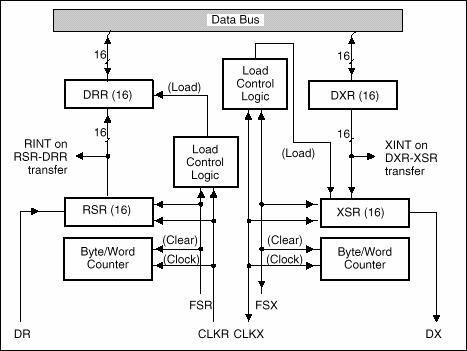

En émission, l’utilisateur charge la donnée à transmettre dans un premier registre DXR. Ce registre est ensuite transféré en parallèle dans le registre à décalage XSR à partir duquel les bits sont transmis en série sur la broche DX.

En réception, les bits reçus en série sur la broche DR chargent en série le registre à décalage RSR. Lorsque le registre à décalage est plein, il est automatiquement chargé en parallèle dans le registre DRR accessible à l’utilisateur.

Les registres DRR et DXR sont mappés en mémoire. Le contrôle du port série s’effectue par l’intermédiaire du registre SPC (Serial Port Control).

Fig. 55 :Architecture interne du port série.

On peut résumé le principe de l’émission et de la réception par le schéma figure 56.

Fig. 56 : Principe de l’émission / réception en utilisant les interruptions

|

FREE |

SOFT |

RSR FULL |

XSR EMPT |

XRDY |

RRDY |

IN1 |

IN0 |

RRST |

XRST |

TXM |

MCM |

FSM |

FO |

DLB |

RES |

XRDY est mis à 1 lorsque XINT passe à 1 soit lors du transfert de données de DXR vers XSR. RRDY est mis à 1 lorsque RINT passe à 1 soit lors du transfert de données de RSR vers DRR. Ces bits permettent de faire du polling Si MCM = 0 CLKX fourni par le circuit extérieur Si MCM = 1 CLKX fourni par le Clock interne TCLKX = TCLKOUT/4 L’écriture dans les bits 1 à 5 n’est prise en compte qu’après un

reset. Il faut donc écrire dans les bits 1 à 5 et mettre RRST (reset du

récepteur) et/ou XRST (reset de l’emetteur) à 0 puis tout en gardant les

valeurs des bits de 1 à 5 mettre RRST et/ou XRST à 1 pour valider le reset

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Fig. 57 :description du registre de contrôle SPC.

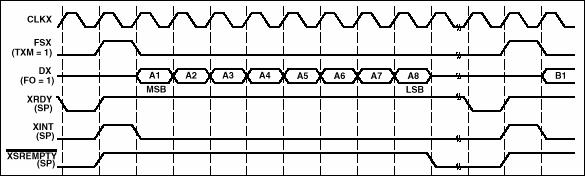

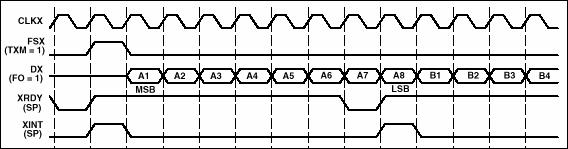

En mode burst, chaque paquet de données (8 ou 16 bits) est envoyé à la suite d’un signal de burst (broche FSX). Cette impulsion apparait dés que le contenu de DXR est transféré vers XSR.

Fig. 58 :Emission en mode burst avec FSX généré en interne à chaque écriture dans DXR

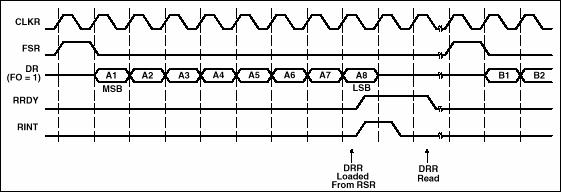

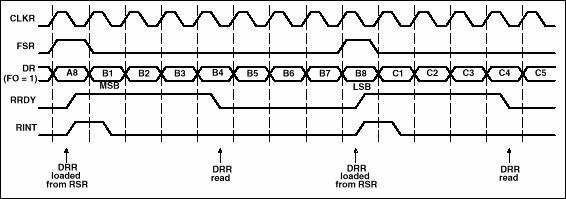

Fig. 59 :Réception en mode burst.

Lors de la réception en mode burst, FSR est toujours généré de façon externe.

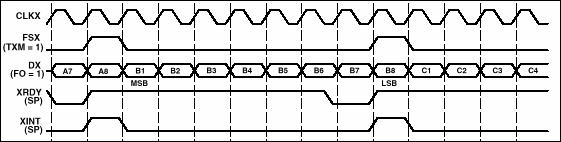

Si on augmente la fréquence maximale des paquets, les temps d’inactivité entre le transfert diminuent pour arriver à une durée minimale entre les transferts de 8 ou 16 (selon FO) période de CLKX. Dans le cas de ce fonctionnement en mode burst à la cadence maximale (Cf figure 60 et 61), les bits sont transmis en continu et donc le signal de synchronisation trame FSX ne sert plus, sauf pour lancer le premier octet ou mot. Pour ces transferts par paquet de données, il existe un mode de fonctionnement continu.

Fig. 61 : Emission en mode burst à la fréquence maximale de fonctionnement.

Fig. 61 : Réception en mode burst à la fréquence maximale de fonctionnement.

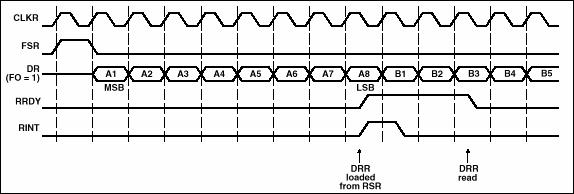

En mode de fonctionnement continu, le signal de synchronisation trame sur FSX/FSR n’est plus nécessaire pour chaque paquet de données.

La transmission se fait au rythme maximal, déterminé par CLKX/CLKR. Seule une première impulsion sur FSX/FSR est nécessaire pour lancer la communication.

Dés que l’émetteur arrête l’envoie de données, le récepteur ne génère plus d’interruption et attend le nouveau signal FSX pour reprendre la lecture des paquets.

Fig. 62 :Emission en mode continu.

Fig. 63 :Réception en mode continu.

Fig. 64 :Communication unidirectionnelle entre 2 DSP.

* Device 0 – Transmit side

;Setup SPC as CLK source and internal frame sync

SPLK #0038h, SPC ;Set TXM=MCM=FSM=1,TDM=DLB=FO=0.

;And put SP into reset ,(XRST=RRST=0)

SPLK #00F8h, SPC ;Take SP out of reset

;Setup interrupts

SPLK #0ffffh, IFR ;clear IFR

SPLK #020h, IMR ;Turn on XINT

CLRC INTM ;enable interrupts

LDP #0

ILOOP BCND SENDZ, BIO ;Wait for ready–to–receive

B ILOOP ;from other device

SENDZ LACL #0 ;First transmit/write value is 0

LAR AR7, #9000h ;Setup where to write

SACL * ;Write first value

SACL DXR ;Transmit first value

SELF1 B SELF1 ;Wait for interrupts

XMT_ISR LACC AR7 ;Check if past 0x0b000

SUB #0B000h ;i.e. end of block

BCND END_SERP,GEQ ;Go to tight loop if so Add one and transmit

LACL *+ ;Load value

ADD #1 ;Add one

SACL * ;Write value

SACL DXR ;Transmit value

RETE

END_SERP B END_SERP ;Sit in tight loop after ;block is complete.

Device 1 – Receive

;Set SP as CLK, frame sync receive

SPLK #0008h, SPC ;Set TXM=MCM=DLB=FO=0,FSM=1.

;And put SP into reset (XRST=RRST=0)

SPLK #00C8h, SPC ;Take SP out of reset

;Setup interrupts

SPLK #0ffffh, IFR ;clear IFR

SPLK #010h, IMR ;Turn on RINT

CLRC INTM ;Enable interrupts

LDP #0

LAR AR7, #9000h ;Setup where to write

;received data

CLRC XF

;Signal ready to receive

SELF1 B SELF1 ;Wait for interrupts

RCV_ISR LACL DRR ;Load received value

SACL *+ ;Write to memory block

LACC AR7 ;Check if past 0x0b000

SUB #0b000h ;i.e. end of block

BCND END_SERP,GEQ ;Go to tight loop if so

END_SERP B END_SERP ;Sit in tight loop after

;block is complete.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 881

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved