| CATEGORII DOCUMENTE |

| Bulgara | Ceha slovaca | Croata | Engleza | Estona | Finlandeza | Franceza |

| Germana | Italiana | Letona | Lituaniana | Maghiara | Olandeza | Poloneza |

| Sarba | Slovena | Spaniola | Suedeza | Turca | Ucraineana |

DOCUMENTE SIMILARE |

|

Le C5X peut adresser 64 Kmots de mémoire programme et 96 Kmots de mémoire données (64 Kmots de mémoire données privée et 32 Kmots de mémoire globale, mode multiprocesseur).

Les instructions sont codées sur 1 ou 2 mots de 16 bits. Il parait évident que si l’on code les adresses d’opérandes sur 16 bits, deux mots sont nécessaires pour coder celles-ci. Le temps d’exécution qui en résulterait serait de 2 cycles et donc non compatible avec les performances espérées pour le DSP. Dans les différents modes d’adressage proposés, le constructeur a eu la volonté de coder une instruction sur 16 bits. Ces modes d’adressage sont :

l’adressage direct ( instructions codées sur 16 bits),

l’adressage des MMR ( instructions codées sur 16 bits),

l’adressage indirect (instructions codées sur 16 bits),

l’adressage immédiat court ou long (respectivement codés sur 1 ou 2 mots),

l’adressage par registre BMAR ou DBMR.

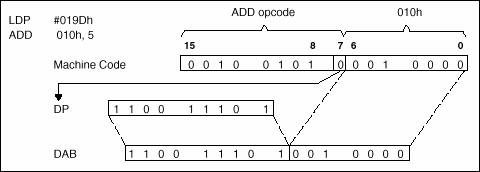

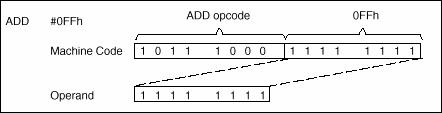

Fig. 16 : Principe de l’adressage

direct. L’adresse de

l’opérande est définie par une adresse (DMA :

Direct Memory Adresse) sur 7 bits qui correspond à un espace adressable

de 128 mots dans une page définie par DP

(Data Pointer) registre de 9 bits.

Cette découpe par pages de 128 mots permet d’avoir une instruction en

adressage direct codée sur 16 bits.

Exemple :

.ds 300h ; directive d’assemblage, déclaration des données

COMPT .word 25 ; déclaration de la variable COMPT à l’adresse 300h initialisée à 25

.ps 0900h

.entry ; début du programme à l’adresse 900h, mémoire SARAM

LDP #8h ; DP

LACL 07h , ACCL (407h) , les 16 bits de poids faible de ACC sont chargés

;par la valeur à l’adresse 407h

LDP #6 ; DP

LACHL VAL ; ACCH (300h) soit ACCH = 25

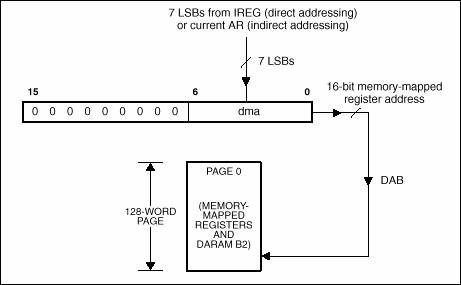

28 registres sont

mappés dans l’espace mémoire page 0 ainsi que 64 autres registres (réservés

pour le contrôle des périphériques). Ce mode d’adressage permet d’accéder

aux registres MMP sans changer la

valeur du DP et fonctionne comme

un adressage direct avec une mise à 0 des 9 bits de poids forts de

l’adresse (page 0). 4 instructions permettent ce mode d’adressage : LAMM Load

accumulator with MMR LMMR : Load MMR SAMM : Store ACC in MMR SMMR : Store MMR

Fig. 17 : Principe de l’adressage des MMR.

Fig. 18 : Registres mappés à la page 0.

Exemple

.mmregs ; possibilité pour l’utilisateur de placer dans l’instruction sur le MMR le nom du registre

LAMM 07h ; ACC = PMST

LAMM PMST ; ACC = PMST dans ce cas, le compilateur remplace PMST par son adresse soit 07h

LMMR GREG, #300h ; GREG prend la valeur placée à l’adresse 300h

SAMM IOWSR ; IOWSR = ACC

SMMR CWSR, #300h ; La valeur de CWSR est placé à l’adresse 300h

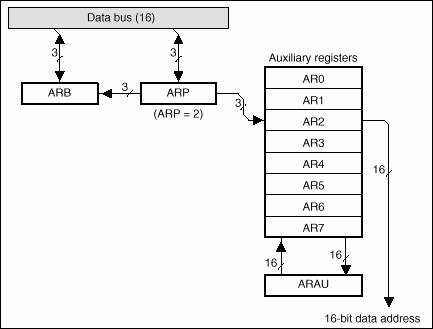

Cet adressage se fait en utilisant un des 8 registres auxiliaires (ARn). Le registre courant est défini par le pointeur de registres auxiliaires ARP.

L’intérêt de l’utilisation des registres auxiliaires réside dans les possibilités de calcul offerte par l’ ARAU, ce calcul se faisant en parallèle du CALU.

Fig. 19 : Principe de l’adressage indirect.

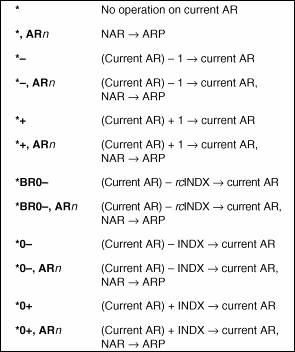

Les huits registres ARn sont connectés à l’ARAU et on peut ainsi obtenir une post-incrémentation ou décrémentation de 1(*+ ou *-), du registre auxiliaire courant, dans l’instruction. On peut de plus (cas de lecture dans une matrice) incrémenter ou décrémenter le registre auxiliaire courant de la valeur comprise dans INDX (*0+ ou *0-).

Exemple : supposons que AR6 soit sélectionné (ARP = 6) et contienne 384h

ADD *+ ; ACC ACC + [AR6] AR6 = AR6 + 1

Donc cette instruction permet de faire l’addition de l’accumulateur avec le contenu de l’adresse 384h et de positionner le pointeur courant vers l’adresse suivant pour la prochaine instruction.

Le contenu du registre INDX peut servir de d’incrément ou de décrément, la syntaxe est alors :

ADD *0+ ; ACC ACC + [AR6]

; AR6 = AR6 + INDX +1

Ceci permet de lire une colonne entière d ‘une matrice par exemple.

Lors d’un adressage indirect, il est possible de spécifier le prochain registre courant.

ADD *, AR2 ; ACC ACC + [AR6] ; ARP = 2

Fig. 20 : Les différentes solutions d’adressage indirect.

Exemple : à l’adresse 300h il y a la valeur 3h et à l’adresse 301h il y a la valeur 10h

LAR AR0, #300h ; AR0 = 300h

LACL #11FFh, AR0 ; ACC = 000011FFh ARP AR0

ADD *+ ; ACC = 00001202h AR0 = 301h

ADD *-, 2, AR1 ; ACC = 00001202h + 10h * 4 AR0 = 300h ARP AR1

Exemple :

SPLK #300h, AR7 ; AR7 = 300h

MAR *, AR7 ; ARP = 7, cette instruction permet de spécifier le pointeur courant

Exemple :

* This routine uses indirect

addressing to calculate the following equation: 10

–––––

X(I) x Y(I)

/

–––––

I = 1 * The routine assumes that the X

values are located in on-chip RAM block B0, * and the Y values in block B1. The

efficiency of the routine is due to the * use of indirect addressing and

the repeat instruction. SERIES MAR *,AR4 ;ARP POINTS TO ADDRESS

REGISTER 4. SETC

CNF ;CONFIGURE BLOCK B0 AS PROGRAM MEMORY. LAR

AR4,#0300h ;POINT AT BEGINNING OF DATA MEMORY. RPTZ

#9 ;CLEAR ACC AND PREG; REPEAT NEXT INST.

10 TIMES MAC 0FF00h,*+ ;MULTIPLY AND ACCUMULATE; INCREMENT AR4. APAC ;ACCUMULATE LAST PRODUCT. RET ;ACCUMULATOR CONTAINS RESULT.

Adressage indirect en bit reverse :

Cet adressage est utilisé pour le calcul de la FFT. L’adressage indirect en bit reverse est donné à la figure 20.1 pour le calcul de la FFT pour 8 points. Pour cela on charge dans INDX la valeur 4 et les adresses sont obtenues à partir de l’adresse de départ dans AR2 par ajout de INDX avec propagation de la retenue binaire de gauche à droite.

|

Instructions |

Valeurs du registre AR2 |

lecture du tableau des x(i) |

|

LAR AR2,#080h |

080h |

x(0) = (AR2) |

|

MAR *,AR2 |

AR2= pointeur courant | |

|

SPLK INDX, #4 |

080h | |

|

LAC *BR0+ |

x(0) |

|

|

LAC *BR0+ |

x(4) |

|

|

LAC *BR0+ |

x(2) |

|

|

LAC *BR0+ |

x(6) |

|

|

LAC *BR0+ |

x(1) |

|

|

LAC *BR0+ |

x(5) |

|

|

LAC *BR0+ |

x(3) |

|

|

LAC *BR0+ |

x(7) |

Fig. 20.1 : Accès aux valeurs pour le calcul de la FFT sur 8 points.

Calcul de la FFT : (Fast Fourrier Transfrom)

Rappels : Le calcul du

spectre en fréquence d’un signal e(t) se fait grace à la transformée de

Fourrier notée E(f) qui est de la forme :

Exemple : la transformée de Fourrier d’un signal sinusoïdal de fréquence 10 Hz est donnée ci-dessous :

Le calcul numérique de la transformée de Fourrier ne peut se faire que sur un nombre d’échantillons fini et l’intégrale ne peut être qu’approximé par partie, ce qui nous donne la formule suivante appelée Transformée de Fourrier Discrète ou (TFD) :

![]() avec M

le nombre d’échantillons e(i)

avec M

le nombre d’échantillons e(i)

et E(k) la valeur de la TFD à la fréquence k/(MTe).

Pour 1024 échantillons, et Te = 1ms (période d’échantillonnage), la fenêtre fera 1 s et il faudra calculer plus de 1 Millions de multiplications et accumulations pour obtenir les 1024 échantillons E(k) fréquentiels, et obtenir la trace fréquentielle du signal.

Pour des calculs en temps réel et sur des signaux de fréquences supérieures à 100Hz, ce calcul est trop long. On fait alors appel à la FFT (Fast Fourrier Transform) qui fait appel à l’entrecroisement temporel des échantillons comme vu à la figure 20.1.

Fig. 21 : Tableau récapitulatif des

instructions utilisant l’adressage immédiat. Dans ce cas l’opérande est codée

dans l’instruction. Cette opérande peut être codée sur 8, 9, 13 bits dans

le cas adressage immédiat court ou sur 16 bits dans le cas d’un adressage

immédiat long (Cf figure 21).

Exemple :

ADD #1234h ; addition de 1234h à l’accumulateur. Instruction codée sur 2*16 bits

LDP #6 ; DP Instruction codée sur 16 bits

SPLK #259, 8 ; (308h) Instruction codée sur 2*16 bits

Dans l’exemple de la figure 22,

l’opérande codé sur 8 bits est additionné à l’accumulateur.

Fig. 22 : Exemple d’adressage court.

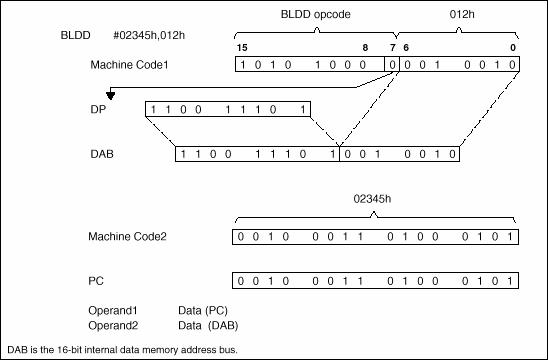

Remarque : il existe des instructions utilisant 2 opérandes, c’est le cas pour les instructions BLDD (BLock move from Data memory to Data memory), BLDP (BLock move from Data memory to Program memory) et BLPD (BLock move from Program memory to Data memory). Ces instructions sont utilisées pour rapatrier des données ou des instructions de la mémoire externe vers la mémoire interne pour accélérer les traitements ultérieurs.

Dans l’exemple de la figure 23, on utilise les 2 bus (programme et données) pour copier un mot à l’adresse 2345h vers l’adresse CE92h.

Fig. 23 : Exemple d’adressage immédiat utilisant 2 opérandes.

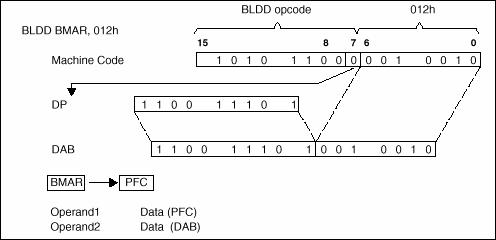

Il existe 2 registres BMAR et DBMR dont l’utilisation revient à faire de l’adressage immédiat (c’est à dire lecture de la donnée sur le bus programme) avec l’avantage de coder l’instruction sur 1 mot au lieu de 2 pour un adressage immédiat long. L’utilisation de BMAR permet de changer la valeur de l’opérande en cours de programme, ce que l’adressage immédiat ne permet pas.

Dans l’exemple de la figure 24,

on copie un mot placé à l’adresse pointée par BMAR vers l’adresse 12h à la

page 19Dh(valeur de DP).

Fig. 24 : Exemple d’adressage immédiat utilisant un opérande et le registre BMAR.

Remarque : BMAR est le registre utilisé par l’ALU et DBMR est l’accumulateur de la PLU.

Exemple : DAT0 DAT0 OU DBMR

OPL DAT0 ; DP = 6. DAT0 est à l’adresse 0 page 6. DBMR contient la valeur FFF0h

; et l’adresse 030h contient la valeur 01h

; Résultat : l’adresse 030h contient la valeur FFF1h

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 936

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved