| CATEGORII DOCUMENTE |

| Bulgara | Ceha slovaca | Croata | Engleza | Estona | Finlandeza | Franceza |

| Germana | Italiana | Letona | Lituaniana | Maghiara | Olandeza | Poloneza |

| Sarba | Slovena | Spaniola | Suedeza | Turca | Ucraineana |

DOCUMENTE SIMILARE |

|

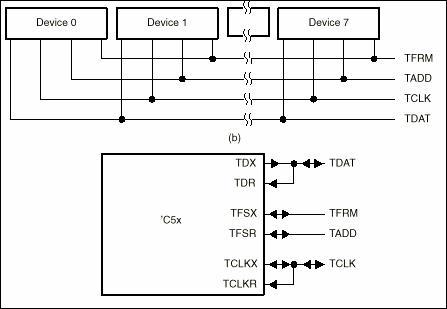

Ce port permet la connexion série de plusieurs TMS320C50 (jusqu'à huit) dans les applications multiprocesseurs.

Ce port, comme le port série synchrone, utilise 6 broches :

3 broches pour l’émission :TDX (données en émission), TCLKX (horloge bit en émission)

et TFSX (horloge trame en émission),

3 broches pour la réception :TDR (données en réception), TCLKR (horloge bit en réception)

et TFSR (horloge trame en réception).

Ce port peut fonctionner en mode série synchrone normal (CF chapitre 14) ou en mode multiprocesseur.

Ce port est constitué de 3 registres fonctionnant sur le même principe que les 3 registres DRR, DXR et SPC du port synchrone :

TRCV : registre de réception des données,

TDXR : registre d’émission des données,

TSPC :registre de configuration.

Plus 3 autres registres de gestion du mode multiprocesseur :

TCSR : choix du ou des canaux d’utilisation pour le processeur,

TRTA : Choix de l’adresse du processeur (8 bits) et de l’adresse du ou des destinataires (8 bits),

TRAD : contrôle du mode.

Principe de fonctionnement :

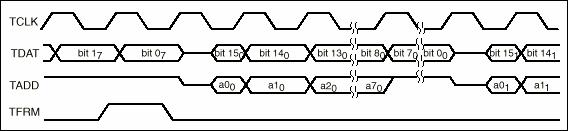

Le principe utilisé est celui du découpage temporel d’une trame en 8 intervalles de temps ou canaux. Chaque trame est déclenché par la broche TFSX et dure 16*8*Tbit, avec Tbit le temps nécessaire pour l’envoi d’un bit (Ce temps maximal est de 1 5 Mbits/s) pour Fclk = 40 MHz, comme pour le port série synchrone). Chaque canal voit l’émission de 16 bits.

Chaque processeur peut s’octroyer un ou plusieurs canaux. Prenons un exemple :

![]()

![]()

|

canal 0 |

canal 1 |

canal 2 |

canal 3 |

canal 4 |

canal 5 |

canal 6 |

canal 7 |

canal 0 |

canal 1 |

canal 2 |

||

|

t |

Device |

Device |

Device |

Device |

Device |

Device |

Device |

Device |

Device |

![]()

Dans cet exemple, il n’y a que 5 DSP de connecter sur le bus série. Chaque DSP émet vers un ou plusieurs DSP. Device 5 émet sur le canal 5 et 6.

La communication entre les DSP se fait sur 4 fils : (Cf figure 65 et 66)

un fil d’horloge TCLK (l’horloge est fournie par un seul DSP à tous les autres),

un fil de début de trame TFRM (comme pour TCLK, TFRM est fourni par un seul DSP),

un fil de donnée TDAT (ces données sont sur 16 bits),

un fil d’adresse TADD (le processeur qui émet spécifie grace aux 8 bits envoyés sur TADD l’adresse de destination des données. Il peut émettre vers un ou plusieurs processeurs).

Fig. 65 : Communication entre 8 DSP.

Fig. 66 : Chronogrammes de communication

Pour chaque DSP, il faut donc spécifier le ou les canaux sur lesquels il émet, son adresse sur 8 bits (adresse qui est véhiculé par le fil TADD) et l’adresse du destinataire (fil TADD). L’adresse du destinataire peut devenir l’adresse des destinataires si l’on choisit bien la façon de coder l’adresse de chaque processeur.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 786

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved