| CATEGORII DOCUMENTE |

| Aeronautica | Comunicatii | Electronica electricitate | Merceologie | Tehnica mecanica |

CBA cu porti logice

Generalitati

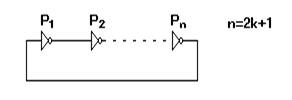

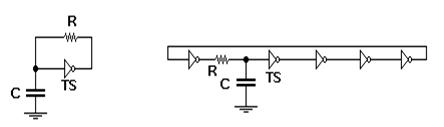

Consider un numar impar de porti NU legate in inel; se obtine un oscilator.

Presupun Tp timpul mediu de propagare prin porti; atunci perioada oscilatiilor este T=2nTp, unde n=2k+1 este numarul portilor.

Daca

Tp = 10ns T f = ![]() =

= ![]() 109

Hz

109

Hz

Daca n = 3 T f = ![]() 109

Hz = 16.6 MHz

109

Hz = 16.6 MHz

Observatii

1. Din calculul anterior se poate determina frecventa maxima a unui astfel de oscilator.

2. Frecventa depinde de timpul de propagare specific portilor. Acesta poate depinde de alimentare (circuite CMOS).

3. In general, pornind de la circuitul anterior si introducind in lant circuite de intirziere, care sa dicteze timpul de propagare prin lant, se obtin CBA cu porti.

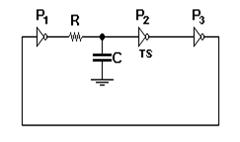

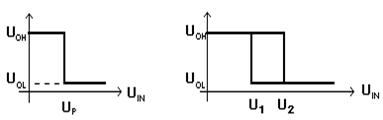

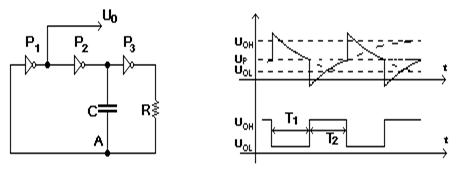

CBA cu porti logice si trigger Schmitt

Cel mai simplu circuit de intirziere este RC trece-jos. Acesta poate fi intercalat in lantul de n=2k+1 inversoare, daca primul inversor de dupa circuitul RC trece-jos este cu caracteristica de trigger Schmitt.

Vom considera varianta cu porti idealizate, adica Rin ; Ries

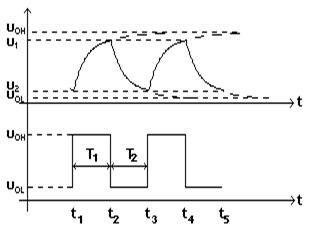

Formele de unda pentru circuitul anterior semnificative sint:

In intervalul [t1, t2], UC este mai mica decit U1, iesirea UO=1=UOH; iesirea portii P1 este UP1=1 si C se incarca prin R spre UOH. In momentul t2 UC atinge U1 si poarta TS, P2, basculeaza, basculeaza si iesirea portii P1 (UO=0) si condensatorul C se descarca prin R.

Rezulta o functionare in care tensiunea pe condensatorul C variaza exponential intre cele doua praguri ale TS.

Calculul perioadei de oscilatie decurge astfel:

- calculul lui T1

UC(0)=U2

UC )=UOH

t=RC

UC(t)=UOH+[U2-UOH]e-t/RC

UC(T1)=U1

T1 = RC ln![]()

- calculul lui T2

UC(0)=U1

UC )=UOL

t=RC

UC(t)=UOL+[U1-UOL]e-t/RC

UC(T2)=U2

T2 = RC ln![]()

Observatii

1. Se poate realiza varianta cu n=1 sau cu n=5.

Relatiile sint aceleasi daca neglijam TP

2. Varianta cu circuite CMOS

Caracteristica de transfer este ideala, Rin , dar Ries este mare si TP destul de mare. Relatiile pentru T1 si T2 sint cu precizie acceptabila, deci daca temporizarile sint mai mari ca TP (frecvente mai scazute - sub 1 MHz) si daca R>>Ries CMOS (R de la zeci de kW in sus), UOH=VDD; UOL

3. Varianta cu circuite TTL

Se tine cont de Ries TTL si Rin TTL => se recomanda R ~ 450 W (in plus intre intrarea si iesirea unei porti TTL nu se poate cupla o rezistenta prea mare). Relatiile au o precizie acceptabila daca UOH=3.9V si UOL

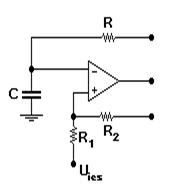

4. Varianta cu AO

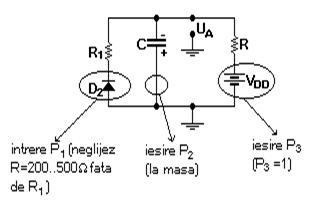

Daca se utilizeaza un TS cu AO in varianta inversoare se poate realiza un CBA cu n=2 (varianta cu o poarta) dupa schema:

Relatiile pentru T1 si T2 se pastreaza cu

In plus, de regula UOH = +VCC si UOL = -VCC

Problema: Cu un AO in montaj TS alimentat la VCC si Vref se realizeaza CBA dupa montajul de mai sus. Sa se calculeze perioada de oscilatie ca functie de RD, R1, R2, VCC

5. Varianta cu bE555

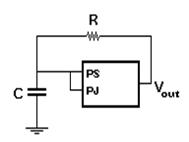

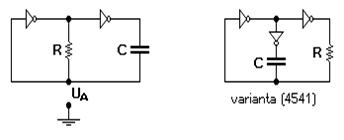

CBA cu porti logice si circuit RC (fara trigger Schmidt)

Daca in variantele cu TS facem ca cele doua praguri sa se apropie (U1 U2), atunci T1 si T2 tind la 0. Se observa ca schema cu poarta obisnuita in loc de TS nu functioneaza.

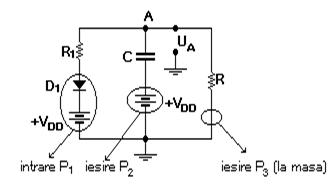

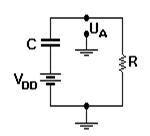

CBA cu circuit RC si porti idealizate

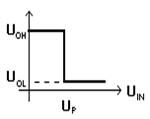

Se considera Rin , Ries=0 si caracteristica de transfer:

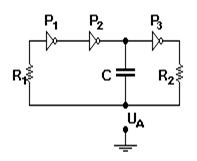

Condensatorul C nu se leaga la masa ci la nivel inversat fata de R.

Initial (intervalul T1) UA=1 => P1=0, P2=1, P3=0. Are loc o circulatie de curent: iesire P2=1, condensator C, R, iesire P3=0; iar UA scade exponential spre UOL. Cind UA atinge UP, circuitul basculeaza cu P1=1, P2=0 si P3=1; saltul in jos de la P2 se transmite prin C si la UA, deci la intrarea lui P1. Incepe incarcarea lui C pe traseul P3=1, R, C, P2=0. Tensiunea UA creste exponential spre 0 (este esential ca R si C sa fie legate la nivele logice diferite). Cind se atinge UP circuitul rebasculeaza in starea innitiala.

- calculul lui T1

UA(0)=UP+(UOH-UOL

UA )=UOL

t=RC

UA(t)=UOL+[UP+UOH-2UOL]e-t/RC

UA(T1)=UP

T1 = RC ln![]()

- calculul lui T2

UA(0)=UP-(UOH-UOL

UA )=UOH

t=RC

UA(t)=UOH+[UP+UOL-2UOH]e-t/RC

UA(T2)=UP

T2 = RC ln![]()

Observatie: Se poate porni de la varianta cu n=1. In acest caz mai trebuie o poarta pentru a se obtine nivel inversat pentru C. Functionarea si relatiile sint identice. Condensatorul C fiind legat dupa R la un nivel inversat, circuitul este cu amorsare nesigura.

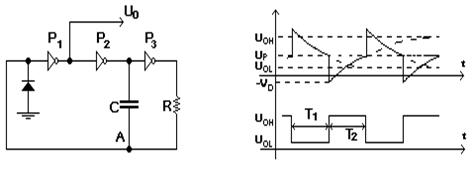

CBA cu circuit RC si porti TTL

Variantele ideale prezentate anterior se pot realiza cu porti TTL daca:

1. R este de ordinul 150 W. Pentru valori mai mari de 8 kW circuitul nu functioneaza (rezistenta mare cuplata intre doua porti TTL). Pentru valori mai mici intervine si Ries

2. Intrarea portii P este prevazuta cu dioda de taiere catre masa, deci saltul in jos este limitat la

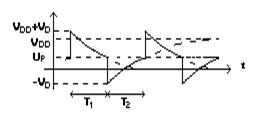

-VD. Formele de unda devin:

- T1 se calculeaza dupa aceeasi relatie (neglijez Ries si Rin deoarece R~500 W

T1

= RC ln![]()

- calculul lui T2

UA(0)=-VD

UA )=UOH

t=RC

UA(t)=UOH+[-VD-UOH]e-t/RC

UA(T2)=UP

T2 = RC ln![]()

Se aleg UOH=3.9 V; UP=1.4 V; UOL=0.1 V si VD=0.65 V. Relatiile au precizii afectate de neglijarea rezistentelor Ries si Rin

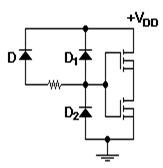

CBA cu circuit RC si porti CMOS

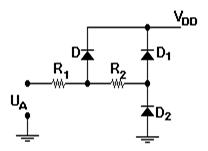

Variantele idealizate se pot realiza cu circuite CMOS daca se au in vedere modificarile:

- Rin poate fi neglijat sigur (Rin ); Ries poate fi neglijat daca se adopta R>>Ries

- influenta circuitului de protectie al portii P1 este: diodele D1 si D2 intra in functie daca UA depaseste +VDD sau masa. In consecinta salturile in sus si in jos vor fi limitate la +VDD + VD si respectiv -VDD

Observatie: Exista

circuite CMOS cu alt tip de protectie pentru intrari care admit tensiuni de

intrare mai mari ca +VDD sau mai mici ca 0 si atunci limitarea nu se mai

face la aceste nivele.

Observatie: Exista

circuite CMOS cu alt tip de protectie pentru intrari care admit tensiuni de

intrare mai mari ca +VDD sau mai mici ca 0 si atunci limitarea nu se mai

face la aceste nivele.

- la circuite CMOS, UOH = VDD , UOL ~ 0 si Up = VDD

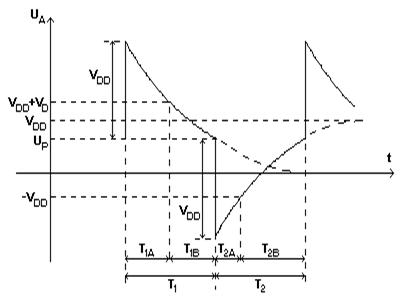

Forma de unda si calculul temporizarilor devine:

- calculul lui T2 este identic cu cel de la

TTL inlocuind VOH=VDD

- calculul lui T2 este identic cu cel de la

TTL inlocuind VOH=VDD

T1 = RC ln![]()

- calculul lui T1

UA(0)=VDD + VD

UA

t=RC

UA(t)=[VDD + VD]e-t/RC

UA(T1)=UP

T1 = RC ln![]()

Observatie: Chiar daca inlocuim UP=VDD/2, T1 si T2 ramin dependente de VDD

CBA cu circuit RC, porti CMOS si rezistenta serie de intrare

R1 intre A si P1 realizeaza:

R1 intre A si P1 realizeaza:

- protectie pentru D1 si D2din circuitul de intrare al lui P1

- reduce dependenta temporizarilor T1 si T2 de VDD

Functionarea circuitului este identica; forma de unda din A se modifica insa ca in figura:

Circuitul de intrare pentru P1 nu mai limiteaza saltul de tensiune UA. Acest salt are valoarea UOH-UOL=VDD. Se observa insa ca atit timp cit UA=VDD+VD (intervalul T1A) descarcarea condensatorului C se face atit prin R cit si prin R1 si D1 deschisa. De asemenea, in intervalul T2A, cit tensiunea UA<-VD este deschisa D2 si incarcarea lui C se realizeaza prin R dar si prin R1 si D2

- Calculul temporizarii

T1=T1A+T1B

- calculul lui T1A

Schema echivalenta este:

t=0 inceputul lui T1A

UA(0)=UP + VDD

UA )=(VDD + VD)*R/(R1+R) (la , C e intrerupt si in A am VDD+VD

divizata)

t1=(R||R1)*C

UA(t) = (VDD + VD) ![]() + [VDD + Vp -

+ [VDD + Vp -

![]()

T1A = (R||R1) C ln

T1A = (R||R1) C ln![]()

Cind UA scade sub VDD+VD, D1 se blocheaza si circuitul echivalent devine:

Descarcarea lui C se face prin R. Relatia lui T1B este identica cu cea pentru T1 de la varianta fara R1, adica:

T1B=RCln![]()

Calculul pentru T2 decurge analog:

Pentru T2A avem UA < -VD si D2 este deschisa, schema echivalenta pentru circuit fiind:

Initial C are minus spre A astfel ca incarcarea se face prin R dar si prin R1

UA(0)=UP-VDD

UA( )=-UP+R1 ![]()

![]()

t=(R||R1)C

UA(t)=![]()

![]()

UA(T2A)=- VD

T2A

= (R||R1) C ln

T2A

= (R||R1) C ln![]()

In continuare, D2 se blocheaza si circuitul echivalent ramine. Incarcarea lui C se face numai prin R. Relatia T2B este identica cu cea dedusa pentru T2 anterior, adica:

T2B=RCln![]()

Perioada de oscilatie este T=T1A+T1B+T2A+T2B, adica:

T = (R||R1) C ln![]()

+ RCln![]()

Observatie

Notam

k=![]() =>

=>

T

=(R||R1) C ln

+ RCln![]()

Daca se calculeaza lim T, atunci:

k

lim

T=RCln![]() +RCln

+RCln![]()

lim

T=RCln![]()

Relatia corespunde cu cazul idealizat particularizat pentru circuite CMOS, adica UOH=VDD si UOL=0. In plus, daca avem in vedere ca pentru circuite CMOS UP=VDD/2, atunci:

lim

T=RCln9 =RCln9=2RCln3

=RCln9=2RCln3

ceea ce inseamna ca perioada nu depinde de VDD. In practica se recomanda k=R1/R=10. Pentru o valoare mai mare ar fi necesar R1 prea mare si in acest fel R1 impreuna cu capacitatea de intrare de la P1 ar constitui un circuit R1C de intirziere care modifica relatiile de intirziere.

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2229

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2025 . All rights reserved